Fターム[4M104BB24]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | 高融点金属のシリサイド (2,215)

Fターム[4M104BB24]の下位に属するFターム

Fターム[4M104BB24]に分類される特許

81 - 100 / 250

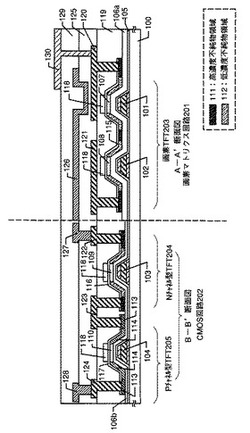

液晶表示装置及び電子機器

【課題】低比抵抗を有し、且つ上記ゲッタリング工程に十分耐えうる電極構造の必要に応じ、新規な電極構造を有する液晶表示装置を提供する。

【解決手段】絶縁表面を有する基板上に、多層構造を有するゲート電極と、前記基板、前記ゲート電極の上面および側面を覆う保護膜と、前記保護膜を覆って形成されたゲート絶縁膜と、前記ゲート絶縁膜上に接して、ソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域の間に形成されたチャネル形成領域と、を有する半導体素子からなる半導体回路を備える。保護膜は、高温処理を施した場合、基板からの不純物の拡散を抑えることができ、基板の不純物濃度に左右されることなく、良好なTFT特性を得ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル及びpチャネルのゲート構造が異なり且つメタルゲート電極を有する半導体装置において、ゲート電極パターン形成時のドライエッチングでゲート絶縁膜の突き抜けが発生しないようにする。

【解決手段】ゲート絶縁膜105と接する第2ゲート電極材料膜(TiN膜)111がゲート電極151の一部として形成されないnチャネル領域103上に、第2ゲート電極材料膜(TiN膜)111のエッチング時にオーバーエッチング吸収層として機能する第1ゲート電極材料膜(ポリシリコン膜)107を予め形成しておく。

(もっと読む)

半導体装置の製造方法

【課題】pMOSFETとnMOSFETとの間で異なる所望のしきい値を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】第1のゲート電極層上および第2のゲート電極層上に、第1の金属含有層9を形成し、この第1の金属含有層上方に感光性有機膜を含む膜10を形成し、第1のゲート電極層上方に位置する感光性有機膜を含む膜を選択的に除去することにより、第1の金属含有層のうち第1のゲート電極層上方に位置する部分を露出させ、感光性有機膜を含む膜上および第1の金属含有層上に第2の金属含有層19を形成し、加熱処理により、第1の金属含有層および第2の金属含有層に含有された金属と第2のゲート電極層とを反応させて、第2のゲート電極層を合金化するとともに、加熱処理により、第1の金属含有層に含有された金属と第2のゲート電極層とを反応させて、第2のゲート電極層を合金化する。

(もっと読む)

半導体装置およびその製造方法

【課題】nウエル及びpウエルに形成されたpMOS及びnMOSトランジスタのしきい値を精密に制御し、かつ製造容易にする。

【解決手段】nウエル2及びpウエル3上にゲート絶縁膜5を形成し、nウエル2上のゲート絶縁膜5上にpMOSトランジスタ11のしきい値制御用の第1金属膜6を、pウエル3上のゲート絶縁膜5上に第1金属膜6と異なる材料からなるnMOSトランジスタ12のしきい値制御用の第2金属膜7を形成する。そして、第1金属膜6上に高融点金属シリサイドからなる第1ゲート電極8pを、第2金属膜7上に高融点金属シリサイドからなる第2ゲート電極8nを形成する。しきい値は金属膜6、7で定まるから安定する。この金属膜6は薄く、容易にパターニングできる。

(もっと読む)

high−K誘電膜上に金属ゲートを蒸着する方法及び、high−K誘電膜と金属ゲートとの界面を向上させる方法、並びに、基板処理システム

【課題】金属酸化膜半導体電界効果トランジスタ(MOSFET)において、本発明の目的は、high−K誘電膜と金属ゲートとの間の界面特性を向上させることにより、電気的特性およびデバイス性能を向上させることである。

【解決手段】high−K誘電体上に金属ゲートを蒸着することによりMOSFETの製造においてhigh−K誘電膜と金属ゲートとの間の界面を向上させる方法は、熱アニーリングモジュール内で、その上にhigh−K誘電膜が蒸着された基板をアニールするアニーリングステップと、金属ゲート蒸着モジュール内で、前記アニールされた基板上に金属ゲート材料を蒸着させる蒸着ステップとを含み、真空を破ることなく、前記アニーリングステップおよび前記蒸着ステップが連続的に行なわれることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】不純物の注入量及びチャネル領域中の不純物濃度を容易に制御する。動作特性に優れたFin型電界効果型トランジスタを備えた半導体装置を提供する。

【解決手段】Fin状の半導体基板の部分に犠牲酸化膜を形成した後、マスクパターンをマスクに用いて半導体基板に不純物を注入する。この後、犠牲酸化膜を除去して、半導体基板を露出させた後、露出した半導体基板上にゲート絶縁膜を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】仕事関数が所望の値に制御されたメタルゲート電極を備える半導体装置を提供する。

【解決手段】半導体基板2上に、ゲート絶縁膜4を介して、N等を含有する仕事関数制御層5、SiまたはAlを含んだ中間層6、およびMoN層等の低抵抗層7が積層された構造を有するメタルゲート電極を形成する。その形成時には、ゲート絶縁膜4上に仕事関数制御層5、中間層6および低抵抗層7の各層の積層後、ゲート加工を行い、LDD領域9、サイドウォール8およびソース・ドレイン領域10を順に形成して、半導体基板2に導入した不純物の活性化アニールを行う。仕事関数制御層5と低抵抗層7との間に中間層6を設けたことにより、仕事関数制御層5へのあるいは仕事関数制御層5からのN等の拡散が抑制され、その仕事関数の変動が抑制されるようになる。

(もっと読む)

半導体装置及びその製造方法

【課題】高濃度拡散層の上部にシリサイド膜を有する半導体装置において、リーク電流の発生を防止する。

【解決手段】第1のMOSトランジスタは、活性領域300xにおける第1のサイドウォールスペーサ305aの外側方下に形成された第1の高濃度拡散層306aと、第1の高濃度拡散層306aの上部に形成された第1のシリサイド膜311aとを備え、第2のMOSトランジスタは、活性領域300xにおける第2のサイドウォールスペーサ305bの外側方下に形成された第2の高濃度拡散層306bと、第2の高濃度拡散層306bの上部に形成された第2のシリサイド膜311bとを備え、第1のシリサイド膜311a及び第2のシリサイド膜311bを構成する結晶粒の結晶粒径は、第1のサイドウォールスペーサ305aと第2のサイドウォールスペーサ305b間の間隔以下である。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置を高集積化および高性能化することのできる技術を提供する。

【解決手段】SOI−MISFETは、SOI層3と、SOI層3上にゲート絶縁膜15を介して設けられたゲート電極35aと、ゲート電極35aの両側壁側のSOI層3上に、SOI層3からの高さがゲート電極35aよりも高く設けられ、ソース・ドレインを構成する積上げ層24とを有している。また、バルク−MISFETは、シリコン基板1上にゲート絶縁膜15より厚いゲート絶縁膜16を介して設けられたゲート電極35bと、ゲート電極35bの両側壁側の半導体基板1上に設けられたソース・ドレインを構成する積上げ層25とを有している。ここで、積上げ層24の厚さが、積上げ層25の厚さよりも厚く、ゲート電極35a、35bの全体、SOI−MISFETのソース・ドレインの一部、およびバルク−MISFETのソース・ドレインの一部がシリサイド化されている。

(もっと読む)

半導体装置の製造方法

【課題】p−MISトランジスタとn−MISトランジスタとのゲート電極形状のばらつきが少ない半導体装置の製造方法を提供する。

【解決手段】第1および第2領域13、14にゲート絶縁膜17を介して第1金属を含む第1金属膜18を形成する工程と、第1領域13における第1金属膜18を保護膜で被覆し、第2領域14における第1金属膜18を除去してゲート絶縁膜17を露出させる工程と、第1金属膜18上およびゲート絶縁膜17上に第1金属と異なる第2金属を含む第2金属膜19を形成する工程と、ゲート電極パターンを有するマスク材を用いて第2金属膜19を異方性エッチングし、第2領域14に第2ゲート電極を形成する工程と、第1金属膜18および第2金属膜19の露出部に酸化処理を施す工程と、第1領域13における第1金属膜18を異方性エッチングし、第1領域13に第1ゲート電極を形成する工程とを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】移動度の低下を極力抑えつつゲートリーク電流が低い良好なゲート絶縁膜を有するMOSFETを含む半導体装置、及びその製造方法を提供する。

【解決手段】半導体層と、ゲート電極と、膜厚が1nm以上で少なくとも半導体層側からその厚み方向に1nmまでの領域は窒化酸化シリコン膜(SiON)から構成され、かつシリコンと酸素の原子数比(O/Si)が0.01〜0.30、シリコンと窒素の原子数比(N/Si)が0.05〜0.30であるゲート絶縁膜と、ソース/ドレイン領域と、を備えたMOSFETを有する半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】 本発明は、金属元素を有する絶縁膜の界面特性を向上させる半導体装置の製造方法を提供することを目的とする。

【解決手段】 本発明の半導体装置の製造方法は、下層、Ge層、Ge酸化物層、上層の順に積層された構造を形成する工程と、熱処理を用いてGe酸化物層及びGe層を除去して、上層と下層とを直接接合させる工程とを有し、上層及び下層の何れかは金属元素を有する絶縁物で形成されることを特徴とする。

(もっと読む)

マイクロデバイス用基板及びその製造方法並びにマイクロデバイス及びその製造方法

【課題】微細径で且つ高アスペクト比の貫通配線を有するマイクロデバイス用基板及びその製造方法並びにマイクロデバイス及びその製造方法を提供する。

【解決手段】基板本体31と、この基板本体31を厚さ方向に貫通する貫通孔32と、この貫通孔32内に埋め込まれ且つIV族元素と該IV族元素との化合物を形成する金属との化合物を含む貫通配線37とを具備することを特徴とするマイクロデバイス用基板にある。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート形成溝内に埋め込んで形成される金属系ゲート電極を有するトランジスタ群と抵抗とを有する半導体装置で、抵抗値のばらつきをなくした抵抗形成を可能とする。

【解決手段】半導体基板11に、第1トランジスタ群と、これよりも低い動作電圧の第2トランジスタ群と、抵抗3とを備え、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13を介してシリコン系材料層71で形成された第1ゲート電極15を有し、第2トランジスタ群は、半導体基板11上の第1層間絶縁膜38に形成したゲート形成溝42内に第2ゲート絶縁膜43を介して金属系ゲート材料を埋め込むように形成された第2ゲート電極47、48を有し、抵抗3は、半導体基板11上に絶縁膜61を介してシリコン系材料層71と同一層で形成された抵抗本体部62と、この上部に形成された抵抗保護層63を有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】異なる動作電圧のトランジスタ群を同一半導体基板に形成し、高電圧動作のトランジスタ群のゲート電極の低抵抗化を可能にし、低動作電圧のトランジスタ群の金属ゲート電極を形成するための導電膜の残査発生をなくすことを可能にする。

【解決手段】半導体基板11に、高動作電圧の第1トランジスタ群と、低動作電圧の第2トランジスタ群とを有し、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13、第1ゲート電極15、シリサイド層とが順に積層され、第2トランジスタ群は、半導体基板11上のダミーゲート18を除去してなるゲート形成溝42内に、第2ゲート絶縁膜と第2ゲート電極を有する半導体装置の製造方法において、第1ゲート電極15をダミーゲート電極16よりも低く形成してから上記シリサイド層を形成し、それらを被覆する層間絶縁膜を形成して表面を平坦化してから、ゲート形成溝を形成する。

(もっと読む)

デュアル仕事関数半導体デバイス

【課題】CMOSがFUSIゲートを含む場合、異なるシリサイド相を有する第1および第2の制御電極が形成され、ゲート形成後の熱工程等により各ゲートの異なったシリサイド相中のNi等の金属はゲート電極間を拡散しない半導体装置を提供する。

【解決手段】第1の制御電極17の金属半導体化合物から、第2の制御電極18の金属半導体化合物に、金属が拡散するのを防止するブロック領域23を形成する。ブロック領域23は、第1および第2の制御電極17、18の間の境界面に形成され、金属半導体化合物がそれから形成される金属中での溶解度より、金属半導体化合物中での溶解度が低いドーパント元素を注入することにより形成する。これにより、金属拡散が防止され、第1および第2の制御電極17、18の金属半導体化合物の構成が、例えば更なるデバイスの処理中の熱工程中に、実質的に変化せずに保たれる。

(もっと読む)

半導体装置及びその製造方法

【課題】微細ショットキーMISFETのソース電極がチャネル端の表面ポテンシャルをピニングすることで発生するトランジスタ性能の劣化を防止する。

【解決手段】ショットキーMISFETを構成する、半導体基板上に形成したソース金属電極8と半導体基板中のチャネル領域11との接触で形成されるショットキー障壁高さとφB0、半導体基板のバンドギャップEGと、半導体基板の真性キャリア濃度niと、デバイスの動作温度Tと、ボルツマン係数kに対して、少なくともソース電極と接するチャネル端近傍の不純物濃度NCHを、NCH≦ni・exp((qφB0−0.5EG)/kT)の条件を満たすようにする。

(もっと読む)

金属ゲート及び高K誘電体を有する回路構造体

【課題】 高k材料含有ゲート誘電体及び金属含有ゲートを有する回路構造体を提供する。

【解決手段】 高k誘電体のゲート絶縁体及び金属含有ゲートを有するPFETデバイス及びNFETデバイスを備えたFETデバイス構造体が、開示される。両方のNFETデバイス及びPFETデバイスにおけるゲート金属層が、単一の共通の金属層から製造された。単一の共通の金属であるために、デバイスの製造が簡単化され、必要とされるマスクの数が減少する。両方の型のデバイスのゲートのために単一の金属層を用いるさらなる結果として、PFET及びNFETの端子電極を、直接物理的に接触した状態で互いに付き合わせることができる。共通の金属材料を選択すること及び高k誘電体の酸素曝露によって、デバイスの閾値電圧が調整される。閾値は、低消費電力のデバイス動作を目的としている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】Pチャネル型トランジスタの閾値電圧を制御することができる半導体装置、およびその半導体装置の製造方法を提供する。

【解決手段】NTrとPTrとを含む半導体装置において、N型チャネル形成領域とP型チャネル形成領域とを有するN型半導体基板2上に絶縁膜Fが形成され、絶縁膜Fにゲート電極用溝A及びBとが形成され、ゲート電極用溝A及びBの内側表面上にゲート絶縁膜20が形成され、NTr領域におけるゲート絶縁膜20上にNTr仕事関数制御メタル膜21が形成され、NTr仕事関数制御メタル膜21及びゲート絶縁膜20上にフッ素がドープされたPTr仕事関数制御メタル膜23が形成され、PTr仕事関数制御メタル膜23の上層に、ゲート電極用溝に埋め込まれてゲート電極が形成されている構成とする。

(もっと読む)

半導体装置およびその製造方法

【課題】しきい値電圧が低く、トランジスタ間でしきい値電圧のばらつきの無いトランジスタを含む半導体装置を提供する。

【解決手段】nチャネルトランジスタとpチャネルトランジスタとを含む相補型の半導体装置において、nチャネルトランジスタは、ゲート絶縁膜と、ゲート絶縁膜上に形成された、第1金属(M1)とシリコン(Si)からなる第1化合物層を含む第1メタルゲート電極を備え、pチャネルトランジスタは、ゲート絶縁膜と、ゲート絶縁膜上に形成された、第1金属(M1)と第2金属(M2)とシリコン(Si)からなる第2化合物層を含む第2メタルゲート電極を備え、第1化合物層の組成が、組成式:M1Six(1≦x)で表され、第2化合物層の組成が、組成式:M1M2Siy(0<y≦0.5)で表される。

(もっと読む)

81 - 100 / 250

[ Back to top ]