Fターム[4M104BB31]の内容

Fターム[4M104BB31]に分類される特許

201 - 220 / 259

半導体装置

【課題】自己整合的に半導体層に不純物元素をドーピングしてLDD領域を形成することが可能な半導体装置の構成を提供する。

【解決手段】絶縁表面上に形成された半導体層と、半導体層上に形成された絶縁膜と、絶縁膜上に形成されたゲート電極とを含む半導体装置であって、ゲート電極は、テーパー形状を有し、半導体層は、チャネル形成領域と、第1の不純物領域と、前記第1の不純物領域よりも不純物濃度の低い第2の不純物領域とを有し、半導体層の端部は、ゲート電極と半導体層との間に設けられた絶縁膜に覆われており、記絶縁膜のうちゲート電極近傍は、テーパー形状を有することにより、自己整合的に半導体層に不純物元素をドーピングしてLDD領域を形成することが可能な構成を提供する。

(もっと読む)

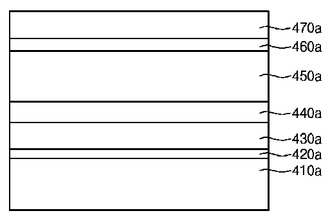

複数の金属層を積層した半導体素子

【課題】CET特性及び絶縁特性を向上させた半導体素子を提供する。

【解決手段】基板110と、基板110上に積層され、高誘電体物質から形成されるゲート酸化膜120と、ゲート酸化膜120上に積層され、ゲート酸化膜120と同種金属の窒化物から形成される第1金属層131と、第1金属層131上に積層される第2金属層132と、第2金属層132上に積層される第3金属層133と、第3金属層133上に積層され、第1金属層131〜第3金属層133と共にゲート電極を形成する物質層140と、を含んでいる。これにより、半導体素子のゲート酸化膜と金属層間の化学的な反応により発生するCET特性の低下および電流の漏れなどを防止することで半導体素子の絶縁特性を向上させることができる。

(もっと読む)

半導体装置の製造方法

【課題】P型MOSFETの閾値のバラつきを抑制して高品質の半導体装置を形成することができ、また、製品開発のコストを抑制することができる半導体装置の製造方法を提供する。

【解決手段】シリコン基板上100にゲート絶縁膜102を形成する第1の工程と、ゲート絶縁膜102上に、ゲート電極104を構成する導電体膜103を、有機材料を用いた形成法によって形成する第2の工程と、導電体膜103が形成されたシリコン基板100を、酸化性雰囲気である水蒸気と、還元性雰囲気である水素との混合雰囲気中で加熱する第3の工程と、を備えた半導体装置の製造方法であって、第3の工程における水蒸気に対する水素の分圧比が、炭素が酸化され、かつ、導電体膜104を構成する金属材料が還元される分圧であることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】膜質が向上したゲート絶縁層を有するMISトランジスタを含む、半導体装置を提供する。

【解決手段】本発明にかかる半導体装置は、半導体層10と、半導体層の上方に設けられたゲート絶縁層20と、ゲート絶縁層の上方に設けられたゲート電極22と、半導体層に設けられたソース領域およびドレイン領域26と、を含み、ゲート絶縁層は、シリコンと、窒素と、重水素とを含有する第1の層20aを含む。

(もっと読む)

薄膜トランジスタ装置およびその製造方法、ならびに、該薄膜トランジスタ装置を備えた表示装置

【課題】 TFTの層間絶縁膜の下層にあって膜厚が薄いポリシリコン膜からなるソース領域やドレイン領域に到達するコンタクトホールを開口する際に、ポリシリコン膜を突き抜けてしまうとコンタクトホール底部にポリシリコン膜が残存しないため、接続抵抗が増大してしまう。また、保持容量の下部電極がポリシリコン膜からなる場合、該膜を低抵抗化するために高ドーズのドーピングプロセスが必要であるため、生産性を著しく低下させていた。

【解決手段】 基板1上で島状に形成されたポリシリコン膜3におけるソース領域3aおよびドレイン領域3bの少なくとも一部を覆う金属膜4を形成してから、ゲート絶縁膜5、ゲート電極6、層間絶縁膜7を形成し、金属膜4の上部にコンタクトホール8を開口する。さらに、金属膜4を形成する際に、保持容量の位置まで延在させることにより、金属膜4を保持容量の下部電極となす。

(もっと読む)

CMOS半導体素子とその製造方法

【課題】窒素含有量の異なる金属をゲート電極材として用いたCMOSトランジスタにおいて、ゲート電極の抵抗を低減しCMOSトランジスタの微細化を実現する。

【解決手段】半導体基板上のNMOS領域とPMOS領域にゲート絶縁膜を介してそれぞれ窒素含有量の異なる下層金属層とその上に積層された上層金属層から成る2層構成のゲート電極が形成されたCMOS半導体素子であって、前記下層金属層を前記上層金属層よりゲート長方向の長さを短くする。

(もっと読む)

半導体装置のデュアルゲート構造物及びその形成方法

【課題】高誘電膜を含むCMOSトランジスタの形成に適合した構造を有するデュアルゲート構造物及びその形成方法を提供する。

【解決手段】デュアルゲート構造物は、第1及び第2領域が区分される基板と、前記第1領域の基板上に形成され、金属酸化膜、第1仕事関数を有する金属物質からなる第1金属パターン、シリコン拡散防止膜パターン、及びシリコンを含む導電膜パターンが積層された第1ゲート構造物と、前記第2領域の基板上に形成され、金属酸化膜、前記金属物質及びシリコン元素を含み前記第1仕事関数より低い第2仕事関数を有する第2金属パターン、及び前記シリコンを含む導電膜パターンが積層された第2ゲート構造物と、を含む。前記デュアルゲート構造物は各領域に形成されるゲート電極が同一の金属物質からなるので前記金属物質の一部を除去しなくてもよいので前記除去工程の際発生する金属酸化膜の損傷を防止することができる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】基板上にトランジスタ等の半導体素子とセンサーとを作り込んで設ける場合に、同一工程で作製することにより得られる半導体装置およびその作製方法を提供することを目的とする。

【解決手段】同一基板上に、互いに接する第1の領域および第2の領域を有する第1の半導体膜と、チャネル領域とソースまたはドレイン領域として機能する第3の領域とを有する第2の半導体膜と、第1の半導体膜および第2の半導体膜を覆って設けられた絶縁膜と、絶縁膜上に設けられ且つ第1の領域と電気的に接続する第1の導電膜と、第2の領域と電気的に接続する第2の導電膜とを設け、第1の領域、第2の領域および第3の領域に不純物元素を第1の領域と第2の領域に含まれる不純物元素の濃度が異なるように導入する。

(もっと読む)

半導体装置及びその製造方法

【課題】高輝度の半導体装置およびその製造方法を提供することにある。【解決手段】絶縁性の成長基板上に形成された第1型の窒化物系クラッド層と、前記第1型の窒化物系クラッド層上に形成された多重量子井戸窒化物系活性層及び前記多重量子井戸窒化物系活性層上に形成された前記第1型と異なる第2型の窒化物系クラッド層と、を含む半導体装置が提供される。前記第1型の窒化物系クラッド層の下部及び前記第2型の窒化物系クラッド層の上部のうち、少なくとも一つには、トンネルジャンクション層が形成される。  (もっと読む)

(もっと読む)

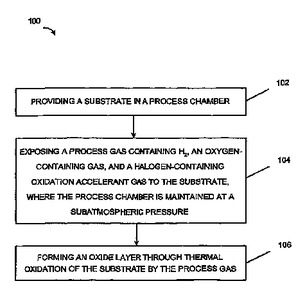

酸化膜の形成方法

基板上に酸化膜を形成する方法。当該方法は、H2、酸素含有ガス、ハロゲンを含有した酸化を促進するガスを含むプロセスガスを大気圧より低い圧力に維持して基板に曝露する工程、並びに、前記プロセスガスによる基板の熱酸化を介して酸化膜を形成する工程を有する。本発明の一の実施例によると、基板は約150℃から約900℃に維持されて良い。酸化膜を含む微細構造について記載されている。前記酸化膜は、高誘電率誘電体層と共に集積されたゲート誘電体酸化膜又は界面酸化膜であって良い。  (もっと読む)

(もっと読む)

半導体デバイスおよびCMOSデバイス

【課題】NMOSとPMOSのショットキー障壁を低くするCMOSデバイスを提供する。

【解決手段】半導体デバイスは基板を備え、当該基板は第1の領域と第2の領域とを有し、第1の領域は、{i,j,k}から成るミラー指数群により表される第1の結晶方位を有すると共に、前記第2の領域は、{l,m,n}から成るミラー指数群により表される第2の結晶方位を有し、l2+m2+n2>i2+j2+k2である。別な実施例では、第1領域に形成されるNMOSFETと、この第2の領域に形成されるPMOSFETと、をさらに備える。各実施例では、NMOSFETとPMOSFETの内の少なくとも一つで形成されるシットキー接触部をさらに備えている。

(もっと読む)

半導体構造

【課題】 金属ゲート電極層に望まれる特性は、微細加工を施された半導体立体構造体上に段差被覆率良く被覆されていることである。またもう一つの特性は、堆積された電極層の表面が1ナノメートルのスケールで平坦であり、電極層の堆積後に特別な平坦化処理を施すことなく電気的な絶縁を目的とした誘電体層を被服することが可能なことである。また、金属ゲート電極層に望まれる更なる特性の一つは、通常の半導体プロセスと同様のエッチング加工性を有していることである。また、金属ゲート電極層に望まれるもうひとつの特性は、結晶粒界がなく均一であり、不純物拡散が抑制された構造であることである。

【解決手段】 上記特性を満たす最良の金属ゲート電極としてアモルファス構造の金属電極が優れていることを見出し、本発明に至った。

(もっと読む)

半導体装置およびその製造方法

【課題】 1.5以上の高アスペクト比である微細ホールに対しても、金属配線膜を埋め込むことができるように、ホールへの金属配線膜の埋め込み性を従来よりも向上させる。

【解決手段】 TiN膜の成膜工程63で、スパッタにより、ホールの内壁に沿ってTiN膜を成膜する。このとき、成膜温度を、従来よりも低温の150℃とすることで、アモルファス構造のTiN膜を形成する。その後、スパッタ工程64、65で、アモルファス構造のTiN膜の表面上にAl合金膜を形成することで、TiN膜を下地とした状態で、Al合金膜をコンタクトホールの内部に埋め込む。このように、Al合金膜の下地となるTiN膜をアモルファス構造にすることで、TiN膜の表面エネルギーを大きくし、TiN膜のAl合金膜に対する濡れ性を従来よりも向上させることができ、ホールへのAl合金膜の埋め込み性を従来よりも向上させることができる。

(もっと読む)

ハイブリッドPVD−CVDシステム

【課題】1つ又は複数のシリコン含有層及び1つ又は複数の金属含有層を含む積層膜を製造する方法及び基板上に積層膜を形成するための基板処理システムを提供する。

【解決手段】基板処理システムは、1つ又は複数のロードロックチャンバに接続された1つ又は複数の搬送ポット及び2つ以上の異なるタイプの処理チャンバを含む。2つ以上のタイプの処理チャンバは、真空を破ることなく、基板処理システムから基板を取り出して、同一の基板処理システムで1つ又は複数のシリコン含有層及び1つ又は複数の金属含有層を蒸着するために使用され、表面汚染、酸化などを防ぎ、別の洗浄や表面処理ステップを排除することができる。基板処理システムは、その場の基板処理のための高処理能力及びコンパクトな専有面積を提供し、かつ異なるタイプの処理を行うように構成されている。

(もっと読む)

半導体装置の作製方法

【課題】 本発明は、TFTを用いる表示装置及びデータを無線で送受信する機能を持った半導体装置の製造工程においてフォトリソグラフィ工程の回数を削減することを目的とする。また、より簡略化された製造工程で、電気的特性の高いTFT、表示装置及びデータを無線で送受信する機能を持った半導体装置等に代表される電子機器を作製する。低いコストで歩留まり良く製造することができる技術を提供することを目的とする。

【解決手段】 基板上に塗れ性が低い層と、塗れ性が低い層に比べて塗れ性が高い領域を形成し、塗れ性が高い領域上に導電性粒子を有する組成物を塗布と焼成を繰り返して凸状の導電層を形成することを特徴とする。

(もっと読む)

MOS構造を有する半導体装置およびその製造方法

【課題】製造プロセスを煩雑にすることなく、閾値が異なるMOS構造のそれぞれのゲート電極に適した材料を採用して閾値を適切に制御でき、かつゲート電極からチャネル領域への拡散を顕著としない技術を提供する。

【解決手段】PMOSトランジスタQPはゲート電極GP及びこれとゲート絶縁膜5を介して対峙するN型ウェル31を、NMOSトランジスタQNはゲート電極GN及びこれとゲート絶縁膜5を介して対峙するP型ウェル32を、それぞれ有している。ゲート電極GNは多結晶シリコン層63で構成される一方、ゲート電極GPは金属層64/多結晶シリコン層63の積層構造を備えている。

(もっと読む)

MOS構造を有する半導体装置およびその製造方法

【課題】製造プロセスを煩雑にすることなく、閾値が異なるMOS構造のそれぞれのゲート電極に適した材料を採用して閾値を適切に制御でき、かつゲート電極からチャネル領域への拡散を顕著としない技術を提供する。

【解決手段】PMOSトランジスタQPはゲート電極GP及びこれとゲート絶縁膜5を介して対峙するN型ウェル31を、NMOSトランジスタQNはゲート電極GN及びこれとゲート絶縁膜5を介して対峙するP型ウェル32を、それぞれ有している。ゲート電極GNは金属層642/多結晶シリコン層63で構成される一方、ゲート電極GPは金属層641/多結晶シリコン層63の積層構造を備えている。金属層642は金属層641よりも薄い。

(もっと読む)

MOS構造を有する半導体装置及びその製造方法

【課題】製造プロセスを煩雑にすることなく、閾値が異なるMOS構造のそれぞれのゲート電極に適した材料を採用して閾値を適切に制御でき、かつゲート電極からチャネル領域への拡散を顕著としない技術を提供する。

【解決手段】PMOSトランジスタQPはゲート電極GP及びこれとゲート絶縁膜5を介して対峙するN型ウェル31を、NMOSトランジスタQNはゲート電極GN及びこれとゲート絶縁膜5を介して対峙するP型ウェル32を、それぞれ有している。ゲート電極GNはシリサイド層65で構成される一方、ゲート電極GPは金属層64/シリサイド層65の積層構造を備えている。

(もっと読む)

埋め込みゲートを有する半導体装置及びその製造方法

【課題】埋め込みゲートトランジスタの短チャネル効果の低減とゲートとの重なり増加とが両立できる半導体装置、およびその製造方法を提供すること。

【解決手段】本発明の半導体装置202は、基板102上に、第1領域104、第2領域106、及び分離領域108に形成された凹部118と、上記凹部118を均一な厚さで裏打ちする誘電体層120とを備えた半導体装置。この製造方法は、基板102における第1領域104と第2領域106との間に分離領域108を形成する工程と、基板表面に凹部118を形成する工程と、酸化物120で凹部118を均一に覆う工程とを含む。さらに、凹部118底面下に配されたチャンネル領域124をドープする工程と、凹部118にゲート電極材料126を堆積する工程とソース/ドレイン領域を形成する工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】動作性能および信頼性の高い回路を備えた半導体装置を提供することを課題とする。そして、半導装置の信頼性を向上させることにより、それを備える電子機器の信頼性を向上させることを課題とする。

【解決手段】連続発振レーザ若しくは10MHz以上の周波数で発振するレーザビームを照射しながら一方向に走査して半導体膜を結晶化若しくは再結晶化させる工程と、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用いて形成するフォトリソグラフィー工程と、低電子温度で高電子密度のプラズマを利用した、半導体膜、絶縁膜若しくは導電膜表面の酸化処理、窒化処理若しくは表面改質処理を行う工程とを組み合わせることで上記課題を解決する。

(もっと読む)

201 - 220 / 259

[ Back to top ]