Fターム[4M104BB31]の内容

Fターム[4M104BB31]に分類される特許

161 - 180 / 259

半導体装置およびその製造方法

【課題】従来のCMISデバイスにおいては、価電子帯端近くの高い仕事関数を有する金属は、還元雰囲気アニール後に実効仕事関数が低下する。

【解決手段】半導体装置は、ソースとドレイン間のN型半導体層上に形成された金属元素を含むゲート絶縁膜と、ゲート絶縁膜上に形成され、膜厚が3nm以下であるカーボン層と、カーボン層上に形成されたゲート電極とを有し、ゲート電極/ゲート絶縁膜界面へのカーボン層による仕事関数の上昇効果により、還元雰囲気アニール耐性のない価電子帯端近くの高い仕事関数を有する金属を用いずとも、PMISFETに必要な実効仕事関数を得ることができ、低い閾値電圧を実現する。

(もっと読む)

半導体装置

【課題】信頼性の向上した半導体装置及びその作製方法を提供する。

【解決手段】ゲート電極と重畳し、該重畳領域の外側に不純物領域が形成された半導体層と、半導体層のゲート電極が設けられた側と同じ側の面に設けられ、不純物領域と一部が接する第1導電層と、ゲート電極及び第1導電層の上に設けられた絶縁層と、該絶縁層に形成され、第1導電層と少なくとも一部が重畳する開口を介して第1導電層と接する第2導電層と、を有する。

(もっと読む)

無線システム、並びに半導体装置及び通信装置

【課題】半導体装置は、高温、低温、高湿度などの劣悪な環境下で使用される他、機械的ストレスが加わる部位に貼付して使用されることもある。したがって、半導体装置を用いたシステムの信頼性を向上するためには、半導体装置には非常に高度な耐久性が要求される。しかしながら、半導体装置には、安価に提供することも求められるため、耐久性を向上する目的で、高価なプロセスを用いることはできない。

【解決手段】同一の機能を有する複数の機能回路を有する半導体装置と、通信装置と、から構成し、半導体装置は各々の機能回路における処理結果を各々異なる周波数の副搬送波を用いて変調して送信し、通信装置は受信した各々の機能回路における処理結果から多数決により正常な応答を抽出する。このようにすることで、信頼性の高い無線システムを安価に提供することができる。

(もっと読む)

MIS型半導体装置の製造方法およびMIS型半導体装置

【課題】微細化してもリーク電流の少ない、信頼性に優れたフルシリサイド化ゲート電極を備えたMIS型半導体装置の製造方法を提供することにある。

【解決手段】シリコン基板1上に、ゲート絶縁膜4及び多結晶シリコン膜5からなるゲート領域を形成した後、プラズマ窒化処理を行って、多結晶シリコン膜5の側面に窒素を導入する。その後、ゲート領域をマスクに、シリコン基板表面にソース、ドレイン領域10、11を形成した後、多結晶シリコン膜5上に金属膜14、17を形成し、然る後、多結晶シリコン膜5と金属膜14、17とをシリサイド化反応させて、多結晶シリコン膜5の全領域がフルシリサイド化されてなるゲート電極15、18を形成する。

(もっと読む)

CMOS半導体素子及びその製造方法

【課題】デュアルメタルゲートCMOS半導体素子を提供する。

【解決手段】金属窒化物層及び多結晶シリコンキャッピング層を備え、nMOS領域及びpMOS領域の金属窒化物層は同種物質で形成され、相異なる不純物含有量により相異なる仕事関数を持つデュアルメタルゲートCMOS半導体素子。同種の金属窒化物層によりメタルゲートを形成するので、工程が単純化して収率が向上すると共に、高性能のCMOS半導体素子を得ることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板とは格子定数の異なる半導体層からチャネル部に対して効果的に応力を印加することが可能でこれによりキャリア移動度の向上を図り高機能化の達成が可能な半導体装置を提供する。

【解決手段】半導体基板3上にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇において半導体基板3の表面を掘り下げた部分にエピタキシャル成長によって形成された半導体層(応力印加層)9とを備えた半導体装置1において、半導体層9は、半導体基板3とは格子定数の異なる層であり、ゲート絶縁膜5およびゲート電極7は、半導体層9間において半導体基板3の表面を掘り下げた部分を埋め込む状態で設けられている。半導体基板3の表面に対するゲート絶縁膜5の深さ位置d2は、半導体層9の深さ位置d1よりも浅いこととする。

(もっと読む)

半導体装置

【課題】無線信号により物理的位置を検出する機能を有する半導体装置において、電源電圧を電池から供給するアクティブ型では、定期的な電池交換、電池の物理的形状、質量に関する制約により、半導体装置の物理的形状、質量などが制限される。

【解決手段】半導体装置に、無線信号から電源電圧を生成する機能を有する電源回路と、無線信号から生成された電圧をA/D変換することで無線信号の強度を検出する機能を有するA/D変換回路と、を搭載する。このようにすることで、電池交換の必要が無く、物理的形状及び質量の制約が少ない、物理的位置を検出する機能を有する半導体装置を提供することができる。また、半導体装置をプラスチック基板上に形成した薄膜トランジスタで構成することで、物理的柔軟性を有し、軽量な、物理的位置を検出する機能を有する半導体装置を安価に提供することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】シリサイド層への不純物拡散を抑制し、シリコン層中に不純物を十分行き渡ることのできる半導体装置、及びその製造方法を提供する。

【解決手段】半導体基板上に、ゲート酸化膜を介して形成されたゲート電極を備える半導体装置において、前記ゲート電極は、前記ゲート酸化膜に接して形成されたシリコン層と、前記シリコン層上に積層された金属を含有する金属含有層と、を有し、前記シリコン層は、前記ゲート酸化膜側に設けられ、第1導電型の不純物がドープされている第1シリコン層と、前記第1シリコン層上に積層され、前記第1導電型の不純物がドープされていない第2シリコン層と、を有すること。

(もっと読む)

半導体装置

【課題】通信距離が極端に短い場合でも半導体装置が正常に動作し、かつ、大きい電力が供給された場合に半導体装置の回路の動作に必要ない電力を蓄電する半導体装置を提供することを課題とする。

【解決手段】アンテナと、アンテナと接続された第1のAC/DC変換回路と、アンテナとスイッチ素子を介して接続された第2のAC/DC変換回路と、第1のAC/DC変換回路から出力される電圧の値に応じてスイッチ素子の動作を制御する検出回路と、第2のAC/DC変換回路を介して、アンテナから供給される電力を蓄電するバッテリーとを設ける。スイッチ素子が動作した場合に、外部から供給される電力の少なくとも一部が第2のAC/DC変換回路を介してバッテリーに供給される構成とする。

(もっと読む)

半導体装置

【課題】IC上に共振回路を形成することなく非接触な通信が可能な半導体装置を提供することを目的とする。また、IC上に形成する配線パターン及びアンテナの構造が簡易になり製造が容易な半導体装置を提供することを目的とする。

【解決手段】基板の一方の面に設けられたアンテナとして機能する導電膜と、ICチップと、ICチップと電気的に接続するように互いに独立して設けられた第1の導電膜及び第2の導電膜とを有し、ICチップは、第1の導電膜と第2の導電膜が基板を介してアンテナとして機能する導電膜と容量を形成するように基板の他方の面に設けられ、ICチップがアンテナとして機能する導電膜を介して外部とデータの送受信を行う。

(もっと読む)

半導体装置およびその製造方法

【課題】空乏化を生じず、また、製造工程における酸化、薬液による腐食、含有する金属による熱処理装置の汚染を抑えることのできるゲート電極を有し、且つトランジスタのオン電流の低下を抑えることのできる半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された金属含有層、並びに前記金属含有層の上面および側面を覆う不純物イオンを含んだ多結晶シリコン層からなるゲート電極と、を有する。

(もっと読む)

半導体素子及びその形成方法、半導体クラスタ装備

【課題】電気的な特性が向上される半導体素子の形成方法を提供する。

【解決手段】この方法は、導電パターン105を有する半導体基板100の上に絶縁膜110を形成する。絶縁膜をパターニングして導電パターンの一部を露出する開口部115を形成し、開口部の内壁及び絶縁膜の上部面に予備拡散防止膜120を形成する。予備拡散防止膜に酸素原子等を供給して第1拡散防止膜120aを形成する。第1拡散防止膜により囲まれている開口部を埋める金属膜152を形成する。この方法により製造された半導体素子及び半導体素子の製造に利用する半導体クラスタ装備を提供する。

(もっと読む)

半導体装置用電極膜

【課題】スパイク発生を解消する電極膜を提供する。

【解決手段】裏面電極膜5は、コレクタ層31の表面に、密着層11と拡散防止層12とバリア層13と電極本体層14と親和層15とがこの順序で形成されており、親和層15は、低融点金属層16によってステージに接続される。密着層11はアルミニウム合金であり、拡散防止層12はTi,Zr,Hf,V,Nb,Ta,Cr,Mo,Ta,W,Coのうち、1種類を含む金属であり、電極本体層14はNi合金であり、バリア層13は拡散防止層12の金属の窒化物である。

(もっと読む)

複数の誘電体を備えた半導体装置の製造方法

【課題】複数の誘電体を備えた半導体装置を製造するためのより良い方法を提供する。

【解決手段】基板200上に、第1制御電極誘電体材料202を設けること、基板200の少なくとも第1領域210aに、第1誘電体材料202を覆うパターン化した犠牲層を設けること、第1領域210aではパターン化した犠牲層を覆い、第2領域210bでは第1誘電体材料202を覆う第2誘電体材料203を設けること、但し、第2領域210bは、第1領域210aと異なっており、第2誘電体材料203をパターン化して、パターン化した第2誘電体材料が、第2領域210bでは第1誘電体材料202を覆い、第1領域210aではパターン化した犠牲層を覆わないようにすること、パターン化した犠牲層を除去することを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜上にpMOS電極材料として金属電極を形成する際に金属膜中からゲート絶縁膜へ拡散する炭素成分を抑制し、固定電荷要因を下げることができる半導体装置及びその製造方法を提供することである。

【解決手段】半導体装置の製造方法は、半導体基板100上にゲート絶縁膜101を形成する工程と、ゲート絶縁膜上に薄いシリコン層102を形成する工程と、この薄いシリコン層上にゲート絶縁膜界面での仕事関数が所定範囲内の値となる金属膜103を形成する工程と、を備えたものである。

(もっと読む)

半導体装置

【課題】大画面化しても低消費電力、歩留まり及び信頼性の向上を実現するための半導体装置の構造及びその作製方法を提供する。

【解決手段】画面で使われる画素薄膜トランジスタを逆スタガ型薄膜トランジスタで作製する。その逆スタガ型薄膜トランジスタにおいて、ソース配線、ゲート電極を同一平面上に作製する。また、ソース配線と逆スタガ型薄膜トランジスタ、画素電極と逆スタガ型薄膜トランジスタをつなぐ金属配線を同一工程で作製する。

(もっと読む)

半導体装置の製造方法

【課題】p型MOSFETとn型MOSFETとの間で異なる所望のしきい値を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板上にHf、 Zrの少なくとも1つと、Si、O、Nを含むゲート絶縁膜を形成し、第1、第2のゲート電極層を形成し、第1のゲート電極層上および第2のゲート電極層上に、第1の金属含有層を形成し、第2の金属含有層を形成し、保護膜を形成し、保護膜を選択的に除去し、残存する保護膜をマスクとして、第1の金属含有層および第2の金属含有層を選択的に除去し、第1の金属含有層および第2の金属含有層が選択的に除去された第2のゲート電極層上に、第3の金属含有層を成膜し、加熱処理により、第1のゲート電極層を合金化するとともに、第2のゲート電極層を合金化し、異なる組成のゲート電極を形成する。

(もっと読む)

半導体素子への金属含有膜の集積方法

【課題】 本発明は、半導体プロセスに関する。より具体的には、本発明は、化学気相成長法によって形成される金属含有膜を半導体素子に集積する方法に関する。

【解決手段】 たとえばゲートスタックのような、半導体素子中の金属含有膜を集積する方法。一の実施例では、当該方法は、処理チャンバ内に基板を供する手順、その基板をタングステンカルボニル含有ガスに曝露することによって、その基板上に、第1基板温度でタングステン含有膜を成膜する手順、第1基板温度よりも高温である第2基板温度でタングステン含有膜を熱処理することで、そのタングステン含有膜から一酸化炭素を除去する手順、及びその熱処理されたタングステン含有膜上にバリヤ層を形成する手順、を有する。タングステン含有膜の例には、W、WN、WSi、及びWCが含まれる。他の実施例は、Ni、Mo、Co、Rh、Re、Cr又はRuを含む金属含有膜を、各金属元素に対応した金属カルボニル先駆体から堆積する手順を有する。

(もっと読む)

半導体装置及びその製造方法

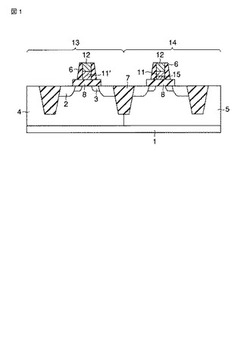

【課題】 ダマシンゲート技術等を用いてゲート電極が作製される半導体装置において、半導体装置の微細化等を可能にする。

【解決手段】 N型MISトランジスタ及びP型MISトランジスタそれぞれのゲート電極が半導体基板に形成された凹部内にゲート絶縁膜を介して形成されている半導体装置であって、N型MISトランジスタ及びP型MISトランジスタの一方のゲート電極は第1の金属含有膜F1及び第1の金属含有膜上の第2の金属含有膜F2の積層構造によって構成され、N型MISトランジスタ及びP型MISトランジスタの他方のゲート電極は第3の金属含有膜F3及び第3の金属含有膜上の第2の金属含有膜F2の積層構造によって構成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極を好適な仕事関数を有する導電材料から構成することができ、ゲート電極の構成材料と層間絶縁層のエッチング条件との関係を考慮する必要のない半導体装置を提供する。

【解決手段】NMISFET及びPMISFETを含む半導体装置であって、各ゲート電極32A,32Bは、層間絶縁層の下層部28Aに設けられたゲート電極形成用開口部に埋め込まれており、NMISFETのゲート電極32Aの少なくとも底面部と側面部は第1の導電材料33Aから構成されており、PMISFETのゲート電極32Bの少なくとも底面部と側面部は第1の導電材料とは異なる第2の導電材料33Bから構成されており、各ゲート電極32A,32Bの頂面上には、導電性を有する保護層35A,35Bが形成されており、各ゲート電極用コンタクトプラグ44A,44Bは、保護層35A,35Bを介して、各ゲート電極32A,32Bの頂面に接続されている。

(もっと読む)

161 - 180 / 259

[ Back to top ]