Fターム[4M104BB31]の内容

Fターム[4M104BB31]に分類される特許

141 - 160 / 259

表示装置の作製方法

【課題】露光マスク数を削減することでフォトリソグラフィ工程を簡略化し、信頼性のある表示装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】チャネルエッチ構造の逆スタガ型薄膜トランジスタを有する表示装置の作製方法において、透過した光が複数の強度となる露光マスクである多階調マスクによって形成されたマスク層を用いてエッチング工程を行う。さらに、基板上にゲート配線層とソース配線層を同工程で形成し、ゲート配線層とソース配線層の交差部においてはソース配線層を分断(切断)した形状とする。分断されたソース配線層は開口(コンタクトホール)を介してゲート絶縁層上にソース電極層及びドレイン電極層と同工程で形成された導電層を介して電気的に接続する。

(もっと読む)

半導体装置およびその製造方法

【課題】リーク電流の増大や被膜性の劣化やトランジスタ特性の劣化等のエッチングに伴う不具合を防ぐことが可能な半導体装置およびその製造方法を提供する。

【解決手段】CMOSトランジスタ500は、ゲート電極202を有するN型MOSトランジスタおよびゲート電極201を有するP型MOSトランジスタを同一の半導体基板1上に備え、ゲート電極202は、ゲート絶縁膜5と多結晶シリコン層61と金属層62と多結晶シリコン層63とを含み、ゲート電極201は、ゲート絶縁膜5と金属層62と多結晶シリコン層63とを含む。

(もっと読む)

半導体ウエハ上に膜を構築するためのチャンバ

【課題】抵抗率が改善された、共形性の高い拡散バリアの、インシチュウによる構築を遂行する。

【解決手段】本発明の一態様では、処理チャンバと、シャワーヘッドと、ウエハ支持体と、RFシグナル手段とを有していてもよい。シャワーヘッドを具備することにより、処理チャンバ内にガスを供給する。ウエハ支持体は、処理チャンバ内でウエハを支持するために具備される。シャワーヘッドに第1のRFシグナルを供給しまたウエハ支持体に第2のRFシグナルを供給するために、RFシグナル手段がシャワーヘッドとウエハ支持体の両方に結合していてもよい。あるいは、RFシグナル手段は、ウエハ支持体にRFシグナルを供給するためにウエハ支持体だけに結合していてもよい。本発明の態様を実施することによりアルミニウムや銅等のコンタクトメタルの拡散を防止する拡散バリアの能力を、向上させることができる。

(もっと読む)

半導体装置の製造方法

【課題】 本発明は、金属元素を有する絶縁膜の界面特性を向上させる半導体装置の製造方法を提供することを目的とする。

【解決手段】 本発明の半導体装置の製造方法は、下層、Ge層、Ge酸化物層、上層の順に積層された構造を形成する工程と、熱処理を用いてGe酸化物層及びGe層を除去して、上層と下層とを直接接合させる工程とを有し、上層及び下層の何れかは金属元素を有する絶縁物で形成されることを特徴とする。

(もっと読む)

表示装置の作製方法

【課題】電気特性に優れ、信頼性の高い薄膜トランジスタを有する表示装置を生産性よく作製する方法を提案することを課題とする。

【解決手段】ゲート電極上にゲート絶縁膜を形成し、ゲート絶縁膜上に微結晶半導体膜を成膜し、微結晶半導体膜の表面からレーザビームを照射して微結晶半導体膜の結晶性を改善する。次に、結晶性が改善された微結晶半導体膜を用いて薄膜トランジスタを形成する。また当該薄膜トランジスタを有する表示装置を作製する。

(もっと読む)

ショットキーダイオードを備える相変化メモリ素子

【課題】相変化メモリ素子を提供する。

【解決手段】基板上に一方向に延伸しているワードラインと、ワードライン上に位置する第1半導体パターンと、第1半導体パターン上に位置するノード電極と、第1半導体パターンとノード電極との間に形成されたショットキーダイオードと、ノード電極上に位置する相変化抵抗体と、を備える半導体メモリ素子。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極構造が異なるNch絶縁ゲート型電界効果トランジスタとPch絶縁ゲート型電界効果トランジスタのゲート電極形状を安定化させる。

【解決手段】半導体装置50には、Nch MISFETとPch FMISFETが半導体基板1上に設けられる。半導体基板1上に、Nch MISFETのソースとドレインの間にオーバラップしてゲート絶縁膜7、ゲート電極膜8、及び絶縁膜10が積層形成される。半導体基板1上に、Pch MISFETのソースとドレインの間にオーバラップしてゲート絶縁膜7、ゲート電極膜9、及び絶縁膜10が積層形成される。ゲート電極膜9はゲート電極膜8よりもゲート電極膜同時加工時での補正膜厚分だけ薄く形成されている。

(もっと読む)

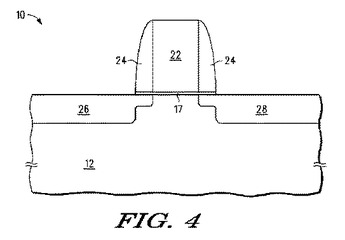

CETスケーリング用高k誘電体の処理方法

半導体装置(10)の作製方法は、上に重なるゲート電極(22)を有するゲート誘電体(17)を作製することを含む。半導体装置(10)は半導体層(12)上に作製される。ジルコン酸ハフニウムを含む高k誘電体(16)は半導体層上に蒸着される。高k誘電体は、水素と窒素を含む雰囲気中で650℃〜850℃の間の温度でアニーリングされる。ゲート電極(22)は高k誘電体上に形成される。高k誘電体機能は、ゲート誘電体(17)での使用のためである。一つの効果は、ゲート漏れのレベルを保持する、またはさらには改善させつつ、トランジスタの性能を向上させることである。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】N−chトランジスタとP−chトランジスタとの境界の寸法制御性に優れ、工程数の増加を最小限に抑制しながら、N−chトランジスタ及びP−chトランジスタのゲートパターンの高さが可能な限り揃った構造を実現する。

【解決手段】基板上のHigh−k膜よりなる絶縁膜上にポリシリコンを形成する。該ポリシリコン膜をエッチングする際にハロゲン系ガスを用いた低バイアス処理を施すことにより、下地のHigh−k膜の膜質を改善しながら、N−chトランジスタ及びP−chトランジスタに独立した仕事関数を持つ金属電極を形成する。

(もっと読む)

デュアルメタルゲート構造の形成方法

半導体構造(10)の形成方法は、第1および第2ウェル領域(16、18)を含む半導体層上にチャネル領域層(40)を形成すること、チャネル領域層上に保護層(80)を形成すること、第1ウェル領域上に第1ゲート誘電体層(26)を形成すること、第1ゲート誘電体上に第1メタルゲート電極層(28)を形成すること、保護層を除去すること、チャネル領域層上に第2ゲート誘電体層(42)を形成すること、第2ゲート誘電体層上に第2メタルゲート電極層を形成すること、第1ウェル領域上に、第1ゲート誘電体層と第1メタルゲート電極層の各々の一部を含む第1ゲートスタック(58)を形成し、チャネル領域層上に、第2ゲート誘電体層と第2メタルゲート電極層の各々の一部を含む第2ゲートスタック(66)を形成することを含む。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート長を増加させずにゲート電極の低抵抗化を可能にする。

【解決手段】半導体基板11上の絶縁膜12に形成されたゲート形成溝13の内部にゲート絶縁膜16を介してゲート電極17が形成され、前記ゲート電極17の一方側の前記半導体基板11にソース領域14が形成され、他方側の前記半導体基板11にドレイン領域15が形成された半導体装置1において、前記ゲート電極17は、前記ゲート形成溝13内から前記絶縁膜12表面より突出して形成されたゲート電極本体部30と、前記ゲート電極本体部30の前記絶縁膜12表面より突出した部分の側壁に形成された導電性のサイドウォール18とを有することを特徴とする。

(もっと読む)

ダメージフリー被覆刻設堆積法

【課題】 周辺表面を殆ど汚染又は乱さずに、スパッタリングされたキャリア/バリヤ層を堆積させて所望の形状に刻設する方法を提供する。

【解決手段】 堆積層のイオンの衝突により浸食・汚染されないように、刻設された層の適用された表面が保護される、イオン堆積スパッタリング法を用いて刻設された材料層を半導体の特徴表面に適用する方法であり、刻設された層の第1の部分を、その層の適用される表面が浸食又は汚染されない程度に基板バイアスを十分低くして適用するステップと、刻設された層の次の部分を、さらなる層材料を堆積させながら、第1の部分からの形状を刻設可能な程度に基板バイアスを十分高くして適用するステップとを含む。この方法は、半導体の特徴表面上にバリヤ層、ウェッティング層及び導電層等を刻設するのに特に適しており、導電層が銅である場合は特に有益である。

(もっと読む)

半導体装置

【課題】光電変換素子を配線基板等に実装するときに、その固着強度を向上させ、接触不良や剥離等の問題を解決することを課題とする。

【解決手段】第1の基板上に、光電変換層と、光電変換層の出力電流を増幅する、少なくとも2つの薄膜トランジスタからなる増幅回路と、前記光電変換層及び前記増幅回路に電気的に接続され、高電位電源を与える第1の電極及び低電位電源を与える第2の電極と、前記第1の基板の最上層に、導電材料と合金を形成する固着層とを有し、第2の基板上に、第3の電極と第4の電極と、前記第1の電極と前記第3の電極、並びに、前記第2の電極と前記第4の電極を固着する前記導電材料とを有する半導体装置に関する。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のMISトランジスタと第2のMISトランジスタとで相異なる絶縁材料からなるゲート絶縁膜を精度良く実現する。

【解決手段】N型MISトランジスタNTrは、半導体基板100における第1の活性領域100a上に形成された第1のゲート絶縁膜105aと、第1のゲート絶縁膜上に形成された第1のゲート電極108aとを備え、P型MISトランジスタPTrは、半導体基板における第2の活性領域100b上に形成され、第1のゲート絶縁膜とは異なる絶縁材料からなる第2のゲート絶縁膜103bと、第2のゲート絶縁膜上に形成された第2のゲート電極108bとを備え、第1のゲート電極と第2のゲート電極とは、素子分離領域上において、上部領域が互いに電気的に接続されていると共に、下部領域が互いに第1のゲート絶縁膜と同じ絶縁材料からなる側壁絶縁膜105xyを挟んで分離されている。

(もっと読む)

拡散バリアフィルムを含む半導体素子の形成方法

【課題】電気抵抗が低く、下部導電体と上部導電体間の拡散を防止する、拡散バリアフィルムの形成方法を提供する。

【解決手段】下部導電体102を含む基板100上に層間絶縁膜104を形成する。これに形成された開口部106に補助拡散バリア膜108を形成する。この上に拡散バリアフィルム120を形成する。この膜は、金属有機化学気相蒸着法による金属窒化物で形成され、部分的にプラズマ処理される。この結果、プラズマ処理された層とプラズマ処理されない層の積層膜となる。これにより、拡散バリアフィルムの比抵抗を減少させると共に、優れたバリア特性を有することができる。さらにこの上に粘着金属層122、第1アルミニウム膜130、第2アルミニウム膜132を形成する。これらの膜をパターンニングして上部導電体とプラグとする。

(もっと読む)

半導体装置及び当該半導体装置の作製方法

【課題】集積回路部上にアンテナを作り込んで設ける場合であっても、接続不良やコンタクト抵抗の増加を抑制することを課題とする。

【解決手段】基板上に第1の導電膜を有する集積回路部を形成し、集積回路部上に絶縁膜を形成し、絶縁膜上にアンテナとして機能する第2の導電膜を選択的に形成し、絶縁膜及び第2の導電膜に開口部を形成して第1の導電膜を露出させ、メッキ処理により開口部及び第2の導電膜の上面に第3の導電膜を形成することにより、第1の導電膜及び第2の導電膜とを電気的に接続する。

(もっと読む)

半導体デバイスにおける分離層の形成

半導体デバイス101が半導体層107により形成される。半導体層107の上方に第1のゲート誘電体層109が形成される。第1のゲート誘電体109の上方に第1の導体層111が形成される。第1の導体層の上方に第1の分離層113が形成される。第1のメサ201および第2のメサ203を分離するために半導体層107にトレンチ205が形成される。トレンチ205は第1の導体層111の上面を越える高さまで絶縁材料401で充填される。第2のメサ203から第1の導体層111が除去される。第1のメサ203の第1の分離層113の上方および第2のメサ203の上方に第2の導体層703が形成される。平坦化エッチングによって第1のメサ201の上方から第2の導体層703が除去される。第1のメサ201において第1の種類の第1のトランジスタ1201が形成され第2のメサ203において第2の種類の第2のトランジスタ1203が形成される。  (もっと読む)

(もっと読む)

配線及び記憶素子の作製方法

【課題】焼成を必要とする液滴吐出法をはじめとする塗布法において、配線や導電膜の作製時における焼成温度を低減することを課題とする。

【解決手段】液滴吐出法等の塗布法を用いて導電性材料よりなるナノ粒子が分散された組成物を吐出し、その後乾燥することで該溶媒を気化させる。そして、活性酸素による前処理を行った後、焼成を行うことで、配線もしくは導電膜を作製する。このように、焼成前に活性酸素による前処理を行うことで、作製時における焼成温度を低減することが可能となる。

(もっと読む)

絶縁膜の作製方法及び半導体装置の作製方法

【課題】非感光性のシロキサン樹脂を用いて、ウェットエッチング法で所望の形状に形成された絶縁膜を形成することができる、絶縁膜の作製方法を提供する。

【解決手段】有機溶媒中にシロキサン樹脂またはシロキサン系材料を有する懸濁液を用いて薄膜を形成し、薄膜に第1の加熱処理を施し、第1の加熱処理後の薄膜上にマスクを形成し、有機溶媒を用いてウェットエッチングすることで、第1の加熱処理後の薄膜の形状を加工し、加工された薄膜に第2の加熱処理を施す。

(もっと読む)

半導体装置およびその製造方法

【課題】高速かつ低消費電力、高記憶密度な半導体装置の製造方法を提供する。

【解決手段】半導体基板中のp型およびn型ウェル上にLa、Al、Oからなる第1および第2非晶質絶縁膜をそれぞれ形成し、第1、第2非晶質絶縁膜上に、その酸化物標準生成エンタルピーの絶対値が第2非晶質絶縁膜の酸化物標準生成エンタルピーの絶対値よりも小さい第1ゲート電極を形成し、その後形成された構造体全体を酸素雰囲気で熱処理し、その後、第1ゲート電極上に金属膜を形成し、第1ゲート電極と金属膜を固相反応させ、第2ゲート電極を形成する。

(もっと読む)

141 - 160 / 259

[ Back to top ]