Fターム[4M104BB32]の内容

Fターム[4M104BB32]に分類される特許

401 - 420 / 978

半導体装置およびその作製方法

【課題】工程を増やすことなく、1枚のマザーガラス基板上に所望の部分にそれぞれ精密に配線の側面の角度を異ならせた配線を提供することを課題とする。

【解決手段】多階調マスクを用いることで1つのフォトレジスト層を1枚のマザーガラス基板から遠ざかる方向に向かって断面積が連続的に減少するテーパ形状を有するフォトレジスト層を形成する。1本の配線を形成する際、1枚のフォトマスクを用い、金属膜を選択的にエッチングすることで、場所によって側面形状(具体的には基板主平面に対する角度)が異なる1本の配線を得る。

(もっと読む)

半導体装置

【課題】曲げ等の外力が加わり応力が生じた場合であってもトランジスタ等の損傷を低減する半導体装置を提供することを目的とする。

【解決手段】可撓性を有する基板上に設けられた第1の島状の補強膜と、第1の島状の補強膜上に、チャネル形成領域と不純物領域とを具備する半導体膜と、チャネル形成領域の上方にゲート絶縁膜を介して設けられた第1の導電膜と、第1の導電膜及びゲート絶縁膜を覆って設けられた第2の島状の補強膜とを有している。

(もっと読む)

銅の相互接続体のための窒化コバルト層及びそれらを形成する方法

集積回路のための相互接続構造体に、銅線の核形成、成長及び接着を促進する窒化コバルトの層が組み込まれる。銅の拡散バリヤーとして機能し、かつ窒化コバルトと下地の絶縁体の間の接着性も増加させる、窒化タングステン又は窒化タンタルなどの耐熱性の金属窒化物又は金属炭化物層上に窒化コバルトを堆積してよい。窒化コバルトは、新規なコバルトアミジナート前駆体からの化学気相成長により形成され得る。窒化コバルト上に堆積された銅層は、高い電気伝導度を示し、マイクロエレクトロニクスにおける銅伝導体の電気化学的な堆積のための種層として機能できる。 (もっと読む)

半導体装置の製造方法

【課題】 金属ゲート電極への熱負荷を低減可能であるとともに、高誘電率ゲート絶縁膜に対する高温での熱処理が可能である半導体装置の製造方法を提供する。

【解決手段】 半導体基板上に高誘電率ゲート絶縁膜及びダミーゲート電極を形成する工程と、少なくとも高誘電率ゲート絶縁膜及びダミーゲート電極をマスクとして半導体基板上にソース及びドレイン領域を形成する工程と、半導体基板上に層間絶縁膜を形成してその一部を除去することでダミーゲート電極上方を露出させる工程と、高誘電率ゲート絶縁膜上のダミーゲート電極を除去して溝を形成する工程と、溝の内部を被覆又は埋め込むように高誘電率ゲート絶縁膜上に金属ゲート電極を形成する工程と、を有する。

(もっと読む)

処理装置、その使用方法及び記憶媒体

【課題】熱処理の面内均一性の劣化を抑制してこれを高めることが可能な処理装置を提供する。

【解決手段】被処理体Wに熱処理を施す処理装置において、一側にゲートバルブ90を有すると共に天井側にシール部材56を介して蓋部44を有する処理容器42と、被処理体を載置する載置台68と、ガス導入手段48と、容器内の雰囲気を排気する排気手段58と、被処理体用加熱手段70と、ゲートバルブ加熱手段96と、容器側壁に設けた容器加熱手段98と、容器加熱手段を制御することによりゲートバルブ側の側壁の設定温度よりもゲートバルブとは反対側の側壁の設定温度の方が高くなるようにすると共に、設定温度は熱処理により発生する反応副生成物の昇華温度以上又は前記ガスの凝縮付着温度以上で且つシール部材の透過ガスが増加する温度以下となるようにする温度制御部110とを備える。

(もっと読む)

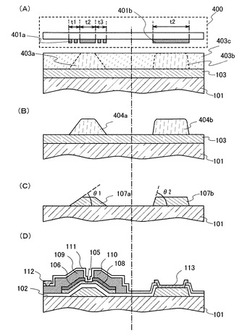

半導体素子及びその製造方法並びに表示装置

【課題】駆動力向上、サブスレッショルド係数低減、オフ電流低減、駆動電圧の低減等トランジスタ特性の高性能化、低消費電力化を実現する半導体素子を提供する。

【解決手段】基板101上に設けられた導電性電極103と、導電性電極103上に設けられた絶縁膜104と、絶縁膜104を介して導電性電極103上部に設けられた半導体105と、半導体105の両側に、絶縁膜104に接して設けられた導電性領域109とを備える。

(もっと読む)

配線構造および半導体装置

【課題】電気を流すことができる。

【解決手段】基板11と、基板11上に形成された、開口孔を有する絶縁膜12と、開口孔の底部に形成された、内部にアルカリ金属原子(またはハロゲン原子)16aを有する筒状炭素構造体14と、を有する配線構造10により、基板11と、基板11上に形成された、開口孔を有する絶縁膜12と、開口孔の底部に形成された、内部にアルカリ金属原子(またはハロゲン原子)16aを有する筒状炭素構造体14とにより、筒状炭素構造体14が金属性を示す。

(もっと読む)

多層浮遊ゲート不揮発性メモリデバイス

【課題】所望の特性の層をより良好に確保できる多層浮遊ゲート不揮発性メモリデバイスを提供する。

【解決手段】本発明は、異なる導電性または半導電性の材料で構築された少なくとも2つの層(1a,1b)を含む浮遊ゲートを持つ浮遊ゲート不揮発性メモリセルに関する。浮遊ゲートの少なくとも2つの層は、層間の直接トンネル電流を可能にする所定の厚さを有する中間誘電体層によって分離している。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率膜をゲート絶縁膜として用い、pチャネル型MISFETおよびnチャネル型MISFETのそれぞれに要求されるしきい値電圧を容易に実現できる相補型MISFETおよびその製造技術を提供する。

【解決手段】n型ウエル3およびp型ウエル4のそれぞれの表面に清浄な酸化シリコン膜5を形成した後、酸化シリコン膜5上に2A族元素の酸化物、3A族元素の酸化物、3B族元素の酸化物、4A族元素の酸化物、および5A族元素の酸化物等からなる酸素欠損調整層6と、高誘電率膜8と、水素に対する還元触媒効果を有する導電性膜12とを順次堆積し、H2を含む雰囲気中にて基板1に対して熱処理を施すことで酸素欠損調整層6と酸化シリコン膜5との間にダイポールを形成する。その後、導電性膜12、高誘電率膜8、酸素欠損調整層6および酸化シリコン膜5等をパターニングしてゲート電極およびゲート絶縁膜を形成する。

(もっと読む)

半導体記憶装置及びその製造方法と駆動方法

【課題】寄生抵抗の増大なく、ホットキャリアによる特性劣化を抑制できる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】ガラス基板1上に形成した半導体層3と、半導体層3上に形成したONO膜による電荷保持膜21と、電荷保持膜21上に設けたゲート電極22とを備える。更に半導体層3にゲーート電極22とオーバーラップするように設けられたニッケルシリサイド等の半導体と金属の化合物からなるソース・ドレイン領域23を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】それぞれが最適なゲート絶縁膜及びゲート電極を有するp型MISFET及びn型MISFETを備え且つ不良の原因となるポリシリコン膜残渣が発生することがない半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板10の第1領域10Aの上に形成された第1のゲート絶縁膜13Aと、第1のゲート絶縁膜13Aの上に形成された第1のゲート電極14Aと、半導体基板10の第2領域10Bの上に形成された第2のゲート絶縁膜13Bと、第2のゲート絶縁膜13Bの上に形成された第2のゲート電極14Bとを備えている。第1のゲート絶縁膜13Aは、第1の金属を含む第1の材料からなる第1の絶縁膜を有し、第2のゲート絶縁膜13Bは、第1の材料と第2の金属を含む第2の材料とが混合された第2の絶縁膜を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル及びpチャネルのゲート構造が異なり且つメタルゲート電極を有する半導体装置において、ゲート電極パターン形成時のドライエッチングでゲート絶縁膜の突き抜けが発生しないようにする。

【解決手段】ゲート絶縁膜105と接する第2ゲート電極材料膜(TiN膜)111がゲート電極151の一部として形成されないnチャネル領域103上に、第2ゲート電極材料膜(TiN膜)111のエッチング時にオーバーエッチング吸収層として機能する第1ゲート電極材料膜(ポリシリコン膜)107を予め形成しておく。

(もっと読む)

液晶表示装置及び電子機器

【課題】低比抵抗を有し、且つ上記ゲッタリング工程に十分耐えうる電極構造の必要に応じ、新規な電極構造を有する液晶表示装置を提供する。

【解決手段】絶縁表面を有する基板上に、多層構造を有するゲート電極と、前記基板、前記ゲート電極の上面および側面を覆う保護膜と、前記保護膜を覆って形成されたゲート絶縁膜と、前記ゲート絶縁膜上に接して、ソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域の間に形成されたチャネル形成領域と、を有する半導体素子からなる半導体回路を備える。保護膜は、高温処理を施した場合、基板からの不純物の拡散を抑えることができ、基板の不純物濃度に左右されることなく、良好なTFT特性を得ることができる。

(もっと読む)

銅配線の製造方法

【課題】極めて微細な孔又は溝内に銅を埋め込むことができる、新たな銅配線の製造方法を提供する。

【解決手段】1価の銅イオンと錯体を形成し、1価の銅イオンとの錯化定数が1×103より高い値を示し、且つ使用環境下において1価の銅イオンと形成する錯体の溶解度が0.5g/L以上の銅錯化剤、若しくは、1価の銅イオンと錯体を形成し、1価の銅イオンとの錯化定数が1×103より高い値を示し、且つ2価の銅イオンとの錯化定数が1×1020以下の値を示す銅錯化剤を1wt%以上と、水を1wt%以上と、銅成分とを含む電解液を強制攪拌しながら、被めっき体における配線接続孔又は配線溝内に銅を電気めっきする工程を備えた銅配線の製造方法によれば、攪拌の程度を調整することにより、微細孔への銅の埋め込み率を調整することができ、微細孔への銅の埋め込み率をより一層高めることができる。

(もっと読む)

窒化物半導体用電極および窒化物半導体装置

【課題】窒化物半導体を用いた窒化物半導体装置における電極の信頼性を向上することができる窒化物半導体用電極およびそれを含む窒化物半導体装置を提供する。

【解決手段】窒化物半導体上に形成される電極であって、窒化物半導体上に形成される金属窒化物層と、金属窒化物層上に形成される第1金属層と、第1金属層上に形成される第2金属層とを備え、第1金属層は、金属窒化物層に含まれる金属と同一の金属元素を含む窒化物半導体用電極とおよびそれを含む窒化物半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】nウエル及びpウエルに形成されたpMOS及びnMOSトランジスタのしきい値を精密に制御し、かつ製造容易にする。

【解決手段】nウエル2及びpウエル3上にゲート絶縁膜5を形成し、nウエル2上のゲート絶縁膜5上にpMOSトランジスタ11のしきい値制御用の第1金属膜6を、pウエル3上のゲート絶縁膜5上に第1金属膜6と異なる材料からなるnMOSトランジスタ12のしきい値制御用の第2金属膜7を形成する。そして、第1金属膜6上に高融点金属シリサイドからなる第1ゲート電極8pを、第2金属膜7上に高融点金属シリサイドからなる第2ゲート電極8nを形成する。しきい値は金属膜6、7で定まるから安定する。この金属膜6は薄く、容易にパターニングできる。

(もっと読む)

窒化物系半導体装置用多層電極構造

【課題】窒化物系半導体層に対する優れた付着力を有しかつ電解液に対する優れた耐腐食性をも有する窒化物系半導体装置用多層電極構造を提供する。

【解決手段】窒化物系半導体装置用多層電極構造は、窒化物系半導体層(101)上に順次積層される第1、第2、第3、および第4の電極層(102、103、104、105)を含み、第1電極層(102)は金属窒化物を含み、第2電極層(103)は相対的に低い標準電極電位を有する金属を含み、第4電極層(105)は相対的に高い標準電極電位を有する金属を含み、第2と第4の電極層に挟まれた第3電極層(104)は相対的に中間の標準電極電位を有する金属を含んでいることを特徴としている。

(もっと読む)

high−K誘電膜上に金属ゲートを蒸着する方法及び、high−K誘電膜と金属ゲートとの界面を向上させる方法、並びに、基板処理システム

【課題】金属酸化膜半導体電界効果トランジスタ(MOSFET)において、本発明の目的は、high−K誘電膜と金属ゲートとの間の界面特性を向上させることにより、電気的特性およびデバイス性能を向上させることである。

【解決手段】high−K誘電体上に金属ゲートを蒸着することによりMOSFETの製造においてhigh−K誘電膜と金属ゲートとの間の界面を向上させる方法は、熱アニーリングモジュール内で、その上にhigh−K誘電膜が蒸着された基板をアニールするアニーリングステップと、金属ゲート蒸着モジュール内で、前記アニールされた基板上に金属ゲート材料を蒸着させる蒸着ステップとを含み、真空を破ることなく、前記アニーリングステップおよび前記蒸着ステップが連続的に行なわれることを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】アクティブマトリクス型の液晶表示装置に代表される電気光学装置において、逆スタガ型の薄膜トランジスタを有する画素部及び端子部を作製する工程数を削減して、具体的にはフォトリソグラフィー工程で使用するフォトマスクの枚数を削減して、電気光学装置の生産性、歩留まりを向上させ、製造コストの低減を実現することを課題とする。

【解決手段】上記課題を鑑み、透光性基板に透過部と光強度を低減する機能を有する中間透過部と遮光部が設けられたフォトマスク(多階調フォトマスク)を採用する。さらには、画素部のソース電極及びドレイン電極と端子部に延在するソース配線のパターニングにエッチング工程を必要としないリフトオフ方法を採用する。

(もっと読む)

半導体装置及びその製造方法

【課題】駆動能力を低下させることなく、半導体装置内部の高電界が与える影響によって生じるGIDLを低減する。

【解決手段】ゲート電極108は、ゲート電極108のチャネル長方向の中央部に位置し且つ高誘電率膜107つまりゲート絶縁膜と接する第1の導電部108Aと、ゲート電極108のチャネル長方向の両端部に位置し且つ高誘電率膜107つまりゲート絶縁膜と接する第2の導電部108Bとを含む。第1の導電部108Aの第1の仕事関数と第2の導電部108Bの第2の仕事関数とが異なっている。

(もっと読む)

401 - 420 / 978

[ Back to top ]