Fターム[4M104BB32]の内容

Fターム[4M104BB32]に分類される特許

321 - 340 / 978

スパッタリング装置及び半導体装置の製造方法

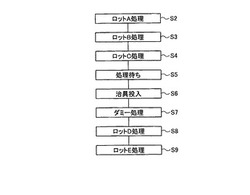

【課題】マルチチャンバーにおけるステージ温度の急激な低下を抑制することによって品質異常を抑制することのできるスパッタリング装置を提供する。

【解決手段】本発明に係るスパッタリング装置は、第1チャンバーと、第2チャンバーと、第3のチャンバーとを具備しており、第3のチャンバーにて処理待ち状態が所定時間経過した後(S5)、ダミー収容室内のダミー基板を第2チャンバー内にて、ダミー基板を加熱しながらダミー基板上に金属膜をスパッタリング成膜し、第2チャンバー内のダミー基板を第3チャンバー内にて、ダミー基板を加熱しないで金属膜上に第2の膜をスパッタリング成膜する(S7)。その後、第3チャンバーにおいて、第2チャンバーによって金属膜が成膜された基板を加熱しない状態で金属膜上に第2の膜をスパッタリング成膜する(S8)。これによって、マルチチャンバーにおけるステージ温度を制御することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】オフセットスペーサが除去されることを防止する。

【解決手段】第1導電型の半導体領域10x上に形成されたゲート絶縁膜13Aと、ゲート絶縁膜上に形成されたゲート電極15Aと、ゲート電極の側面上に形成されたオフセットスペーサ17Aと、ゲート電極の側面上にオフセットスペーサを介して形成された断面形状がL字状の内側サイドウォール19と、ゲート電極15A、オフセットスペーサ17A、内側サイドウォール19、及び半導体領域10xにおける内側サイドウォール19の外側方に位置する領域を覆うように形成された絶縁膜24とを備え、オフセットスペーサ17Aは、ゲート電極の側面上に形成された内側オフセットスペーサ16と、ゲート電極の側面上に内側オフセットスペーサ16を覆うように形成された外側オフセットスペーサ17とを有し、外側オフセットスペーサは、内側オフセットスペーサの上端及び外側面に接して形成されている。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体層とソース電極層及びドレイン電極層との間にバッファ層が設けられた順スタガ型(トップゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース電極層及びドレイン電極層と半導体層との間に、半導体層よりもキャリア濃度の高いバッファ層を意図的に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

塊状化抑制と半導体デバイスの密着性向上のための方法

【課題】半導体装置の金属配線として用いられる銅層が塊状になるのを抑え、さらに拡散バリア層との密着性を向上させるため、改良された付着方法、又はメタライゼーション方法を提供する。

【解決手段】銅シード層とバリア層の間に密着促進層を被着する。コンピュータを用いたシミュレーションで銅膜の塊状化が起こる状況および銅層の密着性に関する評価を行い、密着促進層材料にクロム合金を用いることで、銅膜の密着性を著しく高める。さらにポリデンテートβ−ケトイミネートのクロム含有錯体を密着促進層材料のクロム合金を作るためのクロム含有前駆物質とする。

(もっと読む)

ルテニウム微粒子及びその製造法、並びにルテニウム微粒子を下層金属膜とした金属含有薄膜の製造方法

【課題】 本発明の課題は、ルテニウム微粒子を下層金属膜とした、平坦な連続金属含有薄膜及び連続銅含有薄膜及びその製造法を提供するものでもある。

【解決手段】 本発明の課題は、有機ルテニウム錯体を化学気相蒸着法によりルテニウム含有薄膜を製造させた後、次いで、そのルテニウム含有薄膜の上に、有機金属錯体を化学気相蒸着法により金属含有薄膜を形成させることにおいて、当該ルテニウム含有薄膜がルテニウム微粒子であることを特徴とするルテニウム微粒子によって解決される。

(もっと読む)

半導体装置及びその作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体層とソース電極層及びドレイン電極層との間に金属酸化物層でなるバッファ層が設けられた逆スタガ型(ボトムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース電極層及びドレイン電極層と半導体層との間に、バッファ層として金属酸化物層を意図的に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

配線、その製造方法、薄膜トランジスタおよび表示素子

【課題】良好な形状制御性を確保しつつ、銅配線層の酸化および銅の拡散を抑制できる配線を提供する。

【解決手段】金属拡散防止膜51上に形成したシード層52を、レジストを用いて選択的に除去する。レジストを除去した後、シード層52を覆って無電解めっき法により銅配線層53と、銅配線層53上に位置するメタルマスク層54とを形成する。メタルマスク層54を用いて金属拡散防止膜51を選択的に除去する。良好な形状制御性を確保しつつ、金属拡散防止膜51の形成時のエッチングなどによる銅配線層53の表面荒れなどを防止して、銅配線層53の酸化および銅の拡散を抑制できる。

(もっと読む)

半導体装置

【課題】 LDD形成工程に於けるプラズマプロセスが原因となり生じる素子の

損傷を極力低減した半導体装置の作製方法を提供すること。

【解決手段】 基板全面を覆うように導電性膜を形成した状態で、ハードマスク

を利用した半導体装置の作製方法でLDD構造の素子を形成することにより、L

DD形成工程におけるプラズマプロセスによる素子への損傷を極力低減する。導

電性膜が全面に形成されていることにより、異方性エッチング等のプラズマによ

る処理(プラズマプロセス)においてゲート電極に蓄積される電荷密度を低減で

き、プラズマプロセスによる損傷を低減できる。

(もっと読む)

半導体装置およびその製造方法

【課題】エレクトロマイグレイション耐性の高いエアブリッジ配線を具備した半導体装置及びその製造方法を提供すること。

【解決手段】第1の配線と、第1の配線から空間によって隔てられた状態で、前記第1の配線の上を横切る第2の配線と、前記第1及び第2の配線に接続された半導体素子を具備し、前記第2の配線は、下から順に、タンタル層、タンタルナイトライド層、及び金層が積層されて形成されていること。

(もっと読む)

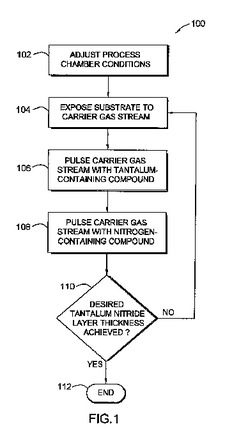

インサイチュチャンバ処理および堆積プロセス

本発明の実施形態は、原子層堆積(ALD)または化学気相堆積(CVD)などの気相堆積プロセス中に、プロセッシングチャンバの内面を処理し、材料を堆積させる方法を提供する。一実施形態では、前処理プロセス中に、プロセッシングチャンバの内面および基板を、水素化配位子化合物などの試薬にさらすことができる。この水素化配位子化合物は、次の堆積プロセス中に使用される有機金属前駆体から形成される遊離配位子と同じ配位子とすることができる。この遊離配位子は、堆積プロセス中に、通常、水素化または熱分解によって形成される。一例では、プロセッシングチャンバおよび基板は、ペンタキス(ジメチルアミノ)タンタル(PDMAT)などのアルキルアミノ配位子を有する有機金属化学前駆体を利用した気相堆積プロセスを行う前に、前処理プロセス中に、アルキルアミン化合物(例えば、ジメチルアミン)にさらされる。  (もっと読む)

(もっと読む)

双方向ダイオード、双方向ダイオードを用いた不揮発性半導体記憶装置、およびその製造方法

【課題】金属電極/半導体層/金属電極または金属電極/絶縁体層/金属電極の積層構造を有した双方向ダイオードにおいて、オン/オフ電流比を向上させることができる構造および、その製造方法を提供すること。

【解決手段】上に向かって凸型の形状を有する下部電極203を形成する工程と、その上に堆積表面の角度に対して堆積レートが異なる成膜法を用いて半導体層または絶縁体層202を形成する工程と、その上に上部電極201を形成する工程と、を備えることを特徴とする。

このような構成にすることにより、双方向ダイオードの印加電圧がオフ領域のときに流れるオフ電流は素子端部のみを流れるが、印加電圧がオン領域のときのオン電流は素子全面を流れるようになり、オン/オフ電流比を向上させることができる。

(もっと読む)

障壁表面上のコバルト堆積

本発明の実施形態は、障壁層上にコバルト層を堆積させた後、コバルト層上に銅または銅合金などの導電材料を堆積させるプロセスを提供する。一実施形態では、基板表面上に材料を堆積させる方法であって、基板上に障壁層を形成するステップと、気相成長プロセス(たとえば、CVDまたはALD)中に基板をジコバルトヘキサカルボニルブチルアセチレン(CCTBA)および水素に露出させて障壁層上にコバルト層を形成するステップと、コバルト層を覆うように導電材料を堆積させるステップとを含む方法が提供される。いくつかの例では、障壁層および/またはコバルト層は、熱プロセス、インサイチュプラズマプロセス、または遠隔プラズマプロセスなどの処理プロセス中にガスまたは試薬に露出させることができる。  (もっと読む)

(もっと読む)

デュアル金属ゲートのコーナー部

【課題】 デュアル金属ゲートのコーナー部を有する改良された電界効果トランジスタを提供する。

【解決手段】 上記を鑑みて、改善された電界効果トランジスタ(FET)構造体、及び該構造体を形成する方法の実施形態が開示される。このFET構造体の実施形態の各々は、固有のゲート構造体を組み込む。具体的には、このゲート構造体は、FETチャネル領域の中央部分の上方の第1のセクションと、チャネル幅のエッジの上方(すなわち、チャネル領域と隣接する分離領域との間の界面の上方)の第2のセクションとを有する。第1のセクション及び第2のセクションは、これらが異なる有効仕事関数(すなわち、それぞれ第1の有効仕事関数及び第2の有効仕事関数)を有する点で異なる(すなわち、これらは、異なるゲート誘電体層及び/又は異なるゲート導体層を有する)。チャネル幅のエッジにおける閾値電圧が上昇することを確実にするように、異なる有効仕事関数が選択される。

(もっと読む)

デュアル仕事関数の金属ゲートを統合する際のイオン注入を用いた有効仕事関数の変化

【課題】 デュアル仕事関数の金属ゲートを統合する際にイオン注入を用いて有効仕事関数を変化させる方法を提供する。

【解決手段】 デュアル有効仕事関数をもつ金属ゲートを集積化するために有効仕事関数を変化させるためのイオン注入が提示される。1つの方法は、第1の型の電界効果トランジスタ(FET)領域及び第2の型のFET領域の上に、高誘電率(高k)層を形成することと、第1の型のFET領域及び第2の型のFET領域の上に、第1の型のFETに適合する第1の有効仕事関数をもつ金属層を形成することと、第2の型のFET領域の上の金属層内に種を注入することによって、第2の型のFET領域の上の第1の有効仕事関数を第2の異なる有効仕事関数に変化させることとを含むことができる。

(もっと読む)

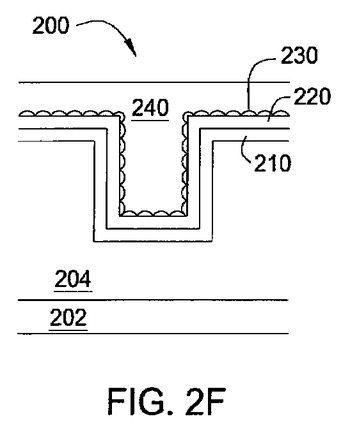

金属相互接続のための共形接着促進材ライナ

【課題】 金属相互接続のための共形接着促進材ライナを提供すること

【解決手段】 誘電体層を少なくとも1つのライン・トラフ及び/又は少なくとも1つのビア・キャビティを有するようにパターン化する。金属窒化物ライナをパターン化誘電体層の表面上に形成する。金属ライナを金属窒化物ライナの表面上に形成する。共形銅窒化物層を、原子層堆積(ALD)又は化学気相堆積(CVD)によって、金属ライナの直接上に形成する。Cuシード層を共形銅窒化物層の直接上に形成する。少なくとも1つのライン・トラフ及び/又は少なくとも1つのビア・キャビティは、電気めっき材料で充填される。共形銅窒化物層とCuシード層との間の直接接触は、強化された接着強度を与える。共形銅窒化物層をアニールして、露出した外側部分を連続的なCu層に変換することができ、このことはCuシード層の厚さを減すのに用いることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】STI幅の増加や信頼性の低下を招くことなく、所定の導電型トランジスタ領域において最適なHigh-kゲート絶縁膜を実現する。

【解決手段】N型トランジスタ領域RnとP型トランジスタ領域Rpとを含む半導体基板101上の全面にHigh-k絶縁膜103、N型トランジスタ用キャップ膜104及び金属含有膜105を順次堆積する。P型トランジスタ領域Rpに位置するN型トランジスタ用キャップ膜104にイオン107を導入することにより、P型トランジスタ用キャップ膜108を形成する。金属含有膜105上にポリシリコン膜111を堆積した後、パターニングにより、N型トランジスタ用ゲート電極113及びP型トランジスタ用ゲート電極114を形成する。

(もっと読む)

半導体加工方法

【課題】high−k膜/メタルゲート構造を有する半導体素子のドライエッチングにおいて、メタルゲート部分を垂直にエッチングする。

【解決手段】減圧処理室204と、該減圧処理室に処理ガスを供給するガス供給手段と、前記減圧処理室内に、半導体基板を載置して保持する試料台205と、前記減圧処理室に供給された処理ガスに高周波エネルギを供給してプラズマを生成するプラズマ生成手段を備え、生成したプラズマにより前記半導体基板にプラズマエッチング処理を施す半導体加工方法において、前記試料台上に、HfあるいはZrを含む高誘電率絶縁膜、TiあるいはTaを含む仕事関数制御金属導体膜、およびレジストを順次形成した半導体基板206を載置し、前記レジストを用いて前記導体膜をエッチング加工するに際して、前記試料台にオンオフ変調された基板バイアス電圧を印加する。

(もっと読む)

半導体装置の製造方法

【課題】仕事関数金属膜と低抵抗膜とで構成されたゲート電極をプラズマエッチングする際に、膜質に応じたエッチングステップの切り替えの遅延を防ぐ。

【解決手段】低抵抗膜6中であって、仕事関数金属膜4との界面の近傍に、プラズマ発光モニタに感度のある、窒素を含む進捗モニタ層5を設けることで、エッチング中のプラズマ発光の変化を検知し、エッチングの進捗をモニタすることでエッチングステップ切り替えの遅延を防止することができる。

(もっと読む)

半導体装置、及びその製造方法

【課題】 金属層と半導体層との接続抵抗の上昇を抑えた積層ゲート電極を有する半導体装置、及びその製造方法を提供する。

【解決手段】 半導体装置10は、半導体基板11に形成された第1導電型のソース領域及びドレイン領域14と、ソース領域とドレイン領域との間に形成されたチャネル領域16と、チャネル領域上に形成されたゲート絶縁膜21とを有する。半導体装置10は更に、ゲート絶縁膜上に形成された金属ゲート電極層22と、金属ゲート電極層上に形成された、第1導電型とは逆の導電型である第2導電型の半導体ゲート電極層23とを有する。

(もっと読む)

バリア蒸着のための液相分子自己組織化および形成構造

マイクロ電子構造を形成する方法及びその形成構造について記載する。無水溶媒に金属前躯体を溶液槽にて溶解し、配線開口を有する基板を溶液槽に配置して、金属前躯体により配線開口内に単分子層を形成する。また、基板を共反応体の混合液中に配置して、共反応体と金属前躯体とを反応させて薄いバリア層を形成する。 (もっと読む)

321 - 340 / 978

[ Back to top ]