Fターム[4M104BB32]の内容

Fターム[4M104BB32]に分類される特許

241 - 260 / 978

半導体デバイスとその形成方法(高k金属ゲートCMOS)

【課題】 金属酸化膜半導体電界効果トランジスタ内にデバイス性能を改善するゲート構造体を提供する。

【解決手段】 基板のp型デバイス領域の上にGe含有層を形成することを含む、半導体デバイスを形成する方法が提供される。その後、基板の第2の部分内に第1の誘電体層が形成され、基板の第2の部分内の第1の誘電層及び基板の第1の部分の上を覆うように、第2の誘電体層が形成される。次に、基板のp型デバイス領域及びn型デバイス領域の上にゲート構造体を形成することができ、n型デバイス領域へのゲート構造体は希土類金属を含む。

(もっと読む)

半導体装置の製造方法

【課題】ソース、ドレインの低抵抗化及び寄生容量の低減化のための構造、所望のゲート長、ソース、ドレイン形状、柱状半導体の直径が得られるSGTの製造方法を提供する。

【解決手段】第1の平面状半導体層上に第1の柱状半導体層を形成する工程と、第1の柱状半導体層の下部と第1の平面状半導体層に第1の第2導電型半導体層を形成する工程と、第1の柱状半導体層の底部及び第1の平面状半導体層上に第1の絶縁膜を形成する工程と、第1の柱状半導体層の周囲にゲート絶縁膜およびゲート電極を形成する工程と、ゲート電極の上部且つ第1の柱状半導体層の上部側壁と、ゲート電極の側壁に第2の絶縁膜をサイドウォール状に形成する工程と、第1の第2導電型半導体層と第2の第2導電型半導体層との間に第1導電型半導体層を形成する工程と、第1の第2導電型半導体層の上部表面と、第2の第2導電型半導体層の上部表面に金属と半導体の化合物を形成する工程とを含む。

(もっと読む)

金属窒化膜の成膜方法および記憶媒体

【課題】より低温でかつ高成膜速度で成膜することができる金属窒化膜の成膜方法を提供すること。

【解決手段】チャンバ内に被処理基板であるウエハを搬入し、チャンバ内を真空に保持した状態とし、ウエハを加熱しつつ、チャンバ内にTiCl4ガスとMMHガスとを交互的に供給してウエハ上にTiN膜を成膜する。

(もっと読む)

スレショルド電圧を有する電界効果トランジスタ、及びその製造方法

【課題】相異なるスレショルド電圧を有する電界効果トランジスタを提供する。

【解決手段】ドープ半導体ウエル上に、複数種のゲート・スタック(100〜600)が形成される。ドープ半導体ウエル(22、24)上に、高誘電率(high−k)ゲート誘電体(30L)が形成される。一つのデバイス領域中に金属ゲート層(42L)が形成され、他のデバイス領域(200、400、500、600)ではhigh−kゲート誘電体は露出される。該他のデバイス領域中に、相異なる厚さを有するスレショルド電圧調整酸化物層が形成される。次いで、スレショルド電圧調整酸化物層を覆って導電性ゲート材料層(72L)が形成される。電界効果トランジスタの一つの型は、high−kゲート誘電体部分を包含するゲート誘電体を包含する。電界効果トランジスタの他の型は、high−kゲート誘電体部分と、相異なる厚さを有する第一スレショルド電圧調整酸化物部分とを包含するゲート誘電体を包含する。相異なるゲート誘電体スタックと、同一のドーパント濃度を有するドープ半導体ウエルを用いることによって、相異なるスレショルド電圧を有する電界効果トランジスタが提供される。

(もっと読む)

半導体基板の作製方法

【課題】炭化シリコンを含む半導体基板の新たな作製方法を提供することを目的の一とする。

【解決手段】シリコン基板表面に炭化処理を施して炭化シリコン層を形成し、シリコン基板にイオンを添加することにより、シリコン基板中に脆化領域を形成し、シリコン基板とベース基板とを絶縁層を介して貼り合わせ、シリコン基板を加熱して、脆化領域においてシリコン基板を分離することにより、ベース基板上に絶縁層を介して炭化シリコン層とシリコン層の積層構造を形成し、シリコン層を除去して炭化シリコン層の表面を露出させることにより半導体基板を作製する。

(もっと読む)

半導体装置の製造方法

【課題】レジストマスクを用いたウエットエッチングにより、下地のゲート絶縁膜にダメージを与えることなく、寸法精度良く金属膜を加工する。

【解決手段】半導体装置の製造方法は、半導体基板100上に金属薄膜102を形成する工程(a)と、金属薄膜102の上にアルカリ水溶液可溶有機膜103を形成する工程(b)と、アルカリ水溶液可溶有機膜103の上にフォトレジスト膜104を形成する工程(c)と、フォトレジスト膜104に開口部を設けてレジストパターン105を形成する工程(d)と、薬液を用いて、開口部に露出するアルカリ水溶液可溶有機膜103を除去する工程(e)と、工程(e)の後に、ウエットエッチングにより、開口部に露出する金属薄膜102を除去する工程(f)とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】(110)面を主面とする半導体基板に形成されたp型MISトランジスタを備えた半導体装置において、p型MISトランジスタのさらなる性能向上を図る。

【解決手段】半導体装置は、(110)面を主面とする半導体基板10に形成されたp型MISトランジスタPTrを備えた半導体装置である。p型MISトランジスタPTrは、半導体基板10における第1の活性領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成され第1の金属膜14a及び第1の金属膜14a上に形成された第1のシリコン膜15aからなる第1のゲート電極14Aとを備えている。第1の金属膜14aは、膜厚が1nm以上であって且つ10nm以下である。

(もっと読む)

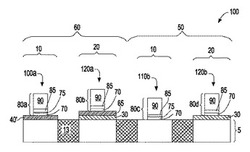

多重Vt電界効果トランジスタ素子

【課題】 多重閾値電圧(Vt)電界効果トランジスタ(FET)素子、及びその製造のための技術を提供する。

【解決手段】 1つの態様において、ソース領域と、ドレイン領域と、ソース領域とドレイン領域とを相互接続する少なくとも1つのチャネルと、チャネルの少なくとも一部を囲み、ゲート全体に対し選択的に配置された少なくとも1つのバンド・エッジ金属により多重閾値電圧を有するように構成されたゲートとを含むFET素子が提供される。

(もっと読む)

金属High−kFETのためのデュアル金属およびデュアル誘電体集積

【課題】本発明は、一つの実施形態において半導体デバイスを形成する方法を提供する。

【解決手段】該方法は、第一導電型領域および第二導電型領域を包含する基板を用意するステップと、基板の第一導電型領域および第二導電型領域の上のゲート誘電体とHigh−kの該ゲート誘電体上を覆う第一金属ゲート導体を包含するゲート・スタックを形成するステップと、第一金属ゲート導体の第一導電型領域中に所在する部分を除去して、第一導電型領域中に所在するゲート誘電体を露出するステップと、基板に対し窒素ベース・プラズマを印加するステップであって、窒素ベース・プラズマは、第一導電型領域中に所在するゲート誘電体を窒化し、第二導電型領域中に所在する第一金属ゲート導体を窒化する、該印加するステップと、少なくとも第一導電型領域中に所在するゲート誘電体上を覆う第二金属ゲート導体を形成するステップと、を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】本発明によれば、SiCを用いた微細化可能で、超低オン抵抗、かつ信頼性にも優れた半導体装置および半導体装置の製造方法を提供する。

【解決手段】炭化珪素基板と、その第1の主面の第1導電型の第1の炭化珪素層と、この表面の第2導電型の第1の炭化珪素領域と、この表面の第1導電型の第2の炭化珪素領域と、その下部の第2導電型の第3の炭化珪素領域と、第2の炭化珪素領域を貫通し、第3の炭化珪素領域に達するトレンチと、ゲート絶縁膜と、ゲート電極と、ゲート電極を被覆する層間絶縁膜と、トレンチ側面の第2の炭化珪素領域上および層間絶縁膜上に形成されたNi、Ti、Ta、MoおよびWからなる群から選択される金属元素を含有する第1の電極と、トレンチ底部の第3の炭化珪素領域上および第1の電極上に形成されたAlを含有する第2の電極と、第2の電極上の第1の主電極と、炭化珪素基板の第2の主面に形成された第2の主電極と、を有する半導体装置。

(もっと読む)

半導体装置

【課題】ゲート配線として耐熱性の導電性材料であるタングステン層を用いた場合に、タングステン層の比抵抗を低くすることによって、配線抵抗を十分に低減することを目的とする。

【解決手段】半導体層と、ゲート配線と、前記半導体層と前記ゲート配線との間に挟まれたゲート絶縁層とを有し、前記ゲート配線はタングステン層を有し、前記タングステン層中の酸素濃度を30ppm以下とすることによって、配線抵抗を十分に低減することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】MIPS構造を有する電界効果トランジスタにおいて、金属ゲート電極とポリシリコンゲート電極との接触抵抗を低減することにより、AC動作を向上させる。

【解決手段】半導体装置1は、半導体基板10上に電界効果トランジスタを有する。電界効果トランジスタは、ゲート絶縁膜25、27とゲート電極63、71と、を備える。さらに、ゲート電極63、71は第1金属からなる第1電極層22と、第2金属からなる第2電極層26、34と、シリコン層からなる第3電極層62、70と、を含む積層構造である。第2金属は、シリコン層の多数キャリアに対する第1電極層22と第3電極層62、70とのバンド不連続を緩和する仕事関数を有する材料である。

(もっと読む)

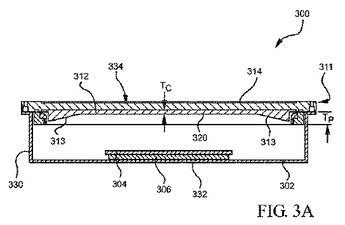

PVDチャンバ用スパッターターゲット

ターゲット組立体とターゲット組立体を含むPVDチャンバが開示される。ターゲット組立体は凹形状のターゲットを含む。PVDチャンバ内で使用されると、凹状ターゲットは、スパッターチャンバ内に配置された基板上の半径方向に均一な堆積層を提供する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクト形成時に、ゲート電極が溶解されて形状異常となるのを防止する。

【解決手段】半導体装置は、基板1上にゲート絶縁膜2を介して形成されたゲート電極31と、基板1のゲート電極31の両側方に形成された不純物領域32及び33とを有するトランジスタと、トランジスタ上を覆うように基板1上に形成された層間絶縁膜11及び12と、不純物領域32及び33及びゲート電極31に電気的に接続するシェアードコンタクト14とを備える。ゲート電極31の側面下部を覆うように第1のサイドウォール5、第1のサイドウォール5におけるゲート電極31とは反対側に第2のサイドウォール6、第1のサイドウォール5上に、ゲート電極31の側面上部と第2のサイドウォール6とに挟まれるように第3のサイドウォール9bが形成されている。第2及び第3のサイドウォール6及び9bは、第1のサイドウォール5とは異なる材料からなる。

(もっと読む)

半導体装置

【課題】半導体または誘電体と、金属との界面において、接合する金属の実効仕事関数を最適化することを可能にするとともに、抵抗を可及的に低くすることを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aと、を備え、酸化膜がTi酸化膜であって、酸化膜に、V、Cr、Mn、Fe、Co、Ni、Nb、Mo、Tc、Ru、Rh、Pd、Ta、W、Re、Os、Ir、Ptから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

半導体装置、半導体装置製造方法、TFT基板、および表示装置

【課題】オン電流を増加させて駆動能力を大きくした半導体装置(ダブルゲート型薄膜トランジスタ)、この半導体装置を製造する半導体装置製造方法、この半導体装置を搭載したTFT基板、およびこのTFT基板を適用した表示装置を提供する。

【解決手段】半導体装置1は、絶縁性基板10(絶縁性基板110)の上に形成された第1ゲート電極11と、第1ゲート電極11の上に形成された第1絶縁層12と、第1絶縁層12の上に形成された半導体層13と、半導体層13の一端に接続されたソース電極15と、ソース電極15に対向して半導体層13の他端に接続されたドレイン電極16と、半導体層13の上に形成された第2絶縁層17と、第2絶縁層17の上に形成された第2ゲート電極19とを備え、第1ゲート電極11および第2ゲート電極19の少なくとも一方は、透明導電性材料で形成され、透明電極を構成している。

(もっと読む)

半導体装置の製造方法

【課題】異なる積層構造を有する異なる導電型のトランジスタにおいて、ゲート電極における形状不良の抑制を図る。

【解決手段】半導体装置の製造方法は、第1導電型のMISFETを有する第1領域及び第2導電型のMISFETを有する第2領域における半導体基板1上に、ゲート絶縁膜3を形成する工程と、前記第1領域における前記ゲート絶縁膜上に、第1金属材料層4を形成する工程と、前記第1領域における前記第1金属材料層上及び前記第2領域における前記ゲート絶縁膜上に、第2金属材料層7からなる第2ゲート電極7a及び7bをそれぞれ形成する工程と、前記第1領域及び前記第2領域における前記第2ゲート電極の側面に、第1側壁絶縁膜11a及び11bをそれぞれ形成する工程と、前記第1側壁絶縁膜をマスクとして、前記第1領域における前記第1金属材料層を加工して第1ゲート電極4aを形成する工程と、を具備する。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】平滑で高品質のCVD−Cu膜を下地に対して高い密着性をもって成膜することができるCu膜の成膜方法を提供すること。

【解決手段】チャンバー1内にCVD−Ru膜を有するウエハWを収容し、チャンバー1内に、成膜中に発生する副生成物であるCu(hfac)2の蒸気圧がその蒸気圧よりも低いCu錯体であるCu(hfac)TMVSからなる成膜原料を気相状態で導入して、Ru膜上にCVD法によりCu膜を成膜するにあたり、チャンバー1の壁部の温度を、副生成物であるCu(hfac)2の蒸気圧が成膜処理時のチャンバー1内の圧力と等しくなる温度以上で成膜原料であるCu(hfac)TMVSの分解温度未満に制御する。

(もっと読む)

堆積チャンバにおける酸化からの導電体の保護

【課題】高導電度または低抵抗率を有する導電膜を形成するプロセスを提供する。

【解決手段】堆積チャンバにおいて基板上に導電膜を堆積した後、基板を取り出すためにチャンバ内に還元ガスを導入する。堆積チャンバはバッチCVDチャンバであってよく、堆積される膜は、例えば窒化チタンなど遷移金属窒化物である金属窒化物であってよい。チャンバから基板を取り出す準備の一部として、基板を冷却してよく、チャンバを還元ガスで充填してチャンバ圧力を上昇させる。この時にチャンバ内に酸化剤が導入され得ることが認められている。充填及び/または冷却プロセスの間、露出した金属含有膜を酸化から保護するために、還元ガスを導入することが発見された。還元ガスは、還元剤が還元ガスの少数成分であるような還元剤とキャリアガスとから形成される。還元剤を供給することによって、露出した金属含有膜の酸化が低減され、その結果金属膜の導電特性が向上する。

(もっと読む)

半導体装置

【課題】メタル電極/high−kゲート絶縁膜からなるゲート構造において、半導体特性や信頼性の劣化をおこさせることなく、サイドウォールを形成したゲート構造を有する半導体装置の提供。

【解決手段】半導体基板1上に設けられた、high−k誘電体材料からなるゲート絶縁膜2と、ゲート絶縁膜2の上に設けられたメタル電極3と、メタル電極3の側壁を覆い、ゲート絶縁膜2を挟んで半導体基板1と対向配置された酸化防止膜4と、ゲート絶縁膜2と酸化防止膜4とを覆うように、半導体基板上に設けられたサイドウォール5とを含むゲート構造。

(もっと読む)

241 - 260 / 978

[ Back to top ]