Fターム[4M104BB32]の内容

Fターム[4M104BB32]に分類される特許

221 - 240 / 978

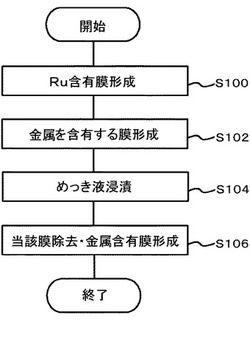

半導体装置の製造方法

【課題】Ru含有膜の表面に形成される金属含有膜の成膜性を向上させることができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、以下の工程を含むものである。基板(半導体素子や層間膜が形成された半導体基板など)にRu含有膜を形成する工程(S100)、Ru含有膜の表面と接するように、Ruより酸化還元電位が低い金属を含有する膜を形成する工程(S102)、基板をめっき液に浸漬させて、当該膜にめっき液を接触させる工程(S104)、基板をめっき液に浸漬させた状態で、当該膜を電気分解により除去してRu含有膜を露出させるとともに、露出したRu含有膜の表面に金属含有膜を電解めっきにより形成する工程(S106)。

(もっと読む)

半導体装置およびその作製方法

【課題】半導体装置の電極に関するもの又は接合工程を有する半導体装置の作製方法に関し、(1)Al電極を用いることにより高抵抗になること、(2)AlとSiとが合金を形成すること、(3)スパッタ法により形成する膜が高抵抗になること、(4)接合工程では、それぞれの面の表面に凹凸が大きいと接合不良が生じること、が課題である。

【解決手段】金属基板又は金属膜が形成された基板を有し、金属基板上又は金属膜上の銅(Cu)メッキ膜を有し、Cuメッキ膜上のバリア膜と、バリア膜上の単結晶シリコン膜と、単結晶シリコン膜上の電極層と、を有する半導体装置を用いる。Cuメッキ膜と金属基板又は金属膜とを接合する際に熱圧着法を用いる。

(もっと読む)

配線を形成する方法及びプラズマスパッタリアクタ

【課題】アスペクト比の高いホール内に、被覆性の良好な、コンタクト抵抗の低いバリア層を形成する半導体装置の製造方法を提供する。

【解決手段】タンタルまたはタンタルナイトライド等のライナー材料をホール内にスパッタ堆積する。ロングスロースパッタリング、自己イオン化プラズマ(SIP)スパッタリング、誘導結合プラズマ(ICP)再スパッタリング及びコイルスパッタリングを1つのチャンバ内で組み合わせたリアクタ150を使う。ロングスローSIPスパッタリングは、ホール被覆を促進する。ICP再スパッタリングは、ホール底部のライナー膜の厚さを低減して、第1のメタル層との接触抵抗を低減する。ICPコイルスパッタリングは、ICP再スパッタリングの間、再スパッタリングによる薄膜化は好ましくないホール開口部に隣接しているような領域上に、保護層を堆積する。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極を有するpチャネル型電界効果トランジスタにおいて、所望するしきい値電圧を安定して得ることのできる技術を提供する。

【解決手段】半導体基板1上に形成されたHfSiON膜からなるゲート絶縁膜5h上に、Me−O−Al−O−Me結合を含むMe1−xAlxOy(0.2≦x≦0.75、0.2≦y≦1.5)組成の導電性膜を一部に有するメタルゲート電極6、またはMe−O−Al−N−Me結合を含むMe1−xAlxN1−zOz(0.2≦x≦0.75、0.1≦z≦0.9)組成の導電性膜を一部に有するメタルゲート電極6を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】高温環境下での絶縁膜の腐食を抑制して、絶縁不良を回避した半導体装置及びその製造方法を提供することことを課題とする。

【解決手段】半導体基板11上にエピタキシャル成長により第1絶縁膜12が積層形成され、この第1絶縁膜12上には、耐熱性の電極13が選択的に形成され、この電極13の上部には、シリカガラスを主成分とする層間絶縁膜14が形成され、この層間絶縁膜14の表面には絶縁バリア膜15が形成され、この絶縁バリア膜15の上には、Alの配線16が形成され、絶縁バリア膜15は、絶縁性の窒化物、炭化物、窒化炭化物の単層膜、多層膜、または混合膜で構成されている。

(もっと読む)

半導体装置の製造方法

【課題】ハーフピッチサイズが32nm以下のCMISデバイスを有する半導体装置において、nチャネル型電界効果トランジスタおよびpチャネル型電界効果トランジスタのそれぞれの閾値電圧を適切に設定することのできる技術を提供する。

【解決手段】pMIS形成領域に、主としてAlが拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜5ならびに下層メタルゲート電極6Dと上層メタルゲート電極6Uとの積層膜からなるメタルゲート電極6を有するpMIS100pを形成し、nMIS形成領域に、主としてLa(ランタン)が拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜11ならびに上層メタルゲート電極6Uからなるメタルゲート電極12を有するnMIS100nを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】EOTの増大及びキャリア移動度の低下を抑制しつつ、半導体基板表面に形成されている酸化膜と高誘電率絶縁膜との界面に、しきい値電圧を低減する電気双極子を形成可能な金属を添加する。

【解決手段】半導体基板100上にゲート絶縁膜140を介してゲート電極150が形成されている。ゲート絶縁膜140は、酸素含有絶縁膜101と、第1の金属を含む高誘電率絶縁膜102とを有する。高誘電率絶縁膜102は、第1の金属とは異なる第2の金属をさらに含む。高誘電率絶縁膜102における第2の金属の組成比が最大になる位置は、高誘電率絶縁膜102と酸素含有絶縁膜101との界面及び高誘電率絶縁膜102とゲート電極150との界面のそれぞれから離れている。

(もっと読む)

半導体装置の製造方法

【課題】 トランジスタのスイッチング速度低下を防止することが可能な半導体装置の製造方法を提供する。

【解決手段】 本発明では、半導体基板100上にゲート絶縁膜104を形成する工程と、ゲート絶縁膜104上に金属膜107を形成する工程と、金属膜107上に金属シリコン化合物膜108を連続して堆積する工程と、金属シリコン化合物膜108上にシリコン膜110を形成する工程と、金属膜107、金属シリコン化合物膜108及びシリコン膜110を加工する工程と、を備える。

(もっと読む)

窒化物半導体装置および窒化物半導体装置製造方法

【課題】窒素不足に起因する移動度の低下を抑制し、窒素不足に起因するリーク電流を低減することができる窒化物半導体装置、その製造方法を提供する。

【解決手段】窒化物半導体装置1は、基板10と、バッファ層11と、窒化物半導体層(第1窒化物半導体層12、第2窒化物半導体層13、第3窒化物半導体層14)と、第1電極22と、第2電極23と、制御電極25とを備える。第1電極22と第2電極23との間で第3窒化物半導体層14の表面から第2窒化物半導体層13に渡って凹状に形成されたリセス部16を備え、リセス部16は、絶縁性窒化物で形成された窒化物絶縁膜17を備え、制御電極25は、導電性窒化物で形成され窒化物絶縁膜17(ゲート絶縁膜)に重ねて配置されている。

(もっと読む)

非対称型半導体デバイス及び製造方法

【課題】 非対称型半導体デバイス、及びその製造の際にスペーサ・スキームを用いる方法を提供する

【解決手段】 高kゲート誘電体の表面上に配置された非対称型ゲート・スタックを含む半構造体が提供される。非対称型ゲート・スタックは、第1の部分と第2の部分とを含み、第1の部分は、第2の部分とは異なる閾値電圧を有する。本発明の非対称型ゲート・スタックの第1の部分は、下から上に、閾値電圧調整材料及び少なくとも第1の導電性スペーサを含み、本発明の非対称型ゲート・スタックの第2の部分は、ゲート誘電体の上の少なくとも第2の導電性スペーサを含む。幾つかの実施形態において、第2の導電性スペーサは、下にある高kゲート誘電体と直接接触しており、他の実施形態においては、第1及び第2の導電性スペーサは、前記閾値電圧調整材料と直接接触している。

(もっと読む)

半導体装置の作製方法

【課題】TFTを用いた半導体装置において、TFT中の汚染不純物を低減し、信頼性のあるTFTを得ることを課題とする。

【解決手段】ガラス基板上のTFTの被膜に存在する汚染不純物を、フッ素を含有する酸性溶液を被膜表面に接触させ、酸性溶液を一定方向に流すことにより、被膜表面の汚染不純物を除去することにより、信頼性のあるTFTを得ることができる。なお、酸性溶液は、フッ酸とフッ化アンモニウムの混合比が体積比で1:50のバッファードフッ酸を用いる。

(もっと読む)

半導体装置及びその製造方法

【課題】高い仕事関数及び高温安定性を備えたメタルゲートを有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート誘電体層108と、ゲート誘電体層108上に形成された酸素を含む合金層110と、酸素を含む合金層110上に形成されたRe層112と、ゲート誘電体層108と酸素を含む合金層110との間に位置するRe酸化物層502を含むp 型電界効果トランジスタを具備する。

(もっと読む)

半導体装置の製造方法

【課題】高誘電率ゲート絶縁膜及びメタルゲート電極を備えたCMISFETの生産性や性能を向上させる。

【解決手段】半導体基板1の主面にゲート絶縁膜用のHf含有絶縁膜5を形成し、その上に窒化金属膜7を形成し、窒化金属膜7上のフォトレジストパターンをマスクにしたウェットエッチングによって、nチャネル型MISFET形成予定領域であるnMIS形成領域1Aの窒化金属膜7を選択的に除去する。それから、希土類元素を含有するしきい値調整層8を形成し、熱処理を行って、nMIS形成領域1AのHf含有絶縁膜5をしきい値調整層8と反応させるが、pチャネル型MISFET形成予定領域であるpMIS形成領域1BのHf含有絶縁膜5は、窒化金属膜7があるためしきい値調整層8とは反応しない。その後、未反応のしきい値調整層8と窒化金属膜7を除去してから、nMIS形成領域1AとpMIS形成領域1Bにメタルゲート電極を形成する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】酸化物半導体を用いた好適な構造のnチャネル型トランジスタおよびpチャネル型トランジスタを提供することを目的の一とする。

【解決手段】第1の酸化物半導体層と電気的に接続し、第1の材料を含む第1の導電層と第2の材料を含む第2の導電層の積層構造でなる第1のソース電極またはドレイン電極と、第2の酸化物半導体層と電気的に接続し、第1の材料を含む第3の導電層と第2の材料を含む第4の導電層の積層構造でなる第2のソース電極またはドレイン電極と、を有し、第1の酸化物半導体層には、第1のソース電極またはドレイン電極の第1の導電層が接触し、第2の酸化物半導体層には、第2のソース電極またはドレイン電極の第3の導電層および第4の導電層が接触する。

(もっと読む)

半導体装置およびその製造方法

【課題】特性の劣化を効果的に抑制することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、GaNを含む半導体層1と、電極とを備えている。電極は、電極本体6と、半導体層1から見て電極本体6よりも離れた位置に形成され、かつAlを含む接続用電極8と、電極本体6と接続用電極8との間に形成されたW、TiW、WN、TiN、Ta、およびTaNよりなる群から選ばれる少なくとも1種を含むバリア層7とを含んでいる。バリア層7の表面粗さRMSが3.0nm以下である。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に高抵抗領域及び低抵抗領域を有するバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層の低抵抗領域を介して接触するように薄膜トランジスタを形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】接続する素子の駆動電圧によってトランジスタのドレイン電圧が決定される。トランジスタの小型化にともないドレイン領域に集中する電界強度が高まり、ホットキャリアが生成し易くなる。ドレイン領域に電界が集中し難いトランジスタを提供することを課題の一とする。また、トランジスタを有する表示装置を提供することを課題の一とする。

【解決手段】高い導電率を有する第1配線層および第2配線層の端部とゲート電極層の重なりをなくすことにより、第1電極層及び第2電極層近傍に電界が集中する現象を緩和してホットキャリアの発生を抑制し、加えて第1配線層および第2配線層より高抵抗の第1電極層および第2電極層をドレイン電極層として用いてトランジスタを構成する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層より導電率の高いバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

製造制御装置及び製造制御方法

【課題】膜厚変動を抑制することにより、トランジスタ特性のばらつきを低減できる製造制御装置及び製造制御方法を提供する。

【解決手段】第1半導体ウェハ上に絶縁膜を堆積する成膜装置30を制御する制御パラメータ(堆積時間ttarget)を算出する製造制御装置20であって、第2半導体ウェハの第2ウェハ表面積L1が大きいほど、成膜装置30に絶縁膜を厚く堆積させる制御パラメータ(堆積時間ttarget)を算出する。また、製造制御装置20は、第2ウェハ表面積L1が大きいほど堆積時間ttargetが長くなるように堆積時間ttargetを算出する堆積時間算出部116を備えてもよい。

(もっと読む)

半導体デバイスとその形成方法(高k金属ゲートCMOS)

【課題】 金属酸化膜半導体電界効果トランジスタ内にデバイス性能を改善するゲート構造体を提供する。

【解決手段】 基板のp型デバイス領域の上にGe含有層を形成することを含む、半導体デバイスを形成する方法が提供される。その後、基板の第2の部分内に第1の誘電体層が形成され、基板の第2の部分内の第1の誘電層及び基板の第1の部分の上を覆うように、第2の誘電体層が形成される。次に、基板のp型デバイス領域及びn型デバイス領域の上にゲート構造体を形成することができ、n型デバイス領域へのゲート構造体は希土類金属を含む。

(もっと読む)

221 - 240 / 978

[ Back to top ]