Fターム[4M104BB32]の内容

Fターム[4M104BB32]に分類される特許

141 - 160 / 978

電界効果トランジスタを形成するための方法および電界効果トランジスタ・デバイス

表示装置、電子機器

【課題】アクティブマトリクス型の液晶表示装置の画面の大面積化を可能とするゲート電

極とゲート配線を提供することを第1の課題とする。

【解決手段】同一基板上に表示領域と、表示領域の周辺に設けられた駆動回路と、を有し

、表示領域は、第1の薄膜トランジスタを有し、駆動回路は、第2の薄膜トランジスタを

有し、第1の薄膜トランジスタと第2の薄膜トランジスタは、リンがドープされたシリコ

ンでなるゲート電極を有し、ゲート電極は、チャネル形成領域の外側に設けられた接続部

でアルミニウムまたは銅を主成分とする層とタンタル、タングステン、チタン、モリブデ

ンから選ばれた少なくとも1種を主成分とする層とを有する配線と電気的に接続する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた高性能な半導体装置を提供する。

【解決手段】基板上に酸化物半導体層を形成し、酸化物半導体層上に第1の導電層を形成し、第1の導電層上に第2の導電層を形成し、第2の導電層をエッチングすることで、第1のパターンを形成し、第1のパターンを酸化することにより膨張させ、膨張後の第1のパターンをマスクとして第1の導電層をエッチングすることで、ソース電極及びドレイン電極となる第2のパターンを形成し、膨張後の第1のパターン及び第2のパターン及び酸化物半導体層を覆うゲート絶縁層を形成し、ゲート絶縁層上にゲート電極を形成する。

(もっと読む)

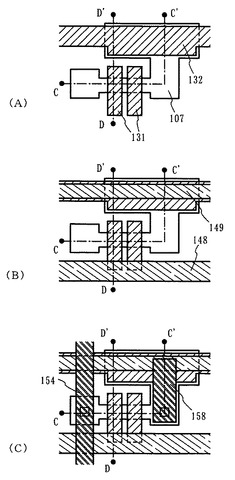

トランジスタ及びその作製方法

【課題】スイッチング特性が良好で、且つ信頼性が高いトランジスタを提供する。

【解決手段】例えば、ボトムゲートトップコンタクト構造のトランジスタを作製するに際して、第1の配線層を形成し、該第1の配線層を覆って第1の絶縁膜を形成し、該第1の絶縁膜上に半導体層を形成し、該半導体層上に導電膜を形成し、該導電膜に少なくとも2段階のエッチングを行って第2の配線層を離間させて形成し、前記2段階のエッチングが、少なくとも前記導電膜に対するエッチングレートが前記半導体層に対するエッチングレートより高い条件により行う第1のエッチング工程と、前記導電膜及び前記半導体層に対するエッチングレートが、前記第1のエッチング工程よりも高い条件により行う第2のエッチング工程と、を有する方法によりトランジスタを作製する。

(もっと読む)

半導体装置の製造方法および基板処理システム

【課題】 液体原料を用いてSi以外の金属膜を安定して成長させる。

【解決手段】 基板上に形成された第1の金属膜の表面を水酸基で終端する第1の前処理を行う工程と、第1の前処理後の第1の金属膜に対して水素含有ガスを供給して第2の前処理を行う工程と、第2の前処理後の第1の金属膜上に第2の金属膜を形成する工程と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクトを備えた半導体装置において、コンタクトホールの開口不良やコンタクト抵抗の増大を防止しつつ、接合リーク電流の発生に起因する歩留まりの低下を防止する。

【解決手段】半導体基板100におけるゲート電極103の両側にソース/ドレイン領域106が形成されている。シェアードコンタクトは、ソース/ドレイン領域106とは接続し且つゲート電極103とは接続しない下層コンタクト113と、下層コンタクト113及びゲート電極103の双方に接続する上層コンタクト118とを有する。

(もっと読む)

薄膜抵抗を備えた半導体装置の製造方法

【課題】薄膜抵抗と配線部との接触抵抗が高抵抗化することを抑制できる薄膜抵抗を備えた半導体装置の製造方法を提供する。

【解決手段】スパッタ装置内において事前にチタンの表面を窒化させておくことで窒化チタンを形成しておき、その後、窒素の導入を停止した状態で窒化チタンをターゲットとしたスパッタにより、窒化チタン膜によって構成される第1金属層5を形成する。これにより、薄膜抵抗Rと接触する第1金属層5を形成する際に、スパッタ装置内に窒化ラジカルが基本的には存在していない条件で第1金属層5の成膜を行うことができるため、薄膜抵抗Rの露出部分に窒化物が形成されないようにできる。したがって、薄膜抵抗Rと配線部の一部を構成する第1金属層5との接触抵抗が高抵抗化することを抑制することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の表皮効果の抑制と低抵抗化を図る。

【解決手段】第1配線部41と、その第1配線部41の周りを被覆する、高融点金属窒化物を含む第2配線部42とを含む配線40aを形成する。このような配線40aにおける第2配線部42は、第1配線部41側から外周に向かって窒素含有率が高くなる部分を有するように形成する。これにより、配線40aにおける表皮効果が抑制されると共に、配線40aの低抵抗化が図られるようになる。

(もっと読む)

半導体装置およびその製造方法

【課題】閾値電圧が低く、かつ、ゲート絶縁膜のリーク電流を抑制可能な半導体装置およびその製造方法を提供する。

【解決手段】メタルゲート電極103,203の材料として、Ta3N5を含むTaxNy膜18,38を用いる。TaxNy膜18,38中には多くの窒素が含まれており、その窒素の一部がゲート絶縁膜102,202中に拡散することにより、TiNに比べてフラットバンド電圧Vfbが高くなり、NMOSFET100およびPMOSFET200の閾値電圧Vthを低くすることができる。また、TaxNy膜18,38中の窒素がHfSiON膜17,37中に拡散することにより、ゲート絶縁膜の絶縁性を高くすることができ、ゲートリーク電流Jgを抑制できる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】耐圧の異なるトランジスタが同一半導体基板上に混載されている場合においても、それらのトランジスタの性能が向上するようにストレスライナ膜を構成することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に混載された低耐圧トランジスタおよび高耐圧トランジスタ上に形成するストレスライナ膜11、12は、互いに膜質を異ならせることができる。ここで、ストレスライナ膜11は、低耐圧トランジスタの性能が効果的に改善され、高耐圧トランジスタの性能があまり改善されないように膜質を設定することができる。また、ストレスライナ膜11は、高耐圧トランジスタの性能が効果的に改善され、低耐圧トランジスタの性能があまり改善されないように膜質を設定することができる。

(もっと読む)

酸化表面層のハイブリッドその場ドライクリーニングプロセス

【課題】 集積回路における酸化表面層の洗浄を行うための新しいドライクリーニングプロセスの提供。

【解決手段】 一の実施例によると、当該方法は、酸化表面層を有する金属含有バリア層を含む基板を供する工程、前記酸化表面層を活性化させるために、プラズマ励起されたアルゴン気体を含む第1処理気体流へ前記酸化表面層を曝露する工程、及び、前記の第1処理気体流へ酸化表面層を曝露する工程中に基板バイアス電力を印加する工程を有する。当該方法は、非プラズマ励起された水素気体を含む第2処理気体へ前記の活性化した酸化表面層を曝露する工程をさらに有する。前記の第1処理気体流へ酸化表面層を曝露する工程は、前記酸化表面層を活性化させるのに加えて、水素気体を含む前記第2処理気体による、前記活性化した酸化表面層の還元を助ける。前記金属含有バリア層の厚さは、ハイブリッドその場ドライクリーニングプロセスによって実質的には変化しない。

(もっと読む)

半導体トランジスタの製造方法

【課題】プロセスの自由度を高めつつ、活性層とオーミックコンタクトをとるオーミック電極を形成できる半導体トランジスタの製造方法を提供する。

【解決手段】GaN系の半導体からなる活性層上に、オーミック電極を形成する半導体トランジスタの製造方法であって、活性層3上に、タンタル窒化物からなる第1の層11と、第1の層11上に積層されたAlからなる第2の層12とを形成する工程と、第1及び第2の層11,12を、520℃以上、600℃以下の温度で熱処理することにより、活性層3とオーミックコンタクトをとるオーミック電極9s,9dを形成する工程とを備える。

(もっと読む)

半導体処理システムのための前駆物質を生成する方法及び装置

【課題】半導体処理システム(320)の前駆物質を生成する装置を提供する。

【解決手段】装置は、側壁(402)、上部、底部を有するキャニスタ(300)を含んでいる。キャニスタ(300)は、上の領域(418)と下の領域(434)を有する内容積(438)を画成している。一実施形態においては、装置は、更に、キャニスタ(300)を部分的に取り囲んでいるヒータ(430)を含んでいる。ヒータ(430)によって、上の領域(418)と下の領域(434)間に温度勾配が生じる。また、精製ペンタキス(ジメチルアミド)タンタルから原子層堆積によってバリヤ層、例えば、窒化タンタルバリヤ層を形成する方法も特許請求される。

(もっと読む)

半導体装置

【課題】メタルゲート電極内に基板面に対して平行な金属とシリコンなどとの境界又はシリサイドとシリコンなどとの境界を含むメタルゲート電極において、トランジスタの接続抵抗が小さく、高速動作時のトランジスタの遅延又はトランジスタ特性のばらつきなどの特性劣化の懸念がなく、且つ、低コストな構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に、ゲート絶縁膜105と、pMIS用金属材料109又はnMIS用金属材料111と、ゲート電極材料112と、ゲート側壁メタル層122とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】適切な仕事関数を有する金属ゲート電極を備え、トランジスタ特性のばらつきが抑えられた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1001と、半導体基板1001内に形成された第1導電型の第1の活性領域1003と、第1の活性領域1003上に形成された第1のゲート絶縁膜1030aと第1のゲート電極1032aとを有し、第1の活性領域1003上に形成された第1チャネル型の第1のMISFET1050とを備える。第1のゲート電極1032aは、第1のゲート絶縁膜1030a上に形成され、金属原子を含む第1の下部ゲート電極1011aと、炭素の単体を含む材料、または分子中に炭素を含む材料からなる第1の酸化防止膜1012aと、第1の上部ゲート電極1013aとを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】バリアメタルの膜厚を抑制しながらメタルゲートの拡散性材料が高誘電率誘電体に拡散することを防ぐ。

【解決手段】半導体装置がゲート積層体構造を含む。ゲート積層体構造は、半導体基板5の上に形成された界面層4と、界面層4の上に形成された高誘電率誘電体3と、拡散性材料と不純物金属を含み、高誘電率誘電体の上方に形成されたシリサイドゲート1と、拡散性材料に対するバリア効果を持ち、高誘電率誘電体3とシリサイドゲート1の間に形成されたバリアメタル2とを備えている。不純物金属は、シリサイドゲート1の拡散性材料が高誘電率誘電体に導入されることを防ぐことができるような、拡散性材料に対するバリア効果を有している。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、ソース電極及びドレイン電極は、第1の導電層と、第1の導電層の端部よりチャネル長方向に伸長した領域を有する第2の導電層と、を含む半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】マイクロローディング効果を防止しながら、上層配線となる金属配線のレイアウト制約のない構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3の上に形成されたゲート電極4と、半導体基板1に形成された拡散層5と、半導体基板1の上に形成された絶縁膜7及び絶縁膜8と、絶縁膜及び絶縁膜8を貫通するホール9Dに埋め込まれ、側面を絶縁膜11で覆われた金属材料からなるプラグ12と、絶縁膜8を貫通しないホール10Bに埋め込まれ、絶縁膜11からなる絶縁体10Cと、絶縁膜8の上に形成され、プラグ12と電気的に接続する金属配線13Bとを備えている。

(もっと読む)

表示装置の作製方法

【課題】液滴吐出法により吐出する液滴の着弾精度を飛躍的に向上させ、微細でかつ精度の高いパターンを基板上に直接形成することを可能にする。もって、基板の大型化に対応できる配線、導電層及び表示装置の作製方法を提供することを課題とする。また、スループットや材料の利用効率を向上させた配線、導電層及び表示装置の作製方法を提供することを課題とする。

【解決手段】液滴吐出法による液滴の吐出直前に、所望のパターンに従い基板表面上の液滴着弾位置に荷電ビームを走査し、そのすぐ後に該荷電ビームと逆符号の電荷を液滴に帯電させて吐出することによって、液滴の着弾位置の制御性を格段に向上させる。

(もっと読む)

積層膜の形成方法

【課題】 各膜の組成が異なる積層膜を、極めて効率よく、しかも酸化等の不都合が生じることなく形成することができる積層膜の形成方法を提供すること。

【解決手段】 処理室内に基板1を配置し、処理室に、少なくとも、金属カルボニルを含有する原料を含む成膜原料を導入し、CVDにより基板1上に金属カルボニル中の金属を含む複数の膜6a、6bを含む積層膜を形成する積層膜の形成方法であって、上記積層膜に含まれる膜は、同一処理室内で、原料種および/または成膜条件を異ならせて連続成膜され、上記膜の組成が異なる積層膜を形成する。

(もっと読む)

141 - 160 / 978

[ Back to top ]