Fターム[4M104BB32]の内容

Fターム[4M104BB32]に分類される特許

181 - 200 / 978

半導体装置及びその製造方法

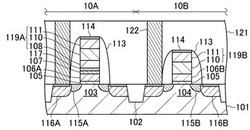

【課題】デュアルメタルゲートプロセスを用いることなく、p型MISトランジスタ及びn型MISトランジスタ双方の特性を向上した半導体装置を実現できるようにする。

【解決手段】半導体装置は、p型半導体領域10Aの上に順次形成された第1の界面シリコン酸化膜105、アルミニウムを含む第1のゲート絶縁膜106A及び第1のゲート電極119Aと、n型半導体領域10Bの上に順次形成された第2の界面シリコン酸化膜105、実効仕事関数を低下させる効果を有する元素を含む第2のゲート絶縁膜106B及び第2のゲート電極119Aとを備えている。第1のゲート絶縁膜106Aの上部におけるアルミニウムの濃度は、1×1020/cm3以上である。第2のゲート絶縁膜106Bの上部におけるアルミニウムの濃度は、1×1019/cm3以下である。第1の界面シリコン酸化膜105の膜厚と第2の界面シリコン酸化膜105の膜厚との差は0.2nm以下である。

(もっと読む)

PMOSデバイスのゲートスタックのしきい値電圧を調整する方法

【課題】本発明は、半導体基板上にゲート誘電体層とゲート電極とのゲートスタックを含む半導体デバイスを製造する方法であって、ゲートスタックのVT値を容易に調整することができる方法を提供する。

【解決手段】ゲート誘電体層とゲート電極とのゲートスタックを含む半導体デバイスを製造する方法は、第1の電気陰性度を有する金属酸化物または半金属酸化物であるゲート誘電体層を半導体基板上に形成するステップと、第2の電気陰性度を有する金属酸化物または半金属酸化物である誘電体VT調整層を形成するステップと、ゲート誘電体層およびVT調整層の上にゲート電極を形成するステップと、を含み、前記ゲートスタックの実効仕事関数が、誘電体VT調整層の厚さおよび組成を調整することによって所望の値に調整され、第2の電気陰性度が、第1の電気陰性度およびAl2O3のいずれよりも高い。

(もっと読む)

半導体装置

【課題】半導体層と電極の接続部に生じる寄生抵抗を抑制し、配線抵抗による電圧降下の影響や画素への信号書き込み不良や階調不良などを防止し、より表示品質の良い表示装置を代表とする半導体装置を提供することを課題の一つとする

【解決手段】上記課題を解決するために、本発明は酸素親和性の強い金属を含むソース電極、及びドレイン電極と、不純物濃度を抑制した酸化物半導体層とを接続した薄膜トランジスタと、低抵抗な配線を接続して半導体装置を構成すればよい。また、酸化物半導体を用いた薄膜トランジスタを絶縁膜で囲んで封止すればよい。

(もっと読む)

半導体装置及びその製造方法

【課題】 高信頼性を有するデュアルダマシン構造を用いた半導体装置及びその製造方法を提供することができる。

【解決手段】 半導体基板上に形成された第一の絶縁膜と、前記第一の絶縁膜に形成されたコンタクトと、前記第一の絶縁膜上に形成され、前記第一の絶縁膜よりも誘電率の低い第二の絶縁膜と、前記第二の絶縁膜に形成され、前記コンタクトと電気的に接続される配線とを備え、前記コンタクト底面及び、前記配線の側面に第一のバリアメタルが形成され、前記コンタクト側面及び前記第一のバリアメタル上に第二のバリアメタルが形成されている。

(もっと読む)

高電子移動度トランジスタの構造、その構造を含んだデバイス及びその製造方法

【課題】MMICのSPDTスイッチなど、半導体デバイスとして用いるのに適したMOS−PHEMTの構造及びその製造方法を開示する。

【解決手段】MOS−PHEMT構造は、Al2O3、HfO2、La2O3及びZrO2からなる群から選ばれる材料からなるゲート誘電体層107を有することを特徴とし、これにより、このMOS−PHEMTの構造を含む、高周波スイッチデバイスなどの半導体構造が、直流電流の損失及び挿入損失の低下を防ぎ、隔絶性を向上させることができる。

(もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置

【課題】MIPS構造を採るメタル膜とコンタクトプラグとの界面抵抗を低減できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を形成し、形成したゲート絶縁膜3の上に、TiN膜4及びポリシリコン膜5を順次形成する。続いて、ポリシリコン膜5にTiN膜4を露出するコンタクトホール5aを形成する。続いて、ポリシリコン膜5における第1のコンタクトホール5aの少なくとも底面及び壁面上に金属膜7を形成する。

(もっと読む)

半導体ウェハ上に銅層を形成する方法

【課題】アスペクト比の高い開口部内に空隙を形成することなく銅層を埋め込むことの可能な電気めっき方法を提供すること。

【解決手段】ウェハ上に銅層を形成する方法は、制御システムを有する電気めっきチャンバ内にウェハを配置する段階と、第1期間302の間にウェハに対する第1電力を正にパルス化する段階と、第1期間302に続く第2期間304の間にウェハに対する第2電力を負にパルス化する段階と、第2期間304に続く第3期間306の間にウェハに対する第3電力を正にパルス化する段階とを備える。

(もっと読む)

PFETチャネルSiGeを有する金属ゲート及び高k誘電体デバイス

【課題】SiGeから成るチャネルを有し、金属ゲート及び高kゲート誘電体を有するPFETを提供する。

【解決手段】Si表面上にSiGe層10をエピタキシャル成長させ、SiGe層の上に、高k誘電体及び金属をブランケット配置し、ゲートスタックを形成した後、NFET側のゲート誘電体、及びSiGe層を除去し、第2の高k誘電体53及び第2の金属52を配置する。PFETは、SiGeチヤネル10の上の高k誘電体を有するゲート誘電体、金属を有するゲート及び、シリサイドを有するソース、ドレインから成る。NFETは、第2の高k誘電体53、第二の金属52を有するゲート及び、シリサイドを有するソース、ドレインからなる。基板表面上のエピタキシャルSiGe層は、PFETのチヤネルのみに形成される。PFET及びNFETデバイス・パラメータは、各ゲート誘電体及びゲートスタックの組成によって別個に最適化することができる。

(もっと読む)

酸素拡散バリア層を有する半導体デバイスおよびそれを製造するための方法

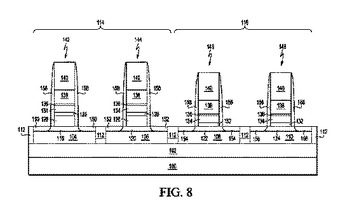

方法および装置はトランジスタを製造するために提供される。トランジスタが、半導体材料104、106、108、110上に配置されたゲートスタック142、144、146を備える。ゲートスタックが、半導体材料上に堆積される酸化物層126、堆積された酸化物層上に配置された酸素拡散バリア層128、酸素拡散バリア層上に配置された高誘電率の誘電体層134、および高誘電率の誘電体層上に配置された酸素ゲッター導電性層138を備える。酸素拡散バリア層が、堆積された酸化物層から酸素ゲッター導電性層への酸素の拡散を防止する。  (もっと読む)

(もっと読む)

半導体デバイスおよびその製造方法

【課題】複数ゲートトランジスタの改良された構造、およびその製造プロセスの提供。

【解決手段】相補型金属酸化膜半導体(CMOS)デバイス100は、第1のパラメータを有する少なくとも2つの第1のゲート電極を備えたPMOSトランジスタと、上記第1のパラメータとは異なる第2のパラメータを有する少なくとも2つの第2のゲート電極を備えたNMOSトランジスタと、を有している。上記第1のパラメータおよび上記第2のパラメータは、上記PMOSおよびNMOSトランジスタの上記ゲート電極材料120の厚さ、またはドーパントプロファイルを含んでいる。上記少なくとも2つの第1のゲート電極および上記少なくとも2つの第2のゲート電極の上記第1および第2のパラメータは、それぞれ、上記PMOSおよびNMOSトランジスタの仕事関数を規定する。

(もっと読む)

半導体ウェハ上に銅層を形成する方法

【課題】めっき動作を動的に制御することの可能な電気めっき方法を提供すること。

【解決手段】ウェハ20上に銅層を形成する方法は、ウェハ20を電気めっきチャンバ10内に配置する段階であって、電気めっきチャンバ10が少なくとも一つの電気コンタクト18を通じてウェハ20に電気的に接続される制御システム34を有し、制御システム34がウェハ20に電力を提供する、段階と、ウェハ20に給電して、ウェハ20上に銅を電気めっきする段階と、電気めっき中にウェハ20の電気特性を監視して、電気めっきチャンバ10内の条件を変更すべきときを判断する段階とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積なSGTを用いたCMOSインバータ回路からなる半導体装置を提供する。

【解決手段】第1のトランジスタは、島状半導体層と、島状半導体層の周囲を取り囲む第1のゲート絶縁膜と、第1のゲート絶縁膜の周囲を取り囲むゲート電極と、島状半導体層の上部に配置された第1の第1導電型高濃度半導体層と、島状半導体層の下部に配置された第2の第1導電型高濃度半導体層とを有し、第2のトランジスタは、ゲート電極の周囲の一部を取り囲む第2のゲート絶縁膜と、第2のゲート絶縁膜の周囲の一部に接する第2の半導体層と、第2の半導体層の上部に配置され、第1導電型高濃度半導体層と反対の極性を有する第1の第2導電型高濃度半導体層と、第2の半導体層の下部に配置され、第1導電型高濃度半導体層と反対の極性を有する第2の第2導電型高濃度半導体層とを有することにより、上記課題を解決する。

(もっと読む)

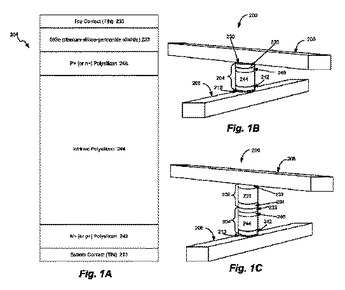

低コンタクト抵抗を有する3次元ポリシリコンダイオードおよびその形成方法

半導体p−i−nダイオードおよび半導体p−i−nダイオードを形成する方法を開示する。一形態において、一の導電型(p+またはn+の一方)を有するようにドープされた領域と、p−i−nダイオードへの電気コンタクトの間に、SiGe領域が形成される。SiGe領域は、コンタクト抵抗を低減する働きをすることができ、順バイアス電流を増加させることができる。ドープされた領域は、ドープされた領域がSiGe領域とダイオードの真性領域との間に存在するように、SiGe領域の下方を伸びている。p−i−nダイオードは、シリコンから形成することができる。SiGe領域の下方のドープされた領域は、付加されたSiGe領域によって逆バイアス電流が増加することを防止する働きをすることができる。一実施形態では、メモリアレイ内の上向きのp−i−nダイオードの順バイアス電流が、下向きのp−i−nダイオードの順バイアス電流に実質的に一致するように、SiGeは形成される。これらのダイオードが3Dメモリアレイの読み出し/書き込み材料に用いられた場合に、より良いスイッチング結果を達成することができる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】炭化珪素(SiC)半導体装置において、SiC基板との良好なオーミック特性が得られると共に、密着性および耐久性に優れた裏面電極を提供する。

【解決手段】SiC半導体装置は、SiC基板1の裏面に形成されたニッケル膜3を含む裏面電極11と、SiC基板1とニッケル膜3との間に介在し、開口部2aを有するバリア膜2とを備える。SiC基板1とニッケル膜3との間においては、バリア膜2の開口部2aの部分に、ニッケルシリサイドの反応層4が形成されている。

(もっと読む)

真空加熱装置及び基板処理システム

【課題】基板に均一性高い加熱処理を行う一方で、高い真空度が得られる真空加熱装置を提供すること。

【解決手段】本発明の真空加熱装置は、気密な処理容器と、この処理容器内に基板を載置するために設けられたアルミニウム合金からなる載置台と、この載置台を支持し、その内部に用力線路部材が大気側から挿入されているステンレス鋼からなる筒状の支持部材と、この支持部材と処理容器との間を気密にするための有機物からなるシール部材と、前記載置台を加熱するための加熱部と、前記処理容器内を真空排気するための真空排気手段と、を備えている。これによって載置台の熱が支持部材を介してシール部材に伝熱し難くなっており、シール部材の昇温が抑えられ、大気側から大気成分がシール部材を通って処理容器内へ侵入することが抑えられる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート構造としてメタル電極/High−k膜構造を用いた半導体装置において、仕事関数の制御とEOTの薄膜化とを両立させる。

【解決手段】半導体基板101におけるnチャネルMISトランジスタ形成領域の上に、ゲート絶縁膜として、第1の高誘電率絶縁層202、アルミニウム含有層203、ランタン含有層204及び第2の高誘電率絶縁層205を順次形成する。その後、ゲート電極形成を行う。

(もっと読む)

半導体装置の製造方法、基板処理装置及び半導体装置

【課題】 緻密で原料起因の不純物濃度が低く抵抗率が低い導電性膜を、速い成膜速度で形成する半導体装置の製造方法および基板処理装置を提供することである。

【解決手段】 2種類以上の原料を処理室内に同時に供給し、処理室内に載置された基板上に膜を形成する半導体装置の製造方法であって、少なくとも1種の原料を第1の供給量で処理室内に供給する第1の原料供給工程と、この少なくとも1種の原料を第1の供給量とは異なる第2の供給量で処理室内に供給する第2の原料供給工程と、を有する。

(もっと読む)

スパッタリングターゲットの製造方法及びスパッタリングターゲット

【課題】半導体素子などに用いられるCu配線のバリア層の形成に好適なスパッタリングターゲットの製造方法及びスパッタリングターゲットを提供する。

【解決手段】粗金属Taをエレクトロンビーム溶解して高純度Taインゴットを精製する工程と、得られた高純度Taインゴットに対して鍛造、圧延による塑性加工を施す工程と、塑性加工を施した前記高純度Taインゴットに熱処理を施す工程と、を有することを特徴とするスパッタリングターゲットの製造方法、及びパッタリングターゲット。

(もっと読む)

半導体発光素子、その製造方法、ランプ、電子機器及び機械装置

【課題】金属反射層の構成材料の拡散を防止することが可能な電極を備えた半導体発光素子、その製造方法、ランプ、電子機器及び機械装置を提供することを目的とする。

【解決手段】基板101と、基板101上にn型半導体層104と発光層105とp型半導体層106とがこの順序で積層されてなる積層半導体層20と、p型半導体層106に接合された一方の電極111と、n型半導体層104に接合された他方の電極108と、を具備する半導体発光素子であって、一方の電極111または他方の電極108のいずれか一方または両方が、第1の拡散防止層51と金属反射層52と第2の拡散防止層53がこの順序で積層されてなる構造を有し、かつ、第1の拡散防止層51がIn、Zn、Al、Ga、Ti、Bi、Mg、W、Ce、Sn、Niのいずれかの金属を含む酸化物からなる半導体発光素子1を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置

【課題】画素TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現し、信頼性と生産性を向上させる技術を提供することを課題とする。

【解決手段】画素領域に形成する画素TFTをチャネルエッチ型の逆スタガ型TFTで基板上に形成し、ソース領域及びドレイン領域のパターニングと画素電極のパターニングを同じフォトマスクで行う。また、ソース配線を画素電極と同じ材料である導電膜で覆い、基板全体を外部の静電気等から保護する構造とする。このような構成とすることで、製造工程において製造装置と絶縁体基板との摩擦による静電気の発生を防止することができる。特に、製造工程で行われる液晶配向処理のラビング時に発生する静電気からTFT等を保護することができる。

(もっと読む)

181 - 200 / 978

[ Back to top ]