Fターム[4M104DD09]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | コンタクトホール又は電極析出部の形成 (4,254) | 孔開け、又は絶縁膜の除去方法 (1,213) | ウェットエッチ (218)

Fターム[4M104DD09]の下位に属するFターム

サイドエッチの利用 (28)

Fターム[4M104DD09]に分類される特許

161 - 180 / 190

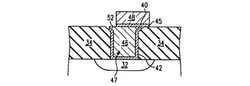

包囲条件を除去するためのプラグの拡大頭部を形成する構成体及び方法

【課題】 相互接続層を形成する場合に侵食されることのないコンタクト開口を形成する技術を提供する。

【解決手段】 絶縁層(34)を貫通するコンタクト開口が真直な側壁部分(42)とお椀形状側壁部分(40)とを有するように形成される。お椀形状側壁部分は絶縁層の上部近くであり底部と比較して上部においてコンタクト開口の拡大直径部分を与えている。導電性物質(46)をコンタクト開口内に形成し下部の導電層(32)と電気的接触を形成する。この導電性物質は拡大頭部(52)を有するプラグ(47)を形成する。この拡大頭部は、存在する場合に、コンタクト開口内のバリア層(45)が爾後の異方性エッチングによってエッチングされることを防止する。従って、例えばアルミニウム等の電気的相互接続層(48)がコンタクトプラグの上側に形成される場合に、そのプラグはエッチストップとして作用しコンタクト開口内のバリア層がエッチングされることを防止する。

(もっと読む)

半導体装置の製造方法

【課題】スルーホールに収容されるプラグと、その下部の導体パターンとの間のコンタクト抵抗を低減可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置10の製造方法は、半導体基板上に絶縁膜(15,16,21)を形成するステップと、異方性エッチングによって絶縁膜の上部分(16,21)にスルーホールの上部分22を形成するステップと、スルーホールの上部分22の側壁にエッチ保護膜23を形成するステップと、絶縁膜の下部分(15)に、スルーホールの上部分22に連続するスルーホールの下部分24を等方性エッチングによって形成するステップとを有する。

(もっと読む)

半導体デバイス用の自己整合ショットキー接合の形成方法

半導体デバイスに対し、自己整合ショットキー接合(29)を形成する方法である。ゲートエッチング及びスペーサ形成の後、接合領域を画成する凹所を半導体基板(10)に形成し、そこに、SiGe層(22)を選択的に成長させる。その後、誘電体層(24)をゲート(14)及びSiGe層(22)の上に設け、コンタクトエッチングを行って、コンタクトホール(26)を形成してから、SiGeの材料(22)を除去して、接合領域にキャビティ(28)を作成する。最後に、キャビティ(28)を金属で満たして、接合(29)を形成する。このようにして、抵抗率が比較的低く、形状及び位置を良好に制御することができる、ショットキー接合を自己整合で形成する方法が提供される。  (もっと読む)

(もっと読む)

半導体素子の製造方法

【課題】金属シリサイド膜を有する半導体素子の製造方法を提供する。

【解決手段】半導体基板100上にゲートスタック110が配置され、基板100の上部及びゲートスタック110の側壁にゲートスペーサ膜120が配置され、ゲートスタック120の間に絶縁膜130が配置される構造体を形成する。絶縁膜130を取り除いてゲートスペーサ膜120を露出させる。ゲートスペーサ膜120上に犠牲絶縁膜を形成する。ゲートスタック120側壁のゲートスペーサ膜120上の犠牲絶縁膜は残り、基板100上部のゲートスペーサ膜120上の犠牲絶縁膜は取り除かれるように犠牲絶縁膜の一部を取り除く。基板100上のゲートスペーサ膜120を取り除き、ゲートスタック120の間の基板100を露出させる。ゲートスタック120の間の基板100の露出面上に金属シリサイド膜を形成する。

(もっと読む)

逆ソース/ドレイン金属コンタクトを有する電界効果トランジスタ(FET)及びその製造方法

【課題】 コンタクト間隔及び寄生容量の問題に対する解決策を提供する、改善されたFET設計を構築する。

【解決手段】 本発明は、下方の第1の誘電体層内に配置された下部と上方の第2の誘電体層内に配置された上部とを有する逆ソース/ドレイン金属コンタクトを含む電界効果トランジスタ(FET)に関する。逆ソース/ドレイン金属コンタクトの下部は、上部より大きい断面積を有する。好ましくは、逆ソース/ドレイン金属コンタクトの下部は、約0.03μm2から約3.15μm2の範囲の断面積を有し、こうした逆ソース/ドレイン金属コンタクトは、約0.001μmから約5μmの範囲の距離だけ、FETのゲート電極から間隔を空けて配置される。

(もっと読む)

バリア性向上のための酸素/窒素遷移領域を含むメッキシード層

【課題】 別個の拡散層及びシード層を利用する必要性を排除した、導電性材料、好ましくはCuの、向上した拡散特性を有するメッキシード層を含む相互接続構造体を提供すること。

【解決手段】 特に、本発明は、相互接続金属の拡散特性向上のためにメッキシード層内に酸素/窒素遷移領域を設ける。メッキシード層はRu、Ir又はそれらの合金を含むことができ、相互接続導電性材料は、Cu,Al、AlCu、W、Ag、Auなどを含むことができる。好ましくは、相互接続導電性材料はCu又はAlCuである。より詳細に言えば、本発明は、上部及び底部シード領域間に挟持された酸素/窒素遷移領域を含む単一のシード層を提供する。メッキシード層内に酸素/窒素遷移領域が存在することで、メッキシードの拡散バリア抵抗が顕著に向上する。

(もっと読む)

半導体装置の製造方法

【課題】 コンタクトパッドを形成する半導体装置の製造方法において、隣接する半導体素子間のショートを防止する。

【解決手段】 シリコン基板11上に、それぞれが金属層15を含むゲート電極17とゲート電極17を覆うゲート側壁絶縁膜20とを有する複数のゲート電極構造体を形成する工程と、ゲート電極構造体を覆って全面にポリシリコン膜を堆積する工程と、ポリシリコン膜をパターニングし、隣接する2つのゲート電極構造体の間でシリコン基板11に接続するコンタクトパッド22を形成する工程(図3(g))と、ゲート側壁絶縁膜のくぼみ21に残留するポリシリコン24を酸化させて酸化シリコン25に形成する工程(図3(h))とをこの順に有する。

(もっと読む)

半導体装置の製造方法

【課題】本発明の目的は、シリサイドブロック層の形成時におけるサイドウォール用絶縁膜の膜厚の減少を抑制することができ、ゲート電極のエッチングやサイドウォール幅のばらつきの発生を抑制することができる半導体装置の製造方法を提供することにある。

【解決手段】基板1上にゲート電極4を形成し、ゲート電極4を被覆するように基板1上にサイドウォール用絶縁膜10およびエッチングストッパ膜20を形成する。次に、エッチングストッパ膜20上にシリサイドブロック用の絶縁層30aを形成し、絶縁層30aを加工して、シリサイド化を防止する領域にシリサイドブロック層30を形成する。シリサイドブロック層30から露出したエッチングストッパ膜20を除去し、サイドウォール用絶縁膜10をエッチバックして、ゲート電極の両側にサイドウォールを形成する。そして、サイドウォールから露出した基板の表面にシリサイド層を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】電気的な接続の信頼性が確保される半導体装置とその製造方法を提供する。

【解決手段】ガラス基板1の表面上に1対のソース・ドレイン領域4a,4bが形成された島状シリコン層4が形成されている。島状シリコン層4上に絶縁膜5を介在させてゲート電極6が形成され、そのゲート電極6を覆うように層間絶縁膜7が形成されている。層間絶縁膜7および絶縁膜5にコンタクトホール9が形成され、そのコンタクトホール9内にプラグ10a,10bが形成されている。コンタクトホール9は、島状シリコン層4を貫通するように形成され、島状シリコン層4を貫通するコンタクトホール9aと、コンタクトホール9aよりも大きい開口断面積を有するコンタクトホールの部分9bとにより構成される。コンタクトホール9内に露出した島状シリコン層4の部分に高濃度領域4dが形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化に対して有利な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板の主表面中に設けられた第1絶縁膜21と、前記第1絶縁膜上に設けられ前記第1絶縁膜の構成元素と所定の金属元素との化合物を主成分とし前記第1絶縁膜よりも比誘電率が高い第1高誘電体膜22−1とを少なくとも備えたゲート絶縁膜12と、前記ゲート絶縁膜上に設けられ、CuまたはCuを主成分とするゲート電極13と、前記ゲート電極を挟むように前記半導体基板中に隔離して設けられたソースまたはドレイン15とを具備する。

(もっと読む)

パターンの形成方法及び液滴吐出ヘッド

【課題】 パターン形成において、低コスト化及び形成時間の短縮化を図るとともに、微細パターンの形成を可能としたパターンの形成方法を提供する。

【解決手段】 本発明のパターン形成方法は、基板18上に第1金属膜28を形成する第1金属膜形成工程と、第1金属膜28上に、パターンを形成しない基板18上の位置に対応する第1金属膜28が露出するようにマスクパターン38を形成するマスクパターン形成工程と、マスクパターン38をマスクとして第1金属膜28上に絶縁膜40を形成する絶縁膜形成工程と、マスクパターン38を除去し、メッキ法により、マスクパターン38を除去した第1金属膜28上に絶縁膜40をマスクとして少なくとも第2金属膜42を形成する第2金属膜形成工程と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】亀裂の無い厚いPSG膜を単層で形成し、低コストで高信頼性の半導体装置およびその製造方法を提供する。

【解決手段】450nm以上の段差T1のある酸化膜5の下地を、リン濃度が2molwt%〜5molwt%で膜厚T1が1.3μm以上の単層のPSG膜7で被覆する。リン濃度を2molwt%〜5molwt%とすることで、下地の段差T1が450nm以上あり、単層のPSG膜の厚さW1が1.3μm以上あった場合でも、高温熱処理によるPSG膜の収縮時に亀裂が発生するのを防止できる。

(もっと読む)

炭化珪素半導体装置及びその製造方法

【課題】基板裏面に極めて低抵抗のオーミックコンタクトを有する縦型パワー炭化珪素半導体装置及びその製造方法を提供する。

【解決手段】平板なSiC基板1の第1の主面側に主要な構成部分を設け、第1の主面の裏面である第2の主面側に少なくとも1つの熱処理型オーミック電極9を設けてなるSiC半導体装置において、熱処理型オーミック電極9は、第2の主面の表層に高温イオン注入で形成された、平坦かつ低抵抗な高濃度不純物領域4に接している。

(もっと読む)

接触形成前に実施する表面の下処理法

【課題】熱伝導性に優れた半導体材料を使用可能で、生産性に優れた半導体デバイスの製造方法を提供する。

【解決手段】リン化インジウム材料に高濃度のシリコンをドーピングしたサブコレクタ層12上にパッシベーション層14が形成される。パッシベーション層14の一部をエッチングにより除去して接触領域を露出させる。露出させた接触領域にエネルギー照射を行い、エネルギー照射を行った部分に低抵抗のオーム接触金属51を堆積する。その後、フォトレジスト21、22を、フォトレジスト22上に堆積した金属51と共に除去する。エネルギー照射としては、不活性材料を使用したスパッタリング処理、化学的に活性を有するイオンを使用したスパッタリング処理、イオンミリング、及びプラズマエッチングのうちのいずれかを利用できる。

(もっと読む)

薄膜トランジスタ回路とその製造方法

【課題】本発明は、単位面積当たりの集積度の高いCMOS構造薄膜トランジスタ回路及びその製造方法を提供する。

【解決手段】本願発明は、基板(2)上に配置された第1の半導体層(4)と、前記第1の半導体層上(4)に第1のゲート絶縁層(5)を介して配置されたゲート電極(6)と、前記ゲート電極(6)上に第2のゲート絶縁層(7)を介して配置された第2の半導体層(8)を備え、前記第2の半導体層(8)のソース領域(8s)及びドレイン領域(8d)が、前記第1の半導体層(4)のソース領域(4s)及びドレイン領域(8d)と重なるように構成された積層型薄膜トランジスタ回路に関し、特に平面表示装置に用いられた場合に、面積として従来比70%以下の狭小化が達成できる。

(もっと読む)

半導体装置の製造方法

【課題】薄膜化された半導体層を貫通することなく、良好な形状のコンタクトホールを形成することができる半導体装置の製造方法を提供する。

【解決手段】絶縁層8の上に設けられた半導体層10に絶縁ゲート電界効果型トランジスタ20を形成すること、前記絶縁ゲート電界効果型トランジスタ20を覆う層間絶縁層30に、前記絶縁ゲート電界効果型トランジスタ20のソース領域またはドレイン領域となる不純物領域28と接続されるコンタクト層38を形成すること、を含み、前記層間絶縁層30はエッチング速度の異なる積層膜32,34で形成し、所定のパターンのマスク層50を用いて第1エッチングを行い、前記不純物領域28の表面が露出しないような凹部36aを形成した後、該不純物領域28の表面が露出するまで等方性エッチングである第2エッチングを行うことでコンタクトホール36を形成すること、を含む半導体装置の製造方法。

(もっと読む)

荷電ビームを用いた液滴吐出装置及び該装置を用いてのパターンの作製方法

液滴吐出法により吐出する液滴の着弾精度を飛躍的に向上させ、微細でかつ精度の高いパターンを基板上に直接形成することを可能にする。もって、基板の大型化に対応できる配線、導電層及び表示装置の作製方法を提供することを課題とする。また、スループットや材料の利用効率を向上させた配線、導電層及び表示装置の作製方法を提供することを課題とする。本発明は、主に絶縁表面を有する基板上において、液滴吐出法によってレジスト材料或いは配線材料等を直接パターニングを行うに際し、液滴着弾精度を飛躍的に向上させることが可能になる。具体的には、液滴吐出法による液適の吐出直前に、所望のパターンに従い基板表面上の液滴着弾位置に荷電ビームを走査し、そのすぐ後に該荷電ビームと逆符号の電荷を液滴に帯電させて吐出することによって、液滴の着弾位置の制御性を格段に向上させることを特徴とする。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 反射防止機能とハードマスク機能を兼備した多層構造のSiC系膜を効率良く、確実に除去し、併せてゲート電極形成プロセスにおける膜の除去工程を簡素化し、デバイスへの悪影響を極力低減できる半導体装置の製造方法を提供する。

【解決手段】 基板上に形成された高誘電体膜と、ポリシリコン膜と、反射防止機能とハードマスク機能とを有するSiC系膜と、を有する積層体に対し、SiC系膜を、パターニングされたレジストをマスクとしてエッチングし、次にSiC系膜をマスクとして、ポリシリコン膜をエッチングした後、少なくとも、SiC系膜および露出した高誘電体膜にプラズマを作用させて改質するプラズマ処理工程と、改質されたSiC系膜および高誘電体膜をウエット洗浄により除去する洗浄工程と、を行なう。

(もっと読む)

半導体装置およびその作製方法

【課題】新規な構成を有する薄膜トランジスタを提供する。またコンタクトホールの形成を、容易かつ確実に実施する方法を提供する。

【解決手段】断面がテーパー形状であるアルミニウムゲイト電極と、前記ゲイト電極上のゲイト絶縁膜と、前記ゲイト絶縁膜上のチャネル形成領域を構成するI型のアモルファスシリコン膜と、前記I型のアモルファスシリコン膜上の保護膜と、前記I型のアモルファスシリコン膜及び保護膜上のn型のアモルファスシリコン膜からなるソース領域及びドレイン領域と、前記ソース領域に電気的に接続されたアルミニウムソース電極と、前記ドレイン領域に電気的に接続されたアルミニウムドレイン電極と、前記ゲイト絶縁膜上の画素電極と、前記ゲイト電極に電気的に接続されたアルミニウムゲイト配線と、を有し、前記ドレイン領域と前記画素電極とはアルミニウムを介して電気的に接続されていることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】AlGaN層の表面を平坦とし、かつ、AlGaN/GaN界面に存在する二次元電子ガスにダメージを与えない半導体装置の製造方法を提供する。

【解決手段】先ず、サファイア又は炭化珪素で形成される支持基板12を用意して、支持基板上にバッファ層14を堆積させる。次に、支持基板及びバッファ層を900℃以上1100℃以下に設定された成長温度に保持した状態で、バッファ層上に、GaN層16及びAlGaN層20を順次に積層してGaN半導体基板10を形成する。GaN半導体基板を形成する工程に引き続いて、GaN半導体基板を500℃以上成長温度以下の温度に保持した状態で、AlGaN層の上側表面28上に、表面保護膜としてAlN層30を形成する。

(もっと読む)

161 - 180 / 190

[ Back to top ]