Fターム[4M104DD18]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | コンタクトホール又は電極析出部の形成 (4,254) | 孔開け、又は除去する絶縁膜の材料 (2,744) | 酸化窒化Si (154)

Fターム[4M104DD18]に分類される特許

41 - 60 / 154

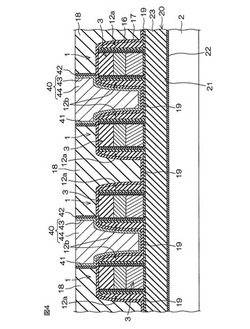

半導体装置およびその製造方法

【課題】コンタクト孔に埋め込まれる金属プラグの材料が層間絶縁膜に染み出すのを防止できる半導体装置を提供する。

【解決手段】隣り合う2つのメモリセル1のサイドウォール間の不純物拡散領域に電気的接続されるコンタクトプラグ40が、層間絶縁膜18を貫通して設けられている。コンタクト孔41の側壁は、層間絶縁膜18より緻密なシール膜42で覆われている。コンタクトプラグ40は、シール膜42の表面およびコンタクト孔41の底面部を覆うように形成されたバリアメタル膜43と、バリアメタル膜43に包囲された状態でコンタクト孔41内に埋め込まれた金属プラグ44とを含む。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成する半導体装置の作製方法を提供することを目的の一とする。

【解決手段】絶縁表面上に、酸化物半導体層と、酸化物半導体層と接するソース電極およびドレイン電極と、を形成し、ソース電極上およびドレイン電極上にそれぞれ絶縁層を形成し、酸化物半導体層、ソース電極、ドレイン電極および絶縁層上にゲート絶縁層を形成し、ゲート絶縁層上に導電層を形成し、導電層を覆うように絶縁膜を形成し、導電層におけるソース電極またはドレイン電極と重畳する領域の少なくとも一部が露出するように絶縁膜を加工し、導電層の露出した領域をエッチングして、ソース電極とドレイン電極に挟まれた領域の少なくとも一部と重畳するゲート電極を自己整合的に形成する半導体装置の作製方法である。

(もっと読む)

トップゲート型薄膜トランジスタ及びこれを備えた表示装置

【課題】酸化物半導体層のチャネル領域の、水素拡散による低抵抗化を抑制するトップゲート型酸化物半導体TFT及びこれを備えた表示装置を提供する。

【解決手段】基板の上に、ソース電極層と、ドレイン電極層と、酸化物半導体層と、ゲート絶縁層と、In、Ga、Zn、Snの少なくとも1種類の元素を含むアモルファス酸化物半導体からなるゲート電極層と、水素を含む保護層と、を有し、ゲート絶縁層は酸化物半導体層のチャネル領域の上に形成され、ゲート電極層はゲート絶縁層の上に形成され、保護層はゲート電極層の上に形成されていることを特徴とするトップゲート型薄膜トランジスタ。

(もっと読む)

半導体装置及び電子機器

【課題】マスク数を増加させることなく、ブラックマスクを用いずに反射型または透過型の表示装置における画素開口率を改善する。

【解決手段】画素間を遮光する箇所は、画素電極167をソース配線137と一部重なるように配置し、TFTはTFTのチャネル形成領域と重なるゲート配線166によって遮光することによって、高い画素開口率を実現する。

(もっと読む)

窒化物半導体装置

【課題】GaN系の窒化物半導体を用いたデバイスのゲートリセス量の制御性を向上することで、閾値電圧の面内均一性を向上することができる窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、基板101上に形成された第1のGaN系半導体からなるバッファ層102と、第2のGaN系半導体からなるキャリア走行層103と、第3のGaN系半導体からなるキャリア供給層104とを備えている。キャリア供給層104の上には第1の絶縁膜105と、アルミニウムを含む第2の絶縁膜106と、第1の絶縁膜105より膜厚が厚い第3の絶縁膜107とが形成されている。ソース電極108及びドレイン電極109は第1の絶縁膜105上に形成されている。ゲート電極110は、リセス構造を含む第2の絶縁膜106及び第3の絶縁膜107上に形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】初期故障や偶発故障の発生を低減する。

【解決手段】HFET1は、下層のGaN層13およびGaN層13の一部を露出させるトレンチT1が形成された上層のAlGaN層14よりなるIII族窒化物半導体層と、III族窒化物半導体層上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、を備える。少なくともゲート絶縁膜15と接触するトレンチT1底部のGaN層13上面には、原子層ステップが形成されている。原子層ステップのテラス幅の平均値は、0.2μm以上1μm未満である。

(もっと読む)

半導体装置の製造方法

【課題】ソース・ドレイン電極と半導体膜とのコンタクト不良を抑制することが可能な半導体装置等を提供する。

【解決手段】両端部30s、30dの膜厚が平坦部30cの膜厚よりも厚い半導体膜30を形成する。ゲート絶縁膜40は、両端部30s、30dが露出されるように形成される。両端部30s、30dには、ソース・ドレイン電極50s、50dとソース・ドレイン領域とを接続する中間電極50s、50dが形成され、この中間電極50s、50dまで開口するコンタクトホールが形成される。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

電界効果トランジスタ

【課題】高電圧を印加しても壊れにくい電界効果トランジスタを提供すること。

【解決手段】この電界効果トランジスタは、略同一の第1、第2トランジスタ部11,12を備える。第1のトランジスタ部11は、ヘテロ接合を含むIII族窒化物半導体層構造、III族窒化物半導体層構造上に間隔をおいて配置されたソース電極5およびドレイン電極7、フィールドプレート91を有するゲート電極6、ドレイン電極7を被覆するように配置された絶縁体層8を有する。フィールドプレート91は、ドレイン電極7を覆うようにひさし状に延在する。第2のトランジスタ部12は、第1のトランジスタ部11と略面対称に配置されている。第1のトランジスタ部11のIII族窒化物半導体層構造、絶縁体層8およびドレイン電極7は、第2のトランジスタ部12において対応する構造または層と一体化されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】耐圧を向上できる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、GaN層10と第1の絶縁層13と第2の絶縁層14と電極層とFP電極17とを備えている。GaN層10は、高欠陥領域10aと、高欠陥領域10aよりも欠陥密度の低い低欠陥領域10bとを含み、主表面10cを有する。第1の絶縁層13は、GaN層10の主表面10cにおける高欠陥領域10aを覆うように形成されている。第2の絶縁層14は、GaN層10の主表面10aにおける低欠陥領域10bの上に形成され、開口部が形成されている。電極層は、開口部の内部に、GaN層10の主表面10aに接触するように形成されている。FP電極17は、電極層に接続するとともに、第2の絶縁層14に重なるように形成されている。第1の絶縁層13の厚みH13は、第2の絶縁層14の厚みH14よりも大きい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】応答特性を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、GaN層10と第1および第2の絶縁層13、14と電極層とFP電極17とを備える。GaN層10は、高欠陥領域10aと、高欠陥領域10aよりも欠陥密度の低い低欠陥領域10bとを含み、主表面10cを有する。第1の絶縁層13は、GaN層10の主表面10cにおける高欠陥領域10aを覆うように形成される。第2の絶縁層14は、GaN層10の主表面10aにおける低欠陥領域10bの上に形成され、開口部が形成される。電極層は、開口部の内部に、GaN層10の主表面10aに接触するように形成される。FP電極17は、電極層に接続するとともに、第2の絶縁層14に重なるように形成される。第1の絶縁層13は、第2の絶縁層14を構成する材料の誘電率よりも小さい誘電率を有する材料を含む。

(もっと読む)

半導体装置およびその作製方法

【課題】画素部の開口率を高くしながら、駆動回路部の特性を向上させた半導体装置を提供することを課題とする。または、消費電力の低い半導体装置を提供することを課題とする。または、しきい値電圧を制御できる半導体装置を提供することを課題とする。

【解決手段】絶縁面を有する基板と、基板上に設けられた画素部と、画素部を駆動する駆動回路の少なくとも一部を有し、画素部を構成するトランジスタおよび駆動回路を構成するトランジスタは、トップゲートボトムコンタクト型のトランジスタであって、画素部においては、電極および半導体層が透光性を有し、駆動回路における電極は、画素部のトランジスタが有するいずれの電極よりも低抵抗である半導体装置である。

(もっと読む)

光電変換装置の製造方法

【課題】高い均一性を備える銀薄膜を熱処理により凝集させて凸凹を形成する場合、温度や表面状態により、一箇所に凝集し、銀薄膜が無くなってしまう領域と、銀が「だま」状に集中してしまう場所ができてしまう場合がある。この場合、本来の目的である乱反射領域にはならず、不良品となる課題がある。

【解決手段】多結晶ITO層20aを積層し、フォトリソグラフ工程によりレジストマスクを形成した後、多結晶ITO層20aを例えば塩酸系のエッチング液を用いてエッチングする。ここで、レジストマスクに覆われた部分は配線層として機能する。この場合粒界から選択的にエッチングが進行し、特定の面方位のグレインが残り、エッチングマスクとして機能する残渣20bが形成される。この残渣20bをマスクとして第2層間絶縁層19をドライエッチングすることでテクスチャー構造を得ることができる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極中の不純物がゲート絶縁膜を突き抜けてチャネル領域に拡

散するのを抑制し、ソース・ドレイン領域の不純物イオンが部分的にチャネル領

域方向に異常拡散するのを防ぐ。

【解決手段】ゲート絶縁膜3上に、ポリシリコン膜4を被着してゲート電極5

パターンにパターンニングした後、ソース・ドレイン領域9を形成する前に、窒

素を含む雰囲気中で窒化処理を行って、ゲート電極5端部付近のゲート絶縁膜3

中に新たに窒素を導入する。または、ゲート電極5のパターンニング後、ソース

・ドレイン領域9を形成する前に、酸化処理を行うことによってゲート電極5の

パターンニングの際に生じるダメージや汚染の一部を酸化膜中に取り込んで基板

から除去する。その後、窒化処理を行うことにより、酸化処理によってゲート電

極5端部付近に形成され、ダメージを含む酸化膜に積極的に窒素を導入する。

(もっと読む)

半導体装置及びその製造方法

【課題】導電層を自己整合的に形成する場合において、第1の拡散層コンタクトプラグのコンタクトマージンを比較的大きく取る。

【解決手段】半導体装置10は、第1のシリコンピラー14Aと、第1のシリコンピラー14Aの上面に設けられ、導電性材料が充填されたスルーホール30aを有する層間絶縁膜30と、スルーホール30aの上側開口部に設けられた第1の拡散層コンタクトプラグDC1とを備え、スルーホール30aの下側開口部の面積は前記第1のシリコンピラー14Aの上面の面積に等しくなっているとともに、スルーホール30aの上側開口部の面積はスルーホール30aの下側開口部の面積より大きくなっており、それによって、スルーホール30a内の導電性材料の第1の拡散層コンタクトプラグDC1との接続面の面積が第1のシリコンピラー14Aの上面の面積より大きくなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】少ない工程数で製造可能であり、かつゲート電極付近の電界集中を緩和させる。

【解決手段】下地11上に第1及び第2絶縁膜13及び15を順次形成し、第2絶縁膜に表面から第1開口パターン、及び第1絶縁膜を露出させ、かつ第1開口パターンよりも開口端の第1方向に沿った長さが短い第2開口パターンを形成し、第1開口パターンを厚み方向に沿って拡大することによって第1開口部19、第1及び第2開口パターンからの露出面から第1絶縁膜を部分的に除去することによって、第1開口部から連続し、かつ第1開口部19よりも開口端の第1方向に沿った長さが短い第2開口部21、及び第2開口部から連続した、下地面を露出させ、かつ第2開口部よりも開口端の第1方向に沿った長さが短い第3開口部23を形成し、第1〜第3開口部を含む電極形成用開口部17を埋め込むとともに、電極形成用開口部周辺の第2絶縁膜の表面を被覆する電極を形成する。

(もっと読む)

半導体装置、液晶表示装置、テレビ、ノート型パーソナルコンピュータ及び携帯情報端末

【課題】信頼性の高い半導体装置を提供する。

【解決手段】ゲート電極と、ゲート電極の上に設けられたゲート絶縁膜と、ゲート絶縁膜

の上に設けられソース領域及びドレイン領域を含む半導体膜と、ソース領域又はドレイン

領域に電気的に接続する配線又は電極と、配線又は電極の上に設けられ第1の開口部を有

する第1の絶縁膜と、第1の絶縁膜の上に設けられ第2の開口部を有する第2の絶縁膜と

、第2の絶縁膜の上に設けられた画素電極とを有し、第1の絶縁膜は窒化シリコン膜を含

む積層の無機絶縁膜からなり、第2の絶縁膜は有機樹脂膜からなり、第2の絶縁膜の第2

の開口部の底面において、第1の絶縁膜の上面は第2の絶縁膜に覆われていない露呈した

部分を有し、第2の絶縁膜の第2の開口部の断面において、第2の絶縁膜の内壁面は凸状

の曲面を有しており、画素電極は、第1の開口部及び第2の開口部を介して配線又は電極

に電気的に接続されている。

(もっと読む)

半導体装置

【課題】金属配線と金属酸化物を有する層を形成する際、電蝕といわれる腐食の発生をおさえることにより、半導体装置の動作特性および信頼性を向上させ、歩留まりの向上を実現することを目的とする。

【解決手段】配線は、耐酸化性金属からなる第1の層と、その上に形成されたアルミニウムもしくはアルミニウムを主成分とする第2の層と、その上に形成された耐酸化性金属からなる第3の層からなる3層構造とし、前記配線と電気的に接続する金属酸化物を有する層を有する。また、第2の層の上面及び下面は第1及び第3の層と接し、側面は酸素とアルミニウムを含む酸化層と接する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、逆阻止特性を有し、かつノーマリオフ特性、オン抵抗とオフ電流の抑制を実現する半導体装置を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、チャネル層14及び電子供給層15を含む半導体積層構造10と、半導体積層構造10上に離間して形成されたソース電極1およびドレイン電極4と、ソース電極1及び前記ドレイン電極4間に形成された絶縁膜22と、絶縁膜上に形成されたゲート電極2とを備え、ドレイン電極4と前記半導体積層構造10との間の逆電流が阻止されたものである。

(もっと読む)

薄膜トランジスタの製造方法及び電気光学装置の製造方法

【課題】活性層としてIn−Ga−Zn−O系ホモロガス酸化物半導体を用い、エッチングストッパー層を形成することなく活性層のダメージを抑制するとともに、ソース・ドレイン電極の低抵抗化を図ることが可能な薄膜トランジスタの製造方法及び電気光学装置の製造方法を提供する。

【解決手段】In、Ga、及びZnを含む酸化物半導体膜16を形成する工程と、前記酸化物半導体膜を活性層18にパターン加工する工程と、前記酸化物半導体膜を500℃以上で熱処理する工程と、前記酸化物半導体膜がパターン加工され、かつ、熱処理した活性層を覆うように金属膜を形成する工程と、前記金属膜をエッチングしてパターン加工することにより前記活性層と接触するソース電極20A及びドレイン電極20Bの少なくとも一方を形成する工程と、を含むことを特徴とする薄膜トランジスタの製造方法。

(もっと読む)

41 - 60 / 154

[ Back to top ]