Fターム[4M104DD23]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 析出面の前処理 (2,098) | 表面処理 (1,044) | 酸化膜除去 (272)

Fターム[4M104DD23]に分類される特許

141 - 160 / 272

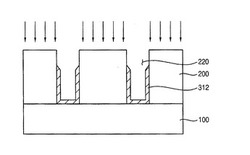

半導体素子及びその製造方法

【課題】コンタクトプラグの形成のための平坦化工程で障壁層が損傷することを防止することができる半導体素子及びその製造方法を提供する。

【解決手段】本発明の半導体素子の製造方法は、半導体基板上に複数の導電性構造物間の空間を埋め立てて上面が平坦化された絶縁膜を形成し、絶縁膜を部分的に除去して基板の一部を露出する開口を形成する。その後、開口の下部側壁及び底面に沿って形成された残留金属膜と開口の上部側壁及び残留金属膜の表面に沿って形成された金属窒化膜とを含む障壁層を形成する。障壁層を含む開口を埋め立てて金属プラグを形成する。

(もっと読む)

シード印刷及びめっきによるコンタクト金属及び相互接続金属の印刷

シリサイド形成金属を含むインクを用いて、コンタクト形成方法、そのコンタクト及び局所相互接続を含むダイオード及び/又はトランジスタ等の電気デバイスとその形成方法に関する。コンタクト形成方法は、露出したシリコン表面上にシリサイド形成金属インクを堆積させるステップと、インクを乾燥させ、シリサイド形成金属前駆体を形成するステップと、シリサイド形成金属前駆体及びシリコン表面を加熱して、金属スイサイドコンタクトを形成するステップとを含む。任意選択的に、露出したシリコン表面に隣接する誘電体層上に、金属前駆体インクを選択的に堆積させて、金属含有相互接続を形成できる。更に、1つ又は複数のバルク導電性金属を、残りの金属前駆体インク及び/又は誘電体層上に堆積させてもよい。かかる印刷したコンタクト及び/又は局所相互接続を用いて、ダイオード及びトランジスタ等を作製できる。 (もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】ゲート絶縁膜7、ゲート電極8a,8b、ソース・ドレイン用のn+型半導体領域9b及びp+型半導体領域10bを形成してから、半導体基板1上に金属膜及びバリア膜を形成し、第1の熱処理を行って金属膜とゲート電極8a,8b、n+型半導体領域9bおよびp+型半導体領域10bとを反応させることで、金属膜を構成する金属元素MのモノシリサイドMSiからなる金属シリサイド層41を形成する。その後、バリア膜および未反応の金属膜を除去してから、第2の熱処理を行い金属シリサイド層41を安定化させる。これ以降、半導体基板1の温度が第2の熱処理の熱処理温度よりも高温となるような処理は行わない。第2の熱処理の熱処理温度は、金属元素MのダイシリサイドMSi2の格子サイズと半導体基板1の格子サイズが一致する温度よりも低くする。

(もっと読む)

窒化物半導体の表面清浄化方法

【課題】本発明は、比較的に低温かつ簡便な処理工程で、上記高温水素プラズマ照射結果と同程度以上のクリーンな窒化物半導体の表面が得られる処理工程を提供することを課題とする。

【解決手段】窒化物半導体(BzAlxGa1-x-y-zInyN1-p-qPpAsq、但し0≦x、y、z、p、q<1、かつx+y+z<1、p+q<1)の表面に原子状水素を照射して自然酸化膜を除去する工程と、酸素プラズマを照射して人工酸化膜を形成する工程と、湿式エッチングにより人工酸化膜を選択的に除去する工程と、人工酸化膜が除去された窒化物半導体の表面を硫黄処理することにより表面保護層を形成する工程と、熱処理により表面保護層を除去する工程とを含む窒化物半導体の表面清浄化方法によって解決される。

(もっと読む)

半導体装置およびその製造方法

【課題】エッチングの終了を時間管理する場合よりも精度良くエッチングできる半導体装置とその製造方法を提供することにある。

【解決手段】

本発明の半導体装置の製造方法は、SiC基板1の表面上に導電膜2を形成する工程と、導電膜2とSiC基板1を反応させて、導電膜2の材料がSiC基板1に拡散したNiSi層3、SiC基板1の珪素により珪化したNi2Si層4、グラファイト5および球状炭素6を生成する工程と、グラファイト5、球状炭素6およびNi2Si層4を、珪素と比較して炭素と結合し易い雰囲気中でエッチングするエッチング工程とを含む。更に、エッチング工程中に放出される炭素放出量がピークを超えて、かつ、所定値以下になった場合にエッチング工程を終了する。

(もっと読む)

半導体装置を回路基板に実装する方法

【課題】 シリコン基板の裏面部にアルミスパイクが発達しづらい半導体装置を提供すること。

【解決手段】 はんだを介して回路基板と接合するために、シリコン基板30の裏面から順に、第1導電層28と、第2導電層26と、第3導電層24を有する裏面電極20を備えている縦型のIGBTである。第1導電層28は、アルミニウムとシリコンを含んでいる。第2導電層26は、チタンを含んでいる。第3導電層24は、ニッケルを含んでいる。第1導電層28の厚みは、600nm以上であることを特徴としている。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜に開口された接続孔の内部に、チタン膜上に窒化チタン膜が形成された積層構造のバリアメタル膜を介して金属膜を埋め込んだ接続部における不具合を回避する。

【解決手段】コンタクトホールC1を形成して、その底部にニッケルシリサイド層14を露出させた後、TiCl4ガスを用いた熱反応により熱反応Ti膜21aを形成し、TiCl4ガスを用いたプラズマ反応によりプラズマ反応Ti膜21bを形成し、H2ガスを用いたプラズマ処理を施して、プラズマ反応Ti膜21bの塩素濃度を低減すると同時に、ニッケルシリサイド層14の表面の酸化膜を還元し、NH3ガスを用いた熱窒化処理及びNH3ガスを用いたプラズマ処理を施して、プラズマ反応Ti膜21bの表面に窒素リッチTiN膜21cを形成すると同時に、ニッケルシリサイド層14の表面の酸化膜を還元する。

(もっと読む)

半導体装置の製造方法、半導体製造装置及び記憶媒体

【課題】絶縁膜の表面および絶縁膜の凹部に沿ってシード層を成膜し、凹部に銅配線を埋め込んだ後、加熱によりバリア膜を形成すると共にシード層を構成する金属の余剰分を配線から除去するにあたって、配線中における前記金属およびその酸化物の残留を抑えて、配線抵抗の上昇を抑えること。

【解決手段】凹部の底部に露出した、銅からなる下層側導電路の表面における、前記銅の自然酸化物を還元するかまたは除去する工程と、前記自然酸化物が還元または除去された基板に対し、銅よりも酸化傾向が高く、酸化物となって銅の拡散防止機能を発揮する自己形成バリア用の金属、またはこの金属と銅との合金からなるシード層を形成する工程と、凹部に銅を埋め込んだ後に前記自己形成バリア用の金属を酸化してバリア層を形成すると共に余剰の自己形成バリア用の金属を埋め込まれた銅の表面に析出させるために基板を加熱する工程と、を含むように半導体装置を製造する。

(もっと読む)

スタックゲート型不揮発性半導体メモリ

【課題】半導体基板上において、下方に浮遊ゲートを有するとともに上方に制御ゲートを有するメモリセルトランジスタの、前記制御ゲートを完全にシリサイド化するとともに、前記半導体基板上において形成した選択ゲートトランジスタなどの制御トランジスタの、シリサイド化の過度の進行を抑制し、書き込み速度の遅延や閾値などの変動を抑制したスタックゲート型不揮発性半導体メモリを提供する。

【解決手段】メモリセルトランジスタの制御ゲートは、酸化層を含まないシリサイドから構成し、制御トランジスタは、層間絶縁膜を貫通するようにして半導体層及びシリサイド層を電気的に接続する追加のシリサイド層を有し、前記追加のシリサイド層は、底面及び側面において、前記半導体層及び前記シリサイド層と、シリサイド化進行防止層で離隔するようにして構成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】複数の積層ゲート電極間に形成される電極間絶縁膜のアスペクト比が高く電極間絶縁膜内にシームが生じたとしても当該シーム内に不要成分を侵入させることなくデバイス不良を防止できるようにする。

【解決手段】シリコン酸化膜8上で且つ多結晶シリコン層6の側面位置にシリコン窒化膜14を形成した後、多結晶シリコン層6上のシリコン窒化膜12を除去している。このため、多結晶シリコン層6の上面をウェットエッチング処理して清浄化するときにシリコン酸化膜8の中央上部にシーム8aが形成されていたとしても、当該シーム8a上を覆うようにシリコン窒化膜14がキャップ絶縁膜として形成されているため、シーム8aを拡大させることなく多結晶シリコン層6の上面を清浄化することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】シリサイド層上に抵抗値の上昇が抑制されたコンタクトを備え、高い信頼性を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板10と、半導体基板10内に形成された活性領域50と、活性領域50の上面に形成されたシリサイド層45と、半導体基板10およびシリサイド層45の上に形成された第1の層間絶縁膜15と、シリサイド層45上に形成され、第1の層間絶縁膜15を貫通するコンタクトプラグ60とを備えている。コンタクトプラグ1個当たりのシリサイド層45の面積は、コンタクトプラグの面積以上、且つ、100μm2以下である。

(もっと読む)

半導体装置の作製方法

【課題】作製コスト及び作製時間が低減された、信頼性の高い半導体装置を作製すること。

【解決手段】島状半導体膜を覆って絶縁膜を形成し、絶縁膜上に第1のゲート電極を形成し、第1のゲート電極をマスクとして絶縁膜をエッチングし第1のゲート電極と同じ幅のゲート絶縁膜を形成し、第1のゲート電極をマスクとして島状半導体膜に不純物元素を第1の濃度で添加し、金属膜を形成後加熱処理によりゲート絶縁膜に覆われていない領域にシリサイド領域を形成し、第1のゲート電極をエッチングし第1のゲート電極より幅の小さい第2のゲート電極を形成し、ゲート絶縁膜及び第2のゲート電極をマスクとして、島状半導体中に不純物元素を第1の濃度より小さい第2の濃度で添加し、島状半導体膜中に低濃度不純物領域、チャネル形成領域、及び高濃度不純物領域を形成する半導体装置の作製方法に関する。

(もっと読む)

電極および電極の形成方法

【課題】半導体シリコンウェーハの電気的特性を評価するにあたり、電気的特性の評価の精度を従来に比べ向上させることが可能なシリコンウェーハ上にショットキー接合された電極とその電極の形成方法を提供する。

【解決手段】半導体シリコンウェーハ上にショットキー接合された電極であって、半導体シリコンウェーハ上に酸化膜を介することなくアルミナ(Al2O3)と金属アルミニウムを真空蒸着したものであることを特徴とする電極とその形成方法である。

(もっと読む)

プラズマ処理方法及び記憶媒体

【課題】タングステンからなる電極や配線の表面に形成された酸化物を、アンモニアガスをプラズマにより活性化させた活性種で確実に還元処理することができ、しかもタングステン表面に窒化タングステン膜が形成されないようにする技術を提供すること。

【解決手段】縦型の処理容器内の処理雰囲気から径方向に外れかつ当該処理雰囲気に臨む領域に、前記処理雰囲気に沿って形成されたプラズマ発生領域と、このプラズマ発生領域に沿って伸びるようにかつ当該プラズマ発生領域を挟んで対向して配置されるプラズマ電極と、を備えた縦型熱処理装置を用いて還元処理するにあたって、プラズマ発生領域に供給するアンモニアの供給量を500sccm以上10000sccm以下、プラズマ電極に印加する高周波を20W以上500W以下、処理雰囲気の圧力を13.3×102Pa以下、処理時間を1秒以上10分以下とする。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】半導体基板1にSTI法で素子分離領域4を形成し、ゲート絶縁膜7を形成し、ゲート電極8a,8bを形成し、ソース・ドレイン用のn+型半導体領域9bおよびp+型半導体領域10bを形成し、半導体基板1上に金属膜12を形成し、金属膜12上にバリア膜13を形成する。それから、第1の熱処理を行って金属膜12とゲート電極8a,8b、n+型半導体領域9bおよびp+型半導体領域10bとを反応させて金属シリサイド層を形成してから、バリア膜13および未反応の金属膜12を除去し、前記金属シリサイド層を残す。素子分離領域4は半導体基板1に圧縮応力を作用させる。バリア膜13は半導体基板1に引張応力を生じさせる膜であり、第1の熱処理では、金属膜12を構成する金属元素MのモノシリサイドMSiからなる金属シリサイド層が形成される。

(もっと読む)

自己整合エピタキシャルソース及びドレイン張り出し部を有する半導体デバイス

ゲート誘電層に近接する自己整合ソース及びドレイン張り出し部を有するトランジスタの作製方法は、基板上にゲート積層体を作製する工程、前記ゲート積層体に隣接する前記基板の領域へドーパントを注入する工程であって、前記ドーパントは前記基板のエッチング速度を増大させ、かつ前記ソース及びドレイン張り出し部の位置を画定する工程、前記基板のドーパントが注入された領域上に設けられた前記ゲート積層体の横方向で対向する面に一対のスペーサを形成する工程、前記基板のドーパントが注入された領域及び該領域の下に位置する前記基板の一部をエッチングする工程であって、前記ドーパントが注入された領域のエッチング速度は該領域の下に位置する前記基板の一部のエッチング速度よりも速い工程、並びに、前記の基板のエッチングされた部分中にシリコンベースの材料を堆積する工程、を有する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】シリコンから構成される導電パターンの下から上までの幅を均一化すること。

【解決手段】半導体基板1上に絶縁膜5を介して第1シリコン膜6を形成し、第1シリコン膜6に高濃度で一導電型不純物を導入し、第1シリコン膜6上に第2シリコン膜9を形成し、第2シリコン膜9上に所定パターンのマスク10mを形成した後、マスク10mから露出する領域で、第1シリコン膜6が露出しない深さまで第1条件により第2シリコン膜9をエッチングし、ついで第1条件に比べて半導体基板1の垂直方向へのエッチング成分の高い第2条件によって第2シリコン膜9の残りと第1シリコン膜6を絶縁膜5が露出しない深さまでエッチングし、さらに第2条件に比べて絶縁膜に対する第1シリコン膜6のエッチング選択比が大きな第3条件により第1シリコン膜6の残りをエッチングする工程とを有している。

(もっと読む)

半導体装置

【課題】信頼性の向上した半導体装置及びその作製方法を提供する。

【解決手段】ゲート電極と重畳し、該重畳領域の外側に不純物領域が形成された半導体層と、半導体層のゲート電極が設けられた側と同じ側の面に設けられ、不純物領域と一部が接する第1導電層と、ゲート電極及び第1導電層の上に設けられた絶縁層と、該絶縁層に形成され、第1導電層と少なくとも一部が重畳する開口を介して第1導電層と接する第2導電層と、を有する。

(もっと読む)

P型4H−SiC基板上のオーミック電極の形成方法

【課題】P型4H−SiC上のオーミック電極の形成方法およびそれにより形成されたオーミック電極を提供する。

【解決手段】P型4H−SiC基板上に、厚さ1〜60nmの第1Al層と、Ti層と、第2Al層とを順次堆積する堆積工程、および非酸化性雰囲気中での熱処理により、上記第1Al層を媒介として上記SiC基板と上記Ti層との合金層を形成する合金化工程を含むことを特徴とするP型4H−SiC基板上のオーミック電極の形成方法。この方法により形成されたP型4H−SiC基板上のオーミック電極も提供される。

(もっと読む)

半導体装置の製造方法

【課題】NMOSのシリサイド組成をPMOSのシリサイド組成よりもシリコンリッチにしようとすると、フルシリサイド化の際にNMOSのポリシリコンに対するニッケルの供給を抑制する必要がある。

【解決手段】実施形態に係る半導体装置の製造方法は、基板上にゲート絶縁膜を介してシリコン層を形成する工程と、シリコン層をパターニングしてNMOSのゲート電極(第1のゲート電極)およびPMOSのゲート電極(第2のゲート電極)を形成する工程と、シリコンからなる第1のゲート電極上に、選択的にシリコン酸化膜を形成する工程と、シリコン酸化膜を形成する工程よりも後に、第1および第2のゲート電極上に、被シリサイド化金属からなる第1の金属膜を形成する工程と、第1の金属膜を構成する被シリサイド化金属のシリサイドである第1のシリサイドが形成されるように、第1の熱処理を行う工程と、を含む。

(もっと読む)

141 - 160 / 272

[ Back to top ]