Fターム[4M104DD23]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 析出面の前処理 (2,098) | 表面処理 (1,044) | 酸化膜除去 (272)

Fターム[4M104DD23]に分類される特許

261 - 272 / 272

半導体装置およびその製造方法

【課題】 シリサイド膜を有する半導体装置において配線抵抗を低減し、また配線抵抗のばらつきを低減する。

【解決手段】 コバルトシリサイドあるいはニッケルシリサイドを使う超高速半導体装置において、シリサイド膜形成のためシリコン表面に金属膜を堆積する前に、シリコン表面から自然酸化膜をウェットエッチングプロセスで除去した後、化学酸化膜を形成する。

(もっと読む)

半導体材料の予めパッシベーション化された表面を金属被覆するための方法及びその方法によって得られる材料

本発明は、半導体材料の予めパッシベーション化した表面を金属被覆するための方法及びその結果得られる材料に関する。本発明は、マイクロエレクトロニクスに適用可能であり、材料(2)の表面を前処理することにより、材料内に水素原子又は金属元素を吸着可能な結合を形成するステップ、表面をパッシベーション化化合物に露出することにより、好ましくは表面の直下に位置する一又は複数の層をパッシベーション化するステップ、及び表面(4)を水素原子へ又は金属元素に露出することにより、該表面を金属被覆するステップを含むことを特徴とする。  (もっと読む)

(もっと読む)

基板処理方法及び装置

【課題】 例えば配線等の下地金属の内部にボイドを発生させることなく、下地金属の露出表面に無電解めっきによって金属膜を確実に形成でき、しかも、スループットを向上させることができるようにする。

【解決手段】 下地金属を形成した基板の表面に無電解めっきにより金属膜を形成するに際し、基板の表面を、カルボキシル基を有する有機酸またはその塩の水溶液に界面活性剤を添加した洗浄液で洗浄し、洗浄後の基板の表面を、金属触媒イオンを含む溶液に前記洗浄液を混合した処理液に接触させて基板の表面に触媒を付与する。

(もっと読む)

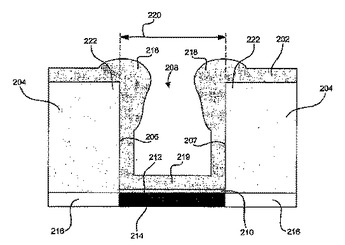

コンタクトの形成中、コンタクトホール幅の増大を防ぐ方法

一形態によれば、半導体ダイに位置するシリサイド層(214)上にコンタクトを形成する方法は、コンタクトホール(208)の各側壁(206、207)、及び、コンタクトホール(208)の底部に位置する自然酸化物層(210)に、バリア層(202)を堆積するステップを含み、各側壁(206、207)は、絶縁層(204)のコンタクトホールによって形成される。コンタクトホール(208)の各側壁(206、207)、及び、酸化物層(210)にバリア層(202)を堆積する(150)ステップにおいて、バリア層(202)の厚さを、コンタクトホール(208)の上部が、コンタクトホール(208)の底部よりも厚くなるよう最適化してもよい。この形態によれば、バリア層(202)の一部分(219)及びコンタクトホール(208)の底部に位置する酸化物層(210)を除去し、シリサイド層(214)を露出させるステップを含む方法も提供される。  (もっと読む)

(もっと読む)

バリヤ物質の原子層堆積

1以上の物質層のバリヤ層を原子層堆積により堆積させるために基板を処理する方法が提供される。一態様においては、金属含有化合物の1以上のパルスと窒素含有化合物の1以上のパルスを交互に導入することにより基板表面の少なくとも一部上に金属窒化物バリヤ層を堆積させるステップと、金属含有化合物の1以上のパルスと還元剤の1以上のパルスを交互に導入することにより金属窒化物バリヤ層の少なくとも一部上に金属バリヤ層を堆積させるステップとを含む基板を処理する方法が提供される。金属窒化物バリヤ層及び/又は金属バリヤ層の堆積前に基板表面上で浸漬プロセスが行われてもよい。 (もっと読む)

多層配線構造の製造方法

【課題】バリアメタル膜の表面に形成される自然酸化膜の膜厚を薄くし、ボイドの発生を防止した多層配線構造の製造方法を提供する。

【解決手段】埋め込み型の多層配線構造の製造方法において、絶縁層に孔部4を形成する工程と、少なくとも孔部の内壁を覆うように、タンタルと窒素を主成分とするバリアメタル膜5を形成する工程と、バリアメタル膜の表面に形成された酸化膜6を除去する工程と、銅を含むめっき液にバリアメタル膜を浸漬してバリアメタル膜上に無電解銅めっき膜7を形成する工程とを含み、バリアメタル膜に含まれる窒素とタンタルの元素組成比(N/Ta)を、0.3以上で、かつ1.5以下とする。

(もっと読む)

半導体装置及びその製造方法

【課題】低抵抗且つ高バリア性を有するバリアメタルを提供する。

【解決手段】バリアメタル201 が、配線溝16の底面及び側壁の表面に沿って形成された膜厚16nmのTaN0.87膜31と、TaN0.87膜上に形成され、配線溝16に埋め込み形成されたCuダマシン配線17に接する膜厚4nmのTaN1.19膜32とから構成されている。

(もっと読む)

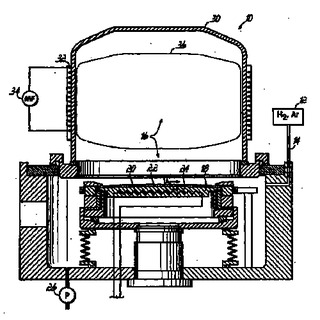

高温水素含有プラズマによるチャンバ及びウェーハ表面から物質を除去する方法及び装置

半導体ウェーハ処理装置(10)のチャンバ(16)と、清掃されるべき表面にバイアス電圧を掛けることなくガス混合物中に高密度プラズマを生成するためのみのICP電源と、に供給される、水素及び不活性ガスから成る清掃ガス混合物、例えば、水素含有量が体積で20%から80%の間にある混合物を使用する清掃方法が提供される。本発明の実施形態では、Si及びSiO2汚染物質又はCFx汚染物質は引き続く金属被着に先立ってシリコン・コンタクト(46)から清掃される。本発明の別の実施形態では、基準酸化物エッチング速度を回復するために酸化物をエッチングする以前にシリコン残留物は内部チャンバ表面から清掃される。

(もっと読む)

(もっと読む)

銅配線構造およびその製造方法

【課題】銅配線の寿命を増大させ、同時に、密着性を高め、ストレスマイグレーション耐性を向上させる。

【解決手段】Cu16とバリアメタル12、あるいはCu16とキャップ層19との界面近傍に、不純物15を固溶させる、不純物15を析出させる、非晶質Cu14を存在させるまたはCuとの化合物を形成することにより、界面近傍の空孔を減らし、Cuのエレクトロマイグレーション(EM)に対する界面拡散の寄与を減少させ、寿命を増大させ、同時に、密着性を高め、ストレスマイグレーション耐性を向上させた。

(もっと読む)

MOSトランジスタ

【課題】 再現性の高い工程を用いて低抵抗のゲート電極を有するGOLD構造を構成できるようにし、それにより、微細化が可能であるとともに信頼性の高いMOSトランジスタを提供する。

【解決手段】 半導体基板1に形成したソース及びドレイン領域10a,10bと、酸化膜3bを介して形成したゲート電極5と、前記ソース及びドレイン領域10a,10bとチャネル形成領域30の間に前記ソース及びドレイン領域10a,10bを取り囲むソース及びドレイン低濃度領域6a’,6b’とを有するMOSトランジスタにおいて、前記酸化膜3bを介して前記ソース及びドレイン低濃度領域6a’,6b’に接する導電性である2つのサイドスペーサ9aと、前記ゲート電極5及び前記サイドスペーサ9a上に形成された導電性薄膜15とを有する。

(もっと読む)

表示素子用配線、これを利用した薄膜トランジスタ基板及びその製造方法

【課題】 物理的に接着力が向上し、電気的には接触抵抗が良好な特性を有する表示素子用配線及びこれを利用した薄膜トランジスタ基板並びにその製造方法を提供することを目的とする。

【解決手段】 表示素子用配線を、低融点金属の合金元素が少なくとも一つ以上合金されているAg合金で形成する。液晶表示パネルにおいて、このような表示素子用配線を用いてゲート配線22,24,26及びデータ配線65,66,68を形成すれば、接触部で他の導電物質と連結される過程で腐食が発生して素子の特性を低下させるのを防止できる。

(もっと読む)

多層配線構造及びその製造方法

【課題】 エレクトロマイグレーション耐性と、ストレスマイグレーション耐性を同時に向上させる多層配線構造及びその製造方法を提供する。

【解決手段】 AlCu膜103Cと、厚みが0〜15nmのTi膜との反応によりAl3 Ti層103DをAlCu膜とTiN膜の界面に形成することにより、界面拡散を抑制し、かつAl3 Ti層形成時に発生する引張り応力を低減し、EM耐性を向上させる。その後のFSG膜104AをHDP−CVD法で成膜する際に、ウェハ裏面に不活性ガスを流してウェハを冷却し、ウェハ温度を450℃以下にすることにより、FSGとAlCuの熱膨張率差に起因するAlCu膜の残留引張り応力の発生を低減し、SM耐性及びEM耐性を向上させる。さらに、FSG膜の上にSiON膜を設けることにより、FSG膜の遊離フッ素の上方への拡散を阻止して、上層配線の剥がれを防止する。

(もっと読む)

261 - 272 / 272

[ Back to top ]