Fターム[4M104DD23]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 析出面の前処理 (2,098) | 表面処理 (1,044) | 酸化膜除去 (272)

Fターム[4M104DD23]に分類される特許

101 - 120 / 272

成膜方法

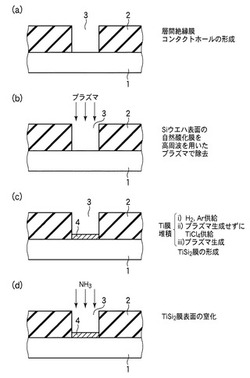

【課題】結晶粒径が均一な金属シリサイド膜、特にチタンシリサイド膜を形成することができる成膜方法を提供すること。

【解決手段】被処理体1のSi含有部分上の自然酸化膜を除去する工程と、被処理体1の自然酸化膜が除去されたSi含有部分上に金属シリサイド膜4を形成する工程とを具備し、金属シリサイド膜4を形成する工程は、最初にプラズマを生成せずに、成膜しようとする金属シリサイド中の金属を含有する金属含有原料ガスを所定時間供給して金属−シリコン結合を生じさせ(ii)、次いで金属含有原料ガスを供給しつつプラズマを生成して当該金属からなる金属膜を成膜し、その際の金属膜とSi含有部分との反応により金属シリサイド膜を形成する(iii)。

(もっと読む)

半導体装置の製造方法

【課題】電極導体膜を有する半導体装置の信頼性を向上させる。

【解決手段】n型MISトランジスタQnを形成したシリコン基板1の層間絶縁膜ILにコンタクトホールCHを形成し(工程s03〜工程s07)、それを埋め込むようにして電極導体膜E1を形成する(工程s11〜工程s14)。電極導体膜E1は、1〜3μmの第1導体膜E1aと1〜3μmの第2導体膜E1bとの2回に分けて堆積し(工程s12、工程s14)、特に、それぞれを堆積する工程の間ではシリコン基板1を一時待機させ(工程s13)、また、第1導体膜E1aは第2導体膜E1bよりも速い堆積速度で堆積する。

(もっと読む)

半導体装置の製造装置及び半導体装置の製造方法

【課題】多層配線構造における硼窒化ジルコニウム膜と下地膜との間の密着性を向上させることにより半導体装置の信頼性を向上させた半導体装置の製造装置及び半導体装置の製造方法を提供する。

【解決手段】第1メタルキャップ膜MC1と第2メタルキャップ膜MC2とが成膜される際に、まず基板Sの表面に水素ラジカルが供給されて、表面処理である微粒子のエッチング処理や未結合手への末端処理、さらには酸化層の還元処理が実行される。そして、この表面処理が基板Sに施された後、基板Sの表面にZr(BH4)4と励起状態の窒素とが供給されて、第1メタルキャップ膜MC1及び第2メタルキャップ膜MC2である硼窒化ジルコニウム膜が成膜される。

(もっと読む)

絶縁ゲート電界効果トランジスタ及びその製造方法

【課題】ゲート絶縁膜やゲート電極を構成する材料がエッチングされることが無く、高い信頼性を有するゲート電極を有する絶縁ゲート電界効果トランジスタを提供する。

【解決手段】絶縁ゲート電界効果トランジスタは、ソース/ドレイン領域13、チャネル形成領域12、ゲート電極423、ゲート絶縁膜430を備え、ゲート絶縁膜430はゲート絶縁膜本体部430A及びゲート絶縁膜延在部430Bから構成されており、ゲート電極を構成する第1層431はゲート電極の側面部の途中まで薄膜状に形成されており、第2層の外側層432Aは第1層431の上に薄膜状に形成されており、第2層の内側層432Bは第2層の外側層で囲まれた部分を埋め込んでおり、第3層の外側層433Aは第2層の内側層、外側層、ゲート絶縁膜延在部を覆い、ゲート電極の頂面まで薄膜状に形成されており、第3層の内側層433Bはゲート電極の残部を占めている。

(もっと読む)

半導体装置の製造装置

【課題】装置の高いスループットを維持しつつ、バリアメタルの酸化工程の追加や異なる種類のシード層の積層、バリア層の積層等を行い配線の信頼性を向上させる。

【解決手段】薄膜の合金シード層を成長させるチャンバー、または、薄膜のバリアメタルを成長させるチャンバーのうち、最も短いタクト時間のチャンバー数を最も少なくして、あるいは、統一して1台の装置で専用に用い、タクト時間の長い工程のチャンバーを2または、3チャンバー以上にすることにより、薄膜工程のチャンバー間バラツキを無くして、装置のスループットを向上させる。

(もっと読む)

半導体装置、およびその製造方法

【課題】配線間をCuプラグによって電気的に接続する構成において、Cuプラグとの電気的接続の信頼性が高く、リーク電流が少ない半導体装置、およびその製造方法を提供することを目的とする。

【解決手段】本発明における半導体装置100は、拡散層43およびゲート電極42を形成した半導体基板1と、半導体基板1上に形成された層間絶縁膜5と、層間絶縁膜5を貫通し、拡散層43およびゲート電極42上に形成されたコンタクトホール61と、コンタクトホール61の内面に形成されたTiバリアメタル層62と、バリアメタル層62上に形成されたW、Co、Ru、Ptのいずれかを含むシード層63と、シード層63上であってコンタクトホール61を充填するように形成されたCuプラグ64と、Cuプラグ64上に形成された配線層7と、を備える。

(もっと読む)

銅表面上への選択的コバルト堆積

本発明の実施形態は、露出誘電表面を覆う銅表面上にコバルト層を選択的に形成するプロセスを提供する。一実施形態では、前処理プロセスの間に金属銅表面を形成している間は処理チャンバー内の基板の汚染された銅表面を還元剤にさらすステップと、気相堆積プロセスの間に基板上の誘電表面を露出したままにしながら金属銅表面を覆ってまたは上にコバルトキャッピング層を選択的に形成するために基板をコバルト前駆体ガスにさらすステップと、コバルトキャッピング層および誘電表面を覆ってまたは上に誘電障壁層を堆積させるステップとを包含する、基板上の銅表面をキャッピングするための方法が、提供される。別の実施形態では、堆積−処理サイクルは、気相堆積プロセスを実行した後に後処理プロセスを実行するステップを包含し、その堆積−処理サイクルは、複数のコバルトキャッピング層を形成するために繰り返されてもよい。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】微細コンタクト孔の形状寸法を安定させつつ、コンタクト抵抗ばらつきを低減することができる、半導体装置およびその製造方法を提供する。

【解決手段】半導体基板11上にニッケルを含む金属シリサイド層12を形成し、その最表面12aを窒化した半導体装置を構成する。この構造によれば、金属シリサイド層最表面12aの窒化により、金属シリサイド層12中に存在するシリコンのダングリングボンドと窒素が結合するため、金属シリサイド層12中への酸素の拡散を抑制することができる。したがって、金属シリサイド層12の酸化による電気的絶縁を低減できるため、コンタクト抵抗を安定化することができる。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】ゲート絶縁膜7、ゲート電極8a,8b、ソース・ドレイン用のn+型半導体領域9b及びp+型半導体領域10bを形成してから、半導体基板1上に金属膜及びバリア膜を形成し、第1の熱処理を行って金属膜とゲート電極8a,8b、n+型半導体領域9bおよびp+型半導体領域10bとを反応させることで、金属膜を構成する金属元素MのモノシリサイドMSiからなる金属シリサイド層41を形成する。その後、バリア膜および未反応の金属膜を除去してから、第2の熱処理を行い金属シリサイド層41を安定化させる。これ以降、半導体基板1の温度が第2の熱処理の熱処理温度よりも高温となるような処理は行わない。第2の熱処理の熱処理温度は、金属元素MのダイシリサイドMSi2の格子サイズと半導体基板1の格子サイズが一致する温度よりも低くする。

(もっと読む)

基板処理装置

【課題】 基板ホルダーが移動しても、整合状態が大きく変化することなく、インピーダンスの整合状態が維持されることを課題とする。

【解決手段】上記課題を解決するため、本願に係わる基板処理装置は、処理チャンバー、前記処理チャンバー内に位置し、基板を保持するための基板ホルダー、前記基板ホルダーに高周波電力を供給するための高周波電源、前記基板ホルダーと前記高周波電源との電気的に間に位置する整合器及び前記基板ホルダーと前記整合器を一体に移動させる移動機構を有する構成とする。

(もっと読む)

半導体装置の製造方法及び半導体製造装置

【課題】シリコンエピタキシャル層と配線材料との間でショートが発生しない半導体装置の製造方法、コンタクトプラグの形成においてコンタクトホールの径の拡大を抑制する半導体装置の製造方法、これらの目的を効果的に達成できる半導体製造装置を提供する。

【解決手段】シリコン表面に形成された第1の酸化シリコン膜2と、第1の酸化シリコン膜2とは形成方法の異なる第2の酸化シリコン膜3とを有し、各々の酸化シリコン膜2,3の少なくとも一部が露出して共存するシリコン基板1を前処理する前処理工程を備えた半導体装置の製造方法であって、前記前処理工程は、第1の酸化シリコン膜2を除去して前記シリコン表面を露出させるエッチング工程を有し、前記エッチング工程は、第1の酸化シリコン膜2と第2の酸化シリコン膜3とを同じエッチングレートでエッチングすることを特徴とする。

(もっと読む)

サブクオーターミクロン適用のための、メタライゼーションに先立つ予備洗浄方法

【課題】半導体基板上のサブミクロン構造について、メタライゼーションに先立つ予備洗浄を提供する。

【解決手段】この方法は、酸素、CF4/O2の混合物またはHe/NF3の混合物のような反応性ガスのプラズマからのラジカルを用いてサブミクロン構造を洗浄することを含み、このプラズマは、好ましくは遠隔プラズマ源により発生され、ラジカルは基板が配置されるチャンバーに供給される。サブミクロン構造内に残留する自然酸化物は、好ましくは、第二の工程において水素を含むプラズマからのラジカルで還元される。第一のまたは両方の洗浄工程に続いて、当該構造は、利用可能なメタライゼーション技術によって金属で充填することができる。これは、典型的には、アルミニウム、銅またはタングステンの蒸着に先立って、露出した誘電体表面にバリア/ライナー層を蒸着することを含む。この予備洗浄およびメタライゼーション工程は、入手可能な一貫処理プラットホーム上で行うことができる。

(もっと読む)

半導体装置の製造方法

【課題】ソース・ドレイン上のシリサイドの異常成長を抑制するとともに、ソース・ドレインの接合深さを浅く保つことができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、N型ウェル103a上にゲート絶縁膜104およびゲート電極105aを形成する工程と、N型ウェル103aのうちゲート電極105aの両側方の領域にシリコンよりも大きく、P型の導電性を示す第1の元素を注入して第1のソース・ドレイン領域111cを形成する工程と、N型ウェル103aのうちゲート電極105aの両側方の領域にシリコンより小さく、P型の導電性を示す第2の元素を注入して第2のソース・ドレイン領域111dを形成する工程と、ソース・ドレイン領域111a上に金属シリサイド層112を形成する工程とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】金属シリサイド層の電気的特性のばらつきを低減することにより、半導体素子の信頼性および製造歩留まりを向上させることのできる技術を提供する。

【解決手段】半導体基板1上にニッケル−白金合金膜を形成した後、熱処理温度が210〜310℃の1回目の熱処理をヒータ加熱装置で行うことで、ニッケル−白金合金膜とシリコンとを反応させて(PtNi)2Si相の白金添加ニッケルシリサイド層33を形成する。続いて未反応のニッケル−白金合金膜を除去した後、1回目の熱処理よりも熱処理温度が高い2回目の熱処理を行い、PtNiSi相の白金添加ニッケルシリサイド層33を形成する。1回目の熱処理の昇温速度は10℃/秒以上(例えば30〜250℃/秒)とし、2回目の熱処理の昇温速度は10℃/秒以上(例えば10〜250℃/秒)とする。

(もっと読む)

半導体装置の製造方法

【課題】シリコン基板と金属プラグとの接触抵抗を安定に低減することが可能な半導体装置およびその製造方法を提供すること。

【解決手段】本発明は、シリコン基板10上に層間絶縁膜20を形成する工程と、層間絶縁膜20を選択的に異方性エッチングにすることによりコンタクトホール30を形成する工程と、コンタクトホール30の底面のシリコン基板10内をアッシング処理する工程と、アッシング処理の後、コンタクトホール30の底面を希弗酸処理する工程と、コンタクトホール30の底面においてシリコン基板10と電気的に接続する金属プラグを形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】本発明は、コンタクトプラグの高抵抗化を抑制することができ、また当該コンタクトプラグの構成材料のソース・ドレイン領域への拡散が起こらず、かつ簡略な製造プロセスにより作製可能な半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、ゲート電極4、第一の層間絶縁膜7、第一のコンタクトプラグ8、第二の層間絶縁膜9および第二のコンタクトプラグ10を有する。第一の層間絶縁膜7の上面は、ゲート電極4の上面と同じ高さ位置である。第一のコンタクトプラグ8は、第一の層間絶縁膜7の膜厚方向に貫通して形成され、下面においてソース・ドレイン領域5と電気的に接続され、第一の電気抵抗率を有する。第二のコンタクトプラグ10は、第二の層間絶縁膜9の膜厚方向に貫通して形成され、下面において第一のコンタクトプラグ8の上面と電気的に接続され、第一の電気抵抗率より低い第二の電気抵抗率を有する。

(もっと読む)

めっき方法及びその方法に用いられるめっき前処理液。

【課題】 めっき層が形成される面にニッケル下地層が設けられた配線、端子、電極部材等の被めっき素材表面に所望とする金属のめっきを施す場合、得られた該金属めっき層の剥離や該金属めっき層面のふくれ等の欠陥部分が生じないめっき方法、及びそのために使用されるめっき前処理液を提供すること。

【解決手段】 被めっき素材上に形成されたニッケル下地層の表面を、亜硝酸イオンを含有する少なくとも1種類の無機酸または有機酸からなるめっき前処理液に接触させた後に該下地層の上に金属めっきを施す。特に、前記無機酸または有機酸としてその組成中にハロゲン元素を含まない酸を用い、また、該めっき前処理液中には界面活性剤を含有させるのが好ましい。

【効果】 所望とする金属めっき層との密着性が極めて良好で、該金属めっき層の剥離や金属めっき層表面のふくれ等の欠陥の発生頻度が低減される。

(もっと読む)

自然酸化物の成長を低減するためのプラズマクリーンプロセスによるパッシベーション層の形成

本明細書に記載される実施形態は、基板上の自然酸化表面を取り除くと同時に、下層の基板表面をパッシベートするための方法を提供する。一実施形態において、プロセスチャンバ内に、酸化物層を有する基板の位置決めを行い、基板の第1の温度を約80℃未満に調整し、プロセスチャンバ内において、約10以上のNH3/NF3モル比を有するアンモニア及び三フッ化窒素を含むガス混合物からクリーニングプラズマを生成し、基板上にクリーニングプラズマを凝縮することを含む方法が提供される。ヘキサフルオロ酸アンモニウムを含む薄膜が、プラズマクリーニングプロセスの間に、自然酸化物から部分的に形成される。本方法は、さらに、プロセスチャンバ内において、約100℃以上の第2の温度まで基板を加熱しつつ、基板から薄膜を取り除き、その上にパッシベーション表面を形成することを含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極、ソース電極またはドレイン電極にタングステン膜を用いた半導体装置において、nMOSとpMOS間での抵抗差を低減可能な半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極14a,14bとソース/ドレイン拡散層16a,16bとを有するnMOS及びpMOSを形成し、ゲート電極14a,14b及びソース/ドレイン拡散層16a,16b上に、タングステン膜17を選択的に形成し、タングステン膜17を覆うように、絶縁膜(エッチングストップシリコン酸化膜18、シリコン窒化膜19)を形成し、pMOS領域12bの絶縁膜を除去し、pMOS領域12bのタングステン膜17上に、タングステン膜20を選択的に形成する。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】 電極間に抵抗成分が生じないp電極を有する窒化物半導体装置およびその製造方法を提供する。

【解決手段】 p電極12は、第1のPd膜13、Ta膜14および第2のPd膜15によって構成され、窒化物半導体から成るp型コンタクト層11上に形成される。第2のPd膜15上には、パッド電極22が形成される。第2のPd膜15は、p電極12を構成するTa膜14上部全面に形成され、Ta膜14の酸化を防止する酸化防止膜として機能する。この第2のPd膜15によって、Ta膜14が酸化されることを防止することができるので、p電極12とパッド電極22との間に生じる抵抗成分を抑制することができる。これによってp電極12とパッド電極22との接触不良を防ぐことができるので、低抵抗なp電極12を実現することができる。

(もっと読む)

101 - 120 / 272

[ Back to top ]