Fターム[4M104DD38]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | PVD (4,537) | スパッタ (3,176) | バイアススパッタ (60)

Fターム[4M104DD38]に分類される特許

21 - 40 / 60

電界効果型トランジスタ

【課題】チャネル領域を構成する有機半導体材料層と良好なオーミック・コンタクトを形成することができるソース/ドレイン電極を備えた電界効果型トランジスタを提供する。

【解決手段】電界効果型トランジスタは、ゲート電極12と、ゲート絶縁層13と、ソース/ドレイン電極21と、チャネル領域15を構成する有機半導体材料層14とを備え、ソース/ドレイン電極21は、金属から成る導体部22、及び、導体部22を少なくとも部分的に被覆し、不純物がドーピングされた有機導電材料層23から成り、有機導電材料層23を介して、チャネル領域15と導体部22との間の電気的接続が形成される。

(もっと読む)

配線を形成する方法及びプラズマスパッタリアクタ

【課題】アスペクト比の高いホール内に、被覆性の良好な、コンタクト抵抗の低いバリア層を形成する半導体装置の製造方法を提供する。

【解決手段】タンタルまたはタンタルナイトライド等のライナー材料をホール内にスパッタ堆積する。ロングスロースパッタリング、自己イオン化プラズマ(SIP)スパッタリング、誘導結合プラズマ(ICP)再スパッタリング及びコイルスパッタリングを1つのチャンバ内で組み合わせたリアクタ150を使う。ロングスローSIPスパッタリングは、ホール被覆を促進する。ICP再スパッタリングは、ホール底部のライナー膜の厚さを低減して、第1のメタル層との接触抵抗を低減する。ICPコイルスパッタリングは、ICP再スパッタリングの間、再スパッタリングによる薄膜化は好ましくないホール開口部に隣接しているような領域上に、保護層を堆積する。

(もっと読む)

半導体装置の製造方法

【課題】保護素子としてSBDを搭載したMOSFETにおいては、SBDの特性を確保するためアルミニウム・ソース電極下のアルミニウム拡散バリア・メタル膜として、TiW(タングステンを主要な成分とする合金)膜が使用される。しかし、本願発明者らが検討したところによると、タングステン系バリア・メタル膜はTiN等のチタン系バリア・メタル膜と比べて、バリア性が低い柱状粒塊を呈するため、比較的容易にシリコン基板中にアルミニウム・スパイクが発生することが明らかとなった。

【解決手段】本願発明は、アルミニウム系メタル層と下層のシリコン系半導体層の間のバリア・メタル層として、タングステン系バリア・メタル膜をスパッタリング成膜によって形成する際、その下層をウエハ側にバイアスを印加したイオン化スパッタにより成膜し、上層をウエハ側にバイアスを印加しないスパッタにより成膜するものである。

(もっと読む)

金属シリサイド形成のための方法および装置

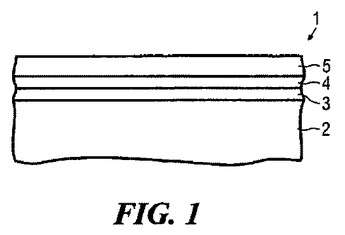

本明細書で述べられる実施形態は、無拡散アニールプロセスを使用して金属シリサイド層を形成する方法を包含する。一実施形態では、基板上に金属シリサイド材料を形成するための方法が、提供される。その方法は、基板のシリコン含有表面を覆って金属材料を堆積させるステップと、金属材料を覆って金属窒化物材料を堆積させるステップと、金属窒化物材料を覆って金属接点材料を堆積させるステップと、基板を無拡散アニールプロセスにさらして金属シリサイド材料を形成するステップとを含む。無拡散アニールプロセスの短い時間枠は、窒素がシリコン含有界面に拡散して窒化シリコンを形成する時間を低減し、それ故に界面抵抗を最小限にする。  (もっと読む)

(もっと読む)

銅配線基板の製造方法

【課題】 電気抵抗のさらなる低減化と基板表面に対する銅薄膜の密着性の確保との両方を高いレベルで達成することができ、かつスパッタリングプロセスで用いられる金属ターゲット材のコスト削減やそれを用いたスパッタリングプロセスを中心として全体的な製造プロセスのコスト低減を達成することを可能とした、銅配線基板の製造方法を提供する。

【解決手段】 本発明の銅配線基板の製造方法は、ガラスまたは石英からなる基板1の表面2に、例えばArガスのような不活性ガスのプラズマ4を照射することで、その表面2に改質を施して、その基板1の表面2自体における純Cuに対する密着性を向上させ、その基板1の表面2の直上に、銅薄膜3をスパッタリングによって形成することを特徴としている。

(もっと読む)

凹状のドレイン及びソース区域並びに非共形的な金属シリサイド領域を有するMOSトランジスタを備えたCMOSデバイス

【解決手段】

凹状のドレイン及びソース構造のトランジスタ(150)における非共形的金属シリサイド層(156)は、歪誘起メカニズム、ドレイン/ソース抵抗等に関して高い性能を提供することができる。このために場合によっては、シリサイド化プロセスに先立ちアモルファス化注入プロセスが実行されてよい一方で、他の場合には高融点金属(156)の異方的な堆積が用いられてよい。

(もっと読む)

貴金属膜の成膜装置及び貴金属膜の成膜方法

【課題】基板に形成されたホールの内部にスパッタリングにより成膜した貴金属膜の厚みを、ホールの両サイドで対称なものとすることができ、したがって、貴金属膜に断線等の不具合が生じる虞がなく、信頼性をより向上させることができる貴金属膜の成膜装置及び貴金属膜の成膜方法を提供する。

【解決手段】本発明の貴金属膜の成膜装置は、基板23に形成されたホールの内部に貴金属膜をスパッタリングにより成膜する装置であり、ターゲット24と、このターゲット24に対向配置されるステージ22と、ターゲット24にスパッタリング電力Pt(W)を印加する電源26とを備え、ターゲットの直径Tと、ターゲット24とステージ22上の基板23との距離Lとの比L/Tを、0.5以上かつ1.5以下の範囲で変更可能とした。

(もっと読む)

スパッタリング装置および金属化構造体を製造する方法

複数のパルスで陽極とターゲット間に電力を印加することによってTaN層(4)を被着し、ターゲットから基板(2)へ反応的にTaをスパッタしてTaNシード層(4)を形成する方法から成る。Ta層(5)は複数のパルスにおける電力を印加すると共に、前記基板(2)を支持するペデスタルに高い周波数信号を印加することによって前記TaNシード層(4)の上に被着され、前記基板(2)に隣接した自己バイアス場を生成する金属化構造体(1)を被着する方法。  (もっと読む)

(もっと読む)

薄膜の形成方法、プラズマ成膜装置及び記憶媒体

【課題】被処理体の表面の凹部の開口部近傍にオーバハング部が形成されることを防止し、この結果、ピンチオフやボイドを発生させることなく凹部内を埋め込むことが可能な薄膜の形成方法を提供する。

【解決手段】高融点金属よりなる金属ターゲット96をスパッタしつつ発生した金属粒子をプラズマでイオン化し、載置台60上に載置された表面に凹部を有する被処理体2の表面に前記イオン化された金属粒子をバイアス電力により引き込んで高融点金属を含む薄膜を堆積する成膜工程を有する薄膜の形成方法において、被処理体を、堆積されつつある薄膜がフローを生ずるようなフロー温度に加熱した状態に維持するようにする。これにより、表面拡散を生ぜしめて被処理体の表面の凹部の開口部近傍にオーバハング部が形成されることを防止する。

(もっと読む)

半導体装置およびその製造方法

【課題】層間絶縁膜の損傷を抑えながらタンタルを主成分とするバリア膜をスパッタによって成膜する半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜113上に、キセノンガスを用いたスパッタリングで、タンタルまたは窒化タンタルを主成分とするバリア膜116を形成するスパッタ成膜工程を備える。スパッタ成膜工程は、層間絶縁膜113の上に、基板にRFバイアスを印加して行うキセノンガスを用いるスパッタリングにより、窒化タンタルを主成分とするバリア膜116Aを形成する工程と、RFバイアスを印加せずに行うキセノンガスを用いるスパッタリングにより、バリア膜116Aの上に、タンタルを主成分とするバリア膜116Bを形成する工程とを備えてもよい。バリア膜116はRFバイアスを連続的に変化させて、層間絶縁膜113側をRFバイアスを印加して、配線層117側をRFバイアスを印加せずに形成することもできる。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクト抵抗をより一層低減することができる半導体装置及びその製造方法を提供する。

【解決手段】コンタクトホール22の側面及び下面並びに層間絶縁膜21上にバリアメタル膜23を形成する。次に、バリアメタル膜23を覆うニッケル膜24をスパッタリング法により形成する。次に、ニッケル膜24を覆うと共に、コンタクトホール22を埋め込むタングステン膜25を熱CVD法により形成する。そして、CMP法により層間絶縁膜21上のバリアメタル膜23、ニッケル膜24及びタングステン膜25を除去する。

(もっと読む)

アルミニウム相互接続部の制御された表面酸化

【課題】集積回路のためのアルミニウム相互接続部メタライゼーションを、所望によりアルゴンが追加されてもよい純粋な酸素雰囲気中で制御可能に酸化させる。

【解決手段】ウエハ32をアルミニウムスパッタリング中に生じる300℃を超える温度からアルミめっきを施したウエハをプラスチックカセット34に装填させることを可能にする100℃未満まで冷却させるので有利に行われる。酸化は高真空搬送チャンバ62と低真空搬送チャンバ40の間の通過チャンバ56、80内で制御可能に行うことができる。酸素分圧は有利には0.01〜1トール、好ましくは0.1〜0.5トールである。1トールを超える全圧にアルゴンを添加すると、ウエハが水冷却ペデスタル上に載置された場合にウエハ冷却が促進される。スパッタチャンバへの酸素逆流を防止するために冷却チャンバは冷却中に真空ポンプで排気されず最初にアルゴンが次に酸素が冷却チャンバにパルスされる。

(もっと読む)

ダメージフリー被覆刻設堆積法

【課題】 周辺表面を殆ど汚染又は乱さずに、スパッタリングされたキャリア/バリヤ層を堆積させて所望の形状に刻設する方法を提供する。

【解決手段】 堆積層のイオンの衝突により浸食・汚染されないように、刻設された層の適用された表面が保護される、イオン堆積スパッタリング法を用いて刻設された材料層を半導体の特徴表面に適用する方法であり、刻設された層の第1の部分を、その層の適用される表面が浸食又は汚染されない程度に基板バイアスを十分低くして適用するステップと、刻設された層の次の部分を、さらなる層材料を堆積させながら、第1の部分からの形状を刻設可能な程度に基板バイアスを十分高くして適用するステップとを含む。この方法は、半導体の特徴表面上にバリヤ層、ウェッティング層及び導電層等を刻設するのに特に適しており、導電層が銅である場合は特に有益である。

(もっと読む)

半導体装置の製造方法

【課題】バリアメタルが薄い場合でもAl配線のモフォロジ及びエレクトロマイグレーションを改善することができる半導体装置の製造方法を得る。

【解決手段】まず、半導体基板11上にSiO2層間膜13(酸化膜)を形成する。次に、SiO2層間膜13上にTi膜18を形成する。次に、Ti膜18上にTiN膜32を形成する。次に、TiN膜32上にAl配線33を形成する。ここで、Ti膜18を形成する工程において、圧力が0.3Pa以下の雰囲気中で物理気相成長法を用いる。これにより、Ti膜18とSiO2層間膜13との間にTiO2膜31が形成される。

(もっと読む)

スパッタ成膜方法及びスパッタ成膜装置

【課題】1個の処理容器内でスパッタによって厚さ方向に濃度勾配を有するように添加金属を含んだ合金層を被処理体上に容易に形成することができる技術を提供すること。

【解決手段】添加金属と主金属とを含む合金からなる金属ターゲットを備えた処理容器内にプラズマ発生用のガスを供給すると共にこのガスに電力を供給してプラズマ化し、そのプラズマによりスパッタされた金属ターゲット粒子により第1の合金膜を被処理体に成膜する第1の成膜工程と、処理容器内の圧力及び前記電力の少なくとも一つを異ならせてプラズマを発生させ、スパッタされた前記金属ターゲットの粒子により、添加金属の濃度が第1の合金膜の添加金属の濃度とは異なる第2の合金膜を第1の合金膜に積層する第2の成膜工程と、を含むようにスパッタ成膜を行い、主金属に対する添加金属の濃度が厚さ方向に異なる膜を成膜することができる。

(もっと読む)

再スパッタされる銅シード層

【課題】段差被覆性に優れた銅シード層の製造方法を提供する。

【解決手段】同じスパッタチャンバ内で実行される堆積された銅のスパッタエッチング162が、銅のスパッタ堆積160の後に続いて実行される。これにより、特に銅の電気めっきの前に、狭いビア内に銅シード層を形成するのに有用な銅堆積プロセスとなる。該堆積は、高い銅イオン化割合及び銅イオンを該ビア内に引き付ける強力なウェーハバイアスを促進する条件下で実行される。該エッチングは、好ましくは、該チャンバの周りのRFコイルによって誘導励起されたアルゴンイオンによって、又は、高いターゲット電力及び極めて強いマグネトロンで形成することができる銅イオンによって、あるいは、RFコイルの使用によって行うことができる。堆積/エッチングの2つ以上のサイクルを実行することができる。最後の瞬時堆積168は、高い銅イオン化及び低いウェーハバイアスで実行することができる。

(もっと読む)

位置制御型デュアルマグネトロン

【課題】ターゲットの中心部に再堆積された材料物質が、該ターゲットから剥がれて、集積回路に欠陥をもたらさない、再堆積物質を洗浄する装置を提供する。

【解決手段】スパッタリング用デュアルマグネトロンにおいて、該マグネトロンの位置は、スパッタ堆積とターゲット洗浄の間で、相補的半径方向に動かすことができる。該マグネトロンは、異なる特徴のサイズ、強度及び不平衡を有する。該ソースマグネトロンは、より小さく、より強く、かつアンバランスのソースマグネトロン62であり、スパッタ堆積及びエッチングにおいて、ウェーハのエッジ近くに位置している。該補助マグネトロン64は、より大きく、弱く、かつより平衡しており、該ターゲットの中心を洗浄し、スパッタ堆積において、スパッタイオンを該ソースマグネトロンからガイドするのに使用される。

(もっと読む)

半導体装置のCu配線およびその製造方法

【課題】本発明の目的は、配線溝や層間接続路表面に形成されたTaNからなるバリア層との密着性が良好なCu配線と、このCu配線を製造できる方法を提供する。本発明の他の目的は、半導体基板上の絶縁膜に形成された配線溝や層間接続路の幅が狭く、深い場合でも、バリア層との密着性が良好で、配線溝や層間接続路の隅々に亘って埋め込まれているCu配線と、このCu配線を製造できる方法を提供する。

【解決手段】半導体基板上の絶縁膜に形成された配線溝または層間接続路に埋め込まれたCu配線を、(1)配線溝側または層間接続路側に形成されたTaNからなるバリア層と、(2)Pt、In、Ti、Nb、B、Fe、V、Zr、Hf、Ga、Tl、Ru、ReおよびOsよりなる群から選ばれる1種以上の元素を合計で0.05〜3.0原子%含有するCuからなる配線本体部とで構成すればよい。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】Al膜の埋め込み性を向上させた半導体装置の製造方法、及び半導体装置の製造装置を提供するものである。

【解決手段】制御部は、ビアホールVHを有したシリコン基板Sの表面に金属膜BM1(Ti膜)と金属窒化膜BM2(TiN膜)を被覆させ、金属窒化膜BM2に被覆されたビアホールVHの内部にCVD法を用いてAl−CVD膜P1を形成させた。そして、制御部は、Al−CVD膜P1を埋め込む前に、ビアホールVHの底部に位置する金属窒化膜BM2の一部をスパッタし、ビアホールVHの底部の側壁に再付着窒化膜BMrを形成させた。

(もっと読む)

電極被覆材料、電極構造体、及び、半導体装置

【課題】低いコンタクト抵抗、高い移動度を達成し得る半導体装置を提供する。

【解決手段】ゲート電極13、ゲート絶縁層14、有機半導体材料層から構成されたチャネル形成領域16、及び、金属から成るソース/ドレイン電極15を有する電界効果型トランジスタから成る半導体装置において、チャネル形成領域16を構成する有機半導体材料層と接するソース/ドレイン電極15の部分は、電極被覆材料21で被覆されており、電極被覆材料21は、金属イオンと結合し得る官能基、及び、金属から成るソース/ドレイン電極15と結合する官能基を有する有機分子から成る。

(もっと読む)

21 - 40 / 60

[ Back to top ]