Fターム[4M104FF07]の内容

Fターム[4M104FF07]に分類される特許

261 - 276 / 276

半導体装置

【課題】 縦型MOSFETのゲート抵抗・入力容量間のトレードオフを改善する。

【解決手段】 半導体装置は、第1導電型の半導体基板と、半導体基板上に形成された第1導電型の半導体領域と、半導体領域の一部分に選択的に形成されたトレンチと、トレンチ内に少なくともその一部分が位置すると共にその延長された上端部分が段部を介して幅広に形成されたゲート電極と、トレンチの壁面に沿って前記ゲート電極との間に形成されたゲート絶縁膜と、半導体領域上で前記ゲート絶縁膜を介してトレンチ底部を除く側壁を囲むように設けられた第2導電型のベース層と、ベース層の上面付近のトレンチの外側にゲート絶縁膜に隣接して形成された第1導電型のソース領域と、ゲート電極のトレンチより延長されてトレンチ内の幅よりも段部を介して幅広に形成された上端部分の下面とソース領域の上面との間の少なくとも一部に形成されると共にトレンチ内のゲート絶縁膜の膜厚よりもその膜厚が厚くなるように形成された絶縁膜と、を備える。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】従来と同等の駆動力を確保しつつ、ヘテロ界面で生じる漏れ電流を低減することが可能な高耐圧電界効果トランジスタを容易に製造する。

【解決手段】基板1とドレイン領域2からなる半導体基体の一主面側に第二のヘテロ半導体領域形成用半導体層400を積層する工程と、所定の開口14を有するマスク層9をマスクとして用いて、第二のヘテロ半導体領域形成用半導体層400を選択的にエッチングして第二のヘテロ半導体領域4を形成する工程と、マスク層9を有した状態で、第一のヘテロ半導体領域形成用半導体層300を積層する工程と、第一のヘテロ半導体領域形成用半導体層300を選択的にエッチングして第一のヘテロ半導体領域3を形成する工程と、第一のヘテロ半導体領域3並びに半導体基体に接するようにゲート絶縁膜5を形成する工程を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】遮断状態においてゲート電極近傍のヘテロ接合界面で生じる漏れ電流を低減する。

【解決手段】第一導電型の基板1とドレイン領域2からなる半導体基体と、該半導体基体の一主面に接し、該半導体基体とはバンドギャップが異なるヘテロ半導体領域3と、ヘテロ半導体領域3と前記半導体基体との接合部にゲート絶縁膜4を介して形成されたゲート電極5と、ヘテロ半導体領域3と接続されたソース電極6と、前記半導体基体とオーミック接続されたドレイン電極7とを有する半導体装置において、少なくともゲート電極5が第二導電型の半導体材料からなる。

(もっと読む)

電界効果トランジスタ

T字型ゲート(10)を有する電界効果トランジスタにおいて、ゲートはネック部(16)と該ネック部から張り出したTバー部(18)とを有し、ネック部(16)は複数の相隔てられたピラー(20)を有する。ネック部を複数の相隔てられたピラーから形成することにより、ゲートとチャネルとの接触面積すなわち“実効ゲート幅”が狭くされる一方で、Tバー部(18)がピラー(20)を橋渡しすることによりゲートを通じての電気的な連続性を確保している。これにより入力ゲート容量が低減され、向上されたデバイス性能を備えたFETがもたらされる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧に優れ、強度の高いIII−V族窒化物半導体からなる半導体装置を実現する。

【解決手段】本発明の構造では、第1のソース電極106がバイアホール112を介して導電性基板101に接続されており、また、第2のソース電極110が形成されている。これにより、ゲート電極108とドレイン電極107との間に高い逆方向電圧が印加されても、ゲート電極108のうちドレイン電極107に近い側の端部に起こりやすい電界集中を効果的に分散または緩和することができるため、耐圧が向上する。また、素子形成層を形成する基板として導電性基板101を用いているため、導電性基板101には裏面まで貫通するバイアホールを設ける必要がない。したがって、導電性基板101に必要な強度を保持したまま、第1のソース電極106と裏面電極115とを電気的に接続することができる。

(もっと読む)

半導体装置及びその製造方法、並びに、ゲート電極及びその製造方法

【課題】通常の紫外線露光により形成したゲート電極開口を厚肉化して開口寸法を縮小することにより、微細なゲート電極を効率的に製造可能な半導体装置の製造方法等の提供。

【解決手段】本発明の半導体装置の製造方法は、ゲート電極形成対象面上に、紫外線レジスト層2を少なくとも1層含むゲート電極開口形成用層を形成し、該ゲート電極開口形成用層にゲート電極開口10aを形成するゲート電極開口形成工程と、前記ゲート電極開口形成用層上に、ゲート電極におけるオーバーゲート部を形成するためのオーバーゲート形成用層3,4を形成するオーバーゲート形成用層形成工程と、前記ゲート電極開口の開口径を縮小させるゲート電極開口縮小工程と、前記ゲート電極開口にゲート電極30を形成するゲート電極形成工程とを含むことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】同一の半導体基板上に、2種類以上のゲート絶縁膜及びゲート電極を有するMIS型トランジスタを備えた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板11の第1のNMISトランジスタ形成領域AreaAには、ハフニウム酸化膜のような金属酸化膜からなるゲート絶縁膜21aとタングステン膜のような金属膜からなるゲート電極22aを有する第1のNMISトランジスタを形成する。また、半導体基板11の第2のNMISトランジスタ形成領域AreaCには、シリコン酸化膜からなるゲート絶縁膜13とポリシリコン膜のような半導体材料からなるゲート電極14cを有する第2のNMISトランジスタを形成する。ゲート電極22aは、ゲート電極14cと同時に形成した第1のダミーゲート電極14aを除去して設けられたゲート電極形成用開口20a内に金属膜を埋め込んで形成されたダマシン構造を有する。

(もっと読む)

半導体装置の作製方法

【課題】 ゲート容量が小さく、短チャネル効果が抑制された薄膜トランジスタ(TFT)を作製する。またゲート配線の配線抵抗を減少させ、回路面積の減少とTFTの高速駆動を可能にする。

【解決手段】 ゲート電極を二層にし、下層の幅を上層よりも小さくすることにより、ゲート電極と半導体膜からなる活性層の重なる面積が小さくなる。これによりゲート容量を減少させ、短チャネル効果を抑制することができるので、TFTを高速駆動させることが可能である。また、ゲート電極と配線を一体形成せず別々に形成することによって、TFTによって構成される回路面積も縮小でき、高速化に寄与できる。

(もっと読む)

半導体装置の作製方法

【課題】 ナノインプリント法を用いることでコストを抑えることができる、半導体装置の作製方法の提案を課題とする。

【解決手段】 本発明は、島状の半導体膜上にゲート絶縁膜と、導電膜と、レジストとを順に形成し、パターンが形成されたモールドをレジストに押し付けた状態でレジストの硬化を行なうことで、パターンをレジストに転写し、導電膜の一部が露出するまでパターンが転写されたレジストの表面をアッシングし、アッシングされたレジストをマスクとして用い、導電膜をエッチングすることを特徴とする。

(もっと読む)

半導体素子の製造方法

【課題】 簡単な方法によりゲート電極を斜めに傾け、ゲート長を短縮することができる半導体素子の製造方法を得る。

【解決手段】 まず、半導体基板11上にゲート電極15を形成する。次に、半導体基板上にゲート電極の一方の側面のみに接触するようにレジスト16を形成する。そして、レジストを収縮又は膨張させることによりゲート電極を傾ける。ここで、ゲート電極の断面形状をΓ型、T型又はY型とするのが好ましい。また、ゲート電極をソース側へ傾けるのが好ましい。

(もっと読む)

複数のフィールドプレートを有するワイドバンドギャップトランジスタ

ソース電極およびドレイン電極が半導体層に接触した、基板上の複数の活性半導体層を備えるトランジスタ。ゲートが、ソース電極とドレイン電極との間に、複数の半導体層上に形成される。複数のフィールドプレートが、半導体層上に配置され、各フィールドプレートは、ゲートのエッジからドレイン電極に向かって延び、また各フィールドプレートは、前記半導体層から、また他のフィールドプレートから分離される。最上部のフィールドプレートは、ソース電極に電気的に接続され、他のフィールドプレートは、ゲートまたはソース電極に電気的に接続される。  (もっと読む)

(もっと読む)

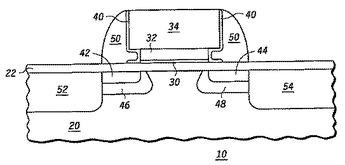

切り欠き制御電極及び当該電極の構造を有する半導体素子の製造方法

半導体素子(10)を形成する方法では、一の表面を有する基板(20)を設け、絶縁層(22)を基板(20)の表面の上に形成し、第1パターニング済み導電層(30)を絶縁層(22)の上に形成し、第2パターニング済み導電層(32)を第1パターニング済み導電層(30)の上に形成し、パターニング済み非絶縁層(34)を第2パターニング済み導電層(32)の上に形成し、そして第1及び第2パターニング済み導電層(30,32)の一部分を選択的に除去して、半導体素子(10)の切り欠き制御電極を形成する。  (もっと読む)

(もっと読む)

デバイス製造方法および基板

電磁放射線を用いた一回の露光プロセスでT−ゲートを製造する方法が開示される。  (もっと読む)

(もっと読む)

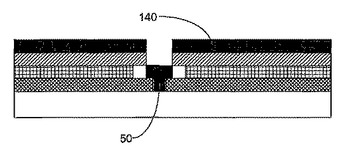

電極規定層を包含する窒化ガリウム材料デバイスおよびその形成方法

窒化ガリウム材料デバイスおよびその形成方法を提供する。該デバイスは、電極規定層を包含する。電極規定層は典型的にはその内部に形成されたビアを有し、該ビア内に電極が(少なくとも部分的に)形成される。したがって、ビアは、電極の寸法を(少なくとも部分的に)規定する。いくつかの場合において、電極規定層は、窒化ガリウム材料領域上に形成された不動態化層である。 (もっと読む)

III族窒化物素子の不動態化およびその方法

【課題】

【解決手段】III族窒化物半導体素子およびその製造方法の実施形態は、高温処理中にIII族窒化物材料に損傷を与えずに、素子のコンタクトを形成することを可能にする低抵抗の不動態化層を備えてよい。不動態化層は、素子全体を不動態化するために用いられてよい。不動態化層は、さらに、素子のコンタクトと活性層との間に設けられて、導電のための低抵抗の電流路を提供してもよい。この不動態化処理は、FET、整流器、ショットキダイオードなど、任意の種類の素子に用いて、破壊電圧を改善すると共に、コンタクトの接合部付近の電界集中効果を防止してよい。不動態化層は、外部拡散に関してIII族窒化物素子に影響を与えない低温アニールで活性化されてよい。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート長の短いゲート電極を有し、しかも低抵抗で高周波特性が優れている半導体装置およびその製造方法を提供する。

【解決手段】少なくともノンドープInGaP層又はノンドープInAlGaP層からなる上層半導体層12と、この上層半導体層直下にGaAs層またはAlGaAs層からなる下層半導体層11を含む半導体基板に、上層半導体層表面から上層半導体層への浸入が、下層半導体層で略停止するショットキーゲート電極15と、このショットキーゲート電極部に接続して第1の電極の抵抗を低減する第2の電極部16からなるT字型ゲート電極を形成する。

(もっと読む)

261 - 276 / 276

[ Back to top ]