Fターム[4M104FF07]の内容

Fターム[4M104FF07]に分類される特許

61 - 80 / 276

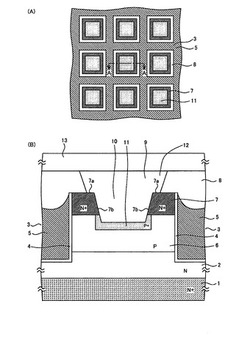

半導体装置及びその製造方法

【課題】微細化されたN+型ソース層とソース電極のコンタクト抵抗が低減されたパワーMOSトランジスタの実現を図る。

【解決手段】N型ドリフト層2の表面にP型ボディ層6を形成し、該P型ボディ層6の表面にN+型ソース層7を形成する。N+型ソース層7上を被覆する層間絶縁膜8に第1のコンタクトホール9を形成し、N+型ソース層7の一部を露出する。第1のコンタクトホール9の底面に露出したN+型ソース層7の表面からP型ボディ層6内まで第2のコンタクトホール10を形成する。第2のコンタクトホール10の底面に露出したP型ボディ層6の表面にP+型コンタクト層11を形成する。第1のコンタクトホール9の底面にフォトリソグラフィ工程のマスク合わせ精度のばらつき幅より小さい幅のN+型層7aを形成し、第1、第2のコンタクトホール9、10内をタングステン層12等で埋設する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】化合物半導体層の表面におけるダングリングボンドを確実に低減させて閾値電圧の変動を抑えて安定化させ、高いトランジスタ特性を得ることができる信頼性の高い化合物半導体装置を実現する。

【解決手段】電極溝2Cの内壁面を含む化合物半導体層2の表面は、電極溝2Cを形成する際のドライエッチングによるエッチング残渣物12a及び変質物12bが除去されて、化合物半導体がフッ素(F)で終端されており、この電極溝2Cをゲート絶縁膜6を介してゲートメタルで埋め込み、或いは電極溝2Cを直接的にゲートメタルで埋め込んで、ゲート電極7が形成される。

(もっと読む)

保護素子およびそれを備えた半導体装置

【課題】被保護素子に接続されることにより、被保護素子の破壊を未然に防止できる保護素子を提供すること。

【解決手段】アノード電極15とカソード電極16との間に主たる電流を流す被保護素子に対して、電気的に並列に接続される保護素子1であって、GaN層13よりもバンドギャップの大きなAlGaN層14が形成され、AlGaN層14の表面に離間してアノード電極15とカソード電極16とが形成され、アノード電極15とカソード電極と16の間の2次元電子ガス層13Aを流れる電流のオンオフを制御する制御電極19を備えたオンオフ可能領域21を備え、制御電極19が所定の抵抗体20を介してアノード電極15に接続されてなり、アノード電極15が被保護素子のアノード電極15と接続され、カソード電極16が被保護素子のカソード電極16と接続され、被保護素子より耐圧が低く設定されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ファインゲート構造を採用してゲート電極の微細化を図るも、ゲート電極の周辺における電界集中によるデバイス特性の変動・劣化を防止する、信頼性の高い化合物半導体装置を実現する。

【解決手段】ゲート電極8は、ファインゲート構造の幹状の下方部分8aと、下方部分8aの上端から当該上端よりも幅広に傘状(オーバーハング形状)に拡がる上方部分8bとが一体形成されており、下方部分8aは、下端を含む第1の部分8aaと、第1の部分8aa上の第2の部分8abとを有し、保護壁7は、第1の部分8aaの両側面のみを覆うように形成されている。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

電極規定層を包含する窒化ガリウム材料デバイスおよびその形成方法

【課題】窒化ガリウム材料デバイスおよびその形成方法を提供する。

【解決手段】該デバイスは、電極規定層24を包含する。電極規定層は典型的にはその内部に形成されたビア26を有し、該ビア内に電極18が(少なくとも部分的に)形成される。したがって、ビアは、電極の寸法を(少なくとも部分的に)規定する。いくつかの場合において、電極規定層は、窒化ガリウム材料領域上に形成された不動態化層である。

(もっと読む)

保護層および低損傷陥凹部を備える窒化物ベースのトランジスタならびにその製作方法

【課題】窒化物ベースの半導体チャネル層上に窒化物ベースの半導体バリア層を形成すること、および窒化物ベースの半導体バリア層のゲート領域上に保護層を形成することによって、トランジスタが製作される。

【解決手段】パターニングされたオーム性接触金属領域が、バリア層上に形成され、第1および第2のオーム性接触を形成するためにアニールされる。アニールは、保護層をゲート領域上に載せたままで実施される。バリア層のゲート領域上に、ゲート接点も形成される。ゲート領域内に保護層を有するトランジスタも形成され、バリア層の成長させたままのシート抵抗と実質的に同じシート抵抗をもつバリア層を有するトランジスタも同様である。

(もっと読む)

半導体装置及びその製造方法

【課題】接続不良の発生を抑制することのできる、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、所定ピッチで所定の幅の素子領域が形成された半導体基板と、半導体基板上に積層された層間絶縁膜と、層間絶縁膜の上面から半導体基板の素子領域にかけて設けられ素子領域に接続される第1コンタクトとを備える。第1コンタクトは、素子領域上の層間絶縁膜に形成された素子領域の幅よりも大きい径を有するコンタクトホールと、コンタクトホールの底部に設けられ、素子領域に達する開口を有するスペーサ膜と、スペーサ膜の開口を介して素子領域に接続されるようにコンタクトホール内に埋め込まれたコンタクトプラグとを有する。

(もっと読む)

シングルゲートまたはマルチゲートフィールドプレート製造

【課題】電界効果型トランジスタの表面に、誘電性材料の堆積/成長させ、誘電性材料をエッチングし、および、メタルを蒸着させる、連続的なステップを用いる、シングルゲートまたはマルチゲートプレートの製造プロセスの提供。

【解決手段】本製造プロセスは、誘電性材料の堆積/成長が、典型的には、非常によく制御できるプロセスなので、フィールドプレート動作を厳しく制御できる。さらに、デバイス表面に堆積された誘電性材料は、デバイスの真性領域から除去される必要はない。このため、乾式または湿式のエッチングプロセスで受けるダメージの少ない材料を用いることなく、フィールドプレートされたデバイスを、実現することができる。マルチゲートフィールドプレートを使うと、マルチ接続を使用するので、ゲート抵抗を減らすこともでき、こうして、大周辺デバイスおよび/またはサブミクロンゲートデバイスの性能を向上することができる。

(もっと読む)

ヘテロ接合電界効果トランジスタ及びその製造方法

【課題】電流コラプスを抑制し、且つゲートリーク電流を低減するヘテロ接合電界効果トランジスタとその製造方法の提供を目的とする。

【解決手段】本発明に係るヘテロ接合電界効果トランジスタは、バリア層40及びバリア層40上に形成されたキャップ層50を含む窒化物半導体層と、前記窒化物半導体層に下部を埋没するようにして前記窒化物半導体層上に設けられたゲート電極90と、前記窒化物半導体層上に形成されたSiを含まない絶縁膜からなる表面保護膜100とを備える。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタが設計より低い閾値電圧で動作し始めるという寄生トランジスタ動作を抑制する。

【解決手段】半導体装置100は、基板102の素子形成領域に形成されたトレンチ162、トレンチ162の側壁および底面に形成されたゲート絶縁膜120、トレンチ162を埋め込むようにゲート絶縁膜120上に形成されたゲート電極122、基板102表面のゲート長方向の一方の側に形成されたソース領域112、およびゲート長方向の他方の側に形成されたドレイン領域113、を有するトランジスタを含む。ここで、ゲート電極122は、トレンチ162外部の基板102上にも露出して形成され、ゲート電極122は、ゲート長方向における、トレンチ162の両端部上部が覆われるとともに、中央部に少なくとも一つ深さが基板まで達する凹部が形成されるように設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタが設計より低い閾値電圧で動作し始めるという寄生トランジスタ動作を抑制する。

【解決手段】半導体装置100は、ゲート幅方向に断続的に深さが変化する複数のトレンチ162、各複数のトレンチ162の側壁および底面に形成されたゲート絶縁膜120、ゲート絶縁膜120上に形成されたゲート電極122、基板102表面のゲート長方向の一方の側に形成されたソース領域112およびゲート長方向の他方の側に形成されたドレイン領域113を有するトランジスタを含む。ここで、トレンチ162の側壁の基板102の表面から底面に向かう途中の位置から底面までの下部分におけるゲート絶縁膜120の膜厚が、当該側壁の途中の位置から表面までの上部分におけるゲート絶縁膜120の膜厚よりも厚く、かつ底面におけるゲート絶縁膜120の膜厚以上である。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法および電子装置

【課題】ゲートリーク電流の増加が抑制された信頼性の高い電界効果トランジスタを提供する。

【解決手段】 ゲート電極は、第1金属層16および第2金属層17を含み、

第2金属層17は、第1金属層16よりも導電率が高く、

第1金属層16の上方に、第2金属層17が積層され、

ソース電極18およびドレイン電極19は、半導体層12〜14上にオーム性接触し、

ゲート電極は、ソース電極18およびドレイン電極19の間に配置され、かつ、第1金属層16により半導体層上にショットキー性接触し、

半導体層上におけるソース電極18およびゲート電極の間、ならびに、ゲート電極およびドレイン電極19の間は、絶縁膜15Aにより覆われ、

かつ、

第2金属層17下面の全体が第1金属層16上面の上方に重なっているか、または、第1金属層16の厚みが絶縁膜15Aの厚み以上であることを特徴とする電界効果トランジスタ。

(もっと読む)

バイポーラトランジスタ

【課題】高速動作性・高電流駆動力を有するヘテロ接合バイポーラトランジスタ及びその製造方法を提供する。

【解決手段】バイポーラトランジスタは、コレクタとして機能するSi単結晶層3と、Si単結晶層3の上に形成された単結晶のSi/SiGeC層30a及び多結晶のSi/SiGeC層30bと、エミッタ開口部を有する酸化膜31と、エミッタ電極50と、エミッタ層35とを備えている。単結晶のSi/SiGeC層30aに真性ベース層52が形成され、単結晶のSi/SiGeC層30aの一部と多結晶のSi/SiGeC層30bとCoシリサイド層37bとにより、外部ベース層51が構成されている。エミッタ電極の厚みは、エミッタ電極50に注入されたボロンがエミッタ電極50内を拡散して、エミッタ−ベース接合部まで達しないように設定されている。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧向上や短チャンネル効果の抑制を可能とする半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、半導体基板であるSiC基板1上に形成された、バッファ層2と、バッファ層2上に形成された、バッファ層2よりもバンドギャップが小さいチャネル層3と、チャネル層3上に形成された、チャネル層3よりもバンドギャップが大きいバリア層4と、バリア層4上に互いに離間して形成された、ソース、ドレイン電極7、8と、ソース、ドレイン電極7、8下から、バリア層4を通ってチャネル層3中にそれぞれ達する、不純物領域5とを備え、不純物領域5の下端は、バッファ層2に達しない。

(もっと読む)

ヘテロ接合バイポーラトランジスタおよびその製造方法

【課題】ヘテロ接合バイポーラトランジスタのエミッタメサがより正確に形成できるようにする。

【解決手段】第1エミッタ電極107bの側部には、例えば酸化シリコンからなる庇部108が形成され、また、少なくともキャップ層106を含んで構成されたエミッタメサの露出している側面から庇部108の下部の領域のレッジ構造部105aにかけて形成された、例えば窒化シリコンからなる被覆層109が形成されている。被覆層109が、庇部108の側面,庇部108の下面,エミッタメサの側部,およびレッジ構造部105aの上にかけて形成されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体基板上の金属電極と半導体基板の界面に、現像残渣のない半導体装置を提供すること。

【解決手段】半導体基板上に、金属電極が設けられた半導体装置であって、金属電極は、半導体基板の上面視において、細線部と、細線部の電極の長手方向の両端に太線部と、細線部から太線部へ向けて線幅が漸増する線幅漸増部とからなり、細線部の側面と線幅漸増部の側面の境界領域に、曲率を有す円弧が付けられた形状であることを特徴とする半導体装置。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ゲート電極の形成工程におけるフォトレジスト層を露光した際に、露光不良によりレジスト残渣が発生しないようにすること。

【解決手段】本発明の電界効果トランジスタ100は、半導体基板1上にゲート電極を備えた電界効果トランジスタで、半導体基板1上に設けられた誘電体膜2と、この誘電体膜2の開口部に設けられたフット部8と、このフット部8上及び誘電体膜2上に設けられたヘッド部9とを備え、誘電体膜の膜厚t1が、0.9k×λ/2|n1−n2|<t1<1.1k×λ/2|n1−n2|(ただしkは自然数であり、屈折率n1は所定の波長λを有する露光光に対する誘電体膜の屈折率n1(>2.1)、屈折率n2はフォトレジスト層の屈折率)である。

(もっと読む)

貫通孔配線基板の製造方法

【課題】めっき反応速度を調整することでめっき未着を防ぐことが可能な貫通孔配線基板の製造方法を提供することである。

【解決手段】微小デバイスを構成する貫通孔配線基板の製造方法であって、基板40の両表面を貫通する貫通孔41を形成する工程と、貫通孔41の少なくとも内表面にNiめっきを成長させる工程と、を備え、貫通孔41の少なくとも内表面にNiめっきを成長させる工程では、Niめっきの析出レートを50nm/min未満にしてめっきを成長させる。

(もっと読む)

61 - 80 / 276

[ Back to top ]