Fターム[4M104FF07]の内容

Fターム[4M104FF07]に分類される特許

121 - 140 / 276

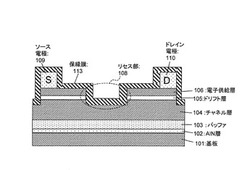

GaN系電界効果トランジスタの製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタの製造方法を提供する。

【解決手段】 GaN系電界効果トランジスタの製造方法は、基板101上にAlN層102、バッファ層103、チャネル層104、ドリフト層105および電子供給層106をエピタキシャル成長させる工程と、リセス部108を形成する工程と、アロイ工程におけるアニール時に電子供給層106を保護する保護膜113を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、オーミック接触を得るためのアニールを行なうアロイ工程と、保護膜113を除去し、ゲート絶縁膜を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、リセス部108のゲート絶縁膜上にゲート電極を形成する工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ高製造歩留まりで、BiCMOS型半導体集積回路装置を実現することができる半導体装置およびその製造方法を提供する。

【解決手段】シャロートレンチ3、ディープトレンチ6に囲まれた半導体層2の基板領域17に、p型の単結晶半導体からなるエピタキシャル・ベース層24が島状に形成される。当該島状領域を含む半導体層2上の全面に窒化シリコン膜42、酸化シリコン膜43が形成される。島状領域上の異なる位置の窒化シリコン膜42、酸化シリコン膜43には、少なくとも2つの開口部が形成され、開口部が形成された窒化シリコン膜42、酸化シリコン膜43上に半導体膜44が形成される。当該半導体膜44が選択的に除去され、一方の開口部において島状領域に接続するベース電極と、他方の開口部において島状領域に接続するエミッタ電極とが同時に形成される。

(もっと読む)

半導体装置

【課題】環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮する。

【解決手段】半導体装置1は、還流ダイオードDと、還流ダイオードDに対し並列に接続され、且つ、キャパシタCと抵抗Rを有する半導体スナバ2を備え、環流ダイオードDの遮断状態における静電容量に対するキャパシタCの静電容量の比が0.1以上になっている。このような構成によれば、振動現象の収束効果が高くなるように半導体スナバ2を構成するキャパシタCの静電容量が設定されているので、環流ダイオードDの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮することができる。

(もっと読む)

オーミック電極、半導体装置、オーミック電極の製造方法および半導体装置の製造方法

【課題】AlGaN層の裏面(N原子面)上に低抵抗なオーミック電極を形成することが可能なオーミック電極、半導体装置、オーミック電極の製造方法および半導体装置の製造方法を提供する。

【解決手段】オーミック電極16は、表面13aと、この表面13aと反対側の裏面12bとを有し、表面13aが(0001)面で、導電型がn型であるAlGaN層11の裏面12bに形成されたオーミック電極16において、オーミック電極16において裏面12bに接触している領域はWを含むことを特徴としている。オーミック電極16の製造方法は、裏面12bに接触する領域にWおよびMoの少なくとも一方を含むオーミック電極16を形成することを特徴としている。

(もっと読む)

電界効果トランジスタ

【課題】低いゲートリーク電流と低オン抵抗との同時に実現する。

【解決手段】InGaAsを主要な材料とするチャネル層と、AlGaAsを主要な材料とするショットキー層と、InGaPを主要な材料とするストッパ層と、ショットキー層の表面を露出するリセスを挟んで配置された第1領域と第2領域とを含むキャップ層と、キャップ層の上に設けられたソース/ドレイン電極と、リセスによって露出されたショットキー層の表面に設けられたゲート電極とを具備する電界効果トランジスタを構成する。ここで、キャップ層は、Si不純物を含む第1SiドープGaAsキャップ層と、第1SiドープGaAsキャップ層よりも低濃度のSi不純物を含む第2SiドープGaAsキャップ層と、第2SiドープGaAsキャップ層とストッパ層との間の層に設けられ、ポテンシャルバリアの上昇を抑制するバリア上昇抑制領域を備えるものとする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】導電層が基板の内部深くにまで達することを回避して、浅いソース・ドレイン領域を形成することを可能とし、微細化に適した半導体装置及びその製造方法を得る。

【解決手段】シリコン基板1の上面内にエクステンション5を形成した後、シリコン酸化膜30を全面に堆積し、シリコン酸化膜30上にシリコン窒化膜31を、シリコン窒化膜31上にシリコン酸化膜32をそれぞれ堆積し、シリコン酸化膜32、シリコン窒化膜31及びシリコン酸化膜30をこの順にエッチングしてサイドウォール36を形成する。不純物領域13を形成し、シリコン酸化膜に対して選択性を有する条件下でシリコン成長を行うことにより、シリコン成長層15,16,37を形成する。コバルト17を全面に堆積した後、熱処理を行うことにより、コバルトシリサイドを形成する。その後、未反応のコバルト17を除去する。

(もっと読む)

半導体装置の製造方法

【課題】加工精度を改善し、かつ厚い配線を得るための半導体装置の製造方法を提供することを課題とする。

【解決手段】絶縁性基板上に形成された導電性膜上に配線形成領域を覆う第1のフォトレジストパターンを形成する工程と、前記第1のフォトレジストパターンをマスクとする異方性エッチングにより前記導電性膜の上部を除去することで第1溝を形成する工程と、前記第1のフォトレジストパターンを除去した後、前記第1溝の底部の少なくとも一部が露出した開口を有する第2のフォトレジストパターンを形成する工程と、前記第2のフォトレジストパターンをマスクとする異方性エッチングにより前記第1溝の底部に露出する前記導電性膜の下部を少なくとも除去することで第2溝を形成する工程を備えることで、前記第1溝と第2溝に由来する配線分離溝と、前記配線分離溝により分離された配線とを形成することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置の性能の劣化を抑制することができる半導体装置を提供すること。

【解決手段】SiC基板11と、このSiC基板11上に形成されたAlGaN層13と、このAlGaN層13上にそれぞれ離間して形成されたソース電極15及びドレイン電極14と、これらのソース電極15、ドレイン電極14間に形成され、ソース電極15及びドレイン電極14に対して平行な開口部16を有する絶縁膜17と、この絶縁膜17の開口部16に形成されたゲート電極18と、このゲート電極18のドレイン電極14側にゲート電極18と一体形成され、ドレイン電極14側端部191が絶縁膜17と離間したドレイン側フィールドプレート電極19とを具備する半導体装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置の性能の劣化を抑制することができる半導体装置を提供すること。

【解決手段】SiC基板11と、このSiC基板11上に形成されたAlGaN層13と、このAlGaN層13上にそれぞれ離間して形成されたソース電極15及びドレイン電極14と、これらのソース電極15、ドレイン電極14間に形成され、ソース電極15及びドレイン電極14に対して平行な開口部16を有する第1の絶縁膜17と、この第1の絶縁膜17の開口部16に形成されたゲート電極18と、このゲート電極18が形成された第1の絶縁膜17上に形成された第2の絶縁膜19と、この第2の絶縁膜19及びソース電極15上に形成され、ドレイン電極14側の端部201が、第2の絶縁膜19と離間したソースフィールドプレート電極20と、を具備する半導体装置。

(もっと読む)

有機薄膜トランジスタ、有機薄膜トランジスタの製造方法、および電子機器

【課題】有機材料からなる下地の絶縁性層に対してダメージを与えることなく、かつ上部に設けられる有機半導体層に対して良好なオーミックコンタクトが得られるソース電極およびドレイン電極を低コストで得ることを可能にする。

【解決手段】有機絶縁層からなる基板11と、基板11上にめっき成膜された層からなるソース電極13sおよびドレイン電極13dの第1層13-1と、第1層13-1よりも有機半導体材料に対して低オーミック接合を形成する金属材料からなり第1層13-1を覆う状態でめっき成膜されたソース電極13sおよびドレイン電極13dの第2層13-2と、第1層13-1および第2層13-2で構成されたソース電極13sおよびドレイン電極13d間にわたって設けられた有機半導体層15とを備えた有機薄膜トランジスタ1aである。

(もっと読む)

半導体装置

【課題】 一対の主電極の間に設けられたゲート電極を有する半導体装置において、高い耐圧を確保しながらオン抵抗を低くする技術を提供する。

【解決手段】 半導体装置100は、一対の主電極2,22間に設けられたゲート電極10を備えている。ゲート部10は絶縁ゲート電極部10aとショットキー電極部10bを有している。半導体装置100は、主電極2に接続するコンタクト領域18と、コンタクト領域18に隣接するチャネル半導体領域8と、チャネル半導体領域8の裏面に接しているp型半導体領域20と、チャネル半導体領域8とp型半導体領域20の両者に隣接するドリフト半導体領域12を備えている。絶縁ゲート電極部10aは、ゲート絶縁膜4を介してコンタクト領域18の表面に対向している。ショットキー電極部10bは、ドリフト半導体領域12の表面に直接的に接触している。

(もっと読む)

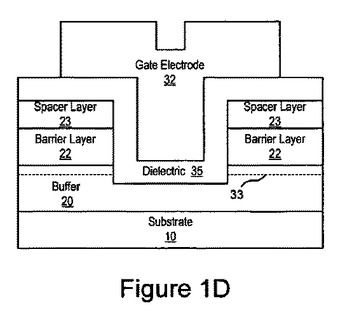

常時オフ半導体デバイスおよびその作製方法

常時オフ半導体デバイスが提供される。III族窒化物バッファ層が提供される。III族窒化物バリア層がIII族窒化物バッファ層上に設けられる。非伝導性スペーサ層がIII族窒化物バリア層上に設けられる。III族窒化物バリア層およびスペーサ層がエッチングされてトレンチを形成する。トレンチはバリア層を貫いて延びてバッファ層の一部を露出させる。誘電体層がスペーサ層上およびトレンチ内に形成され、ゲート電極が誘電体層上に形成される。半導体デバイスの形成に関連する方法も提供される。  (もっと読む)

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ゲートラストプロセスの適用に際して、トランジスタのフリンジ容量及びゲート抵抗の低減と、実効的なゲート長の短縮を実現する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板1上にゲート絶縁膜2、第1のダミーゲート部3及び第2のダミーゲート部4を順に積層して形成する工程と、それらをパターン加工するとともに、第1のダミーゲート部3をゲート長方向Xで第2のダミーゲート部4よりも後退させることにより、ノッチ部6を形成する工程と、ゲート絶縁膜2、第1のダミーゲート部3及び第2のダミーゲート部4の側方に絶縁材料からなる側壁7を形成し、かつ当該絶縁材料でノッチ部6を埋め込む工程と、第1,第2のダミーゲート部3,4を除去して、当該除去部分の底部にゲート絶縁膜2及びノッチ部6を残す工程と、除去部分を導電材料で埋め込むことによりゲート電極を形成する工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】短チャネル効果を抑制すると共に、MISトランジスタの駆動能力が劣化することを防止するMIS(Metal Inserted Semiconductor)トランジスタを備えた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10における活性領域10x上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、第1の導電膜14、及び該第1の導電膜14上に形成された第2の導電膜15からなるゲート電極15Aと、活性領域10xにおける第2導電膜15の側方下に形成されたエクステンション領域16と、第1の導電膜14上に、第2の導電膜15の側面と接して形成された第1のサイドウォール17とを備え、第1の導電膜14のゲート長方向の長さは、第2の導電膜15のゲート長方向の長さよりも大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】高周波応答特性を低下させずにリーク電流を低減させることができ、しかもゲート長の短縮化を図ることが可能な半導体装置を提供する。

【解決手段】電子供給層4にAlGaAs層4AとInGaP層4Bの積層構造を用い、半導体表面に形成する絶縁膜6にSiN膜6AとSiO2膜6Bの積層構造を用いる。絶縁膜6に電子供給層4を露出させる開口60を形成する際に、半導体と接触しているSiN膜6Aがサイドエッチングされることで、開口60の電子供給層4側の内周面61とゲート電極7との接触が回避され、しかもゲート電極7の周囲にInGaP層4Bのみを露出させることができる。

(もっと読む)

浅いイオン注入された領域を含む半導体デバイスとその形成方法

【課題】デバイスの窒化物エピタキシャル層にとって有害となる場合があるアニール条件に耐え得る半導体デバイスを形成する方法を提供すること。

【解決手段】半導体デバイスを形成する方法は、III族窒化物半導体層上に誘電体層を形成する工程と、前記半導体層において離間して設けられたソース領域およびドレイン領域上の前記誘電体層の一部を選択的に除去する工程と、第1の伝導度型を持つイオンを前記半導体層の前記ソース領域およびドレイン領域内へ直接イオン注入する工程と、前記注入されたイオンを活性化するために前記半導体層と前記誘電体層をアニールする工程と、および前記半導体層の前記ソース領域およびドレイン領域上に金属電極を形成する工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極の周囲に形成される空洞と保護膜に形成されるホールとの境界部分の開口を封止しやすい構造を実現する。

【解決手段】半導体装置を、ゲート電極3と、高さが低い部分6Aと高さが高い部分6Bとを有する階段状の空間6をゲート電極3の周囲に有する保護膜4と、高さが低い部分6Aに接するように保護膜4に形成されたホール5とを備えるものとする。

(もっと読む)

トランジスタ、半導体装置及びその製造方法

【課題】トレンチゲート型トランジスタのオン抵抗とプレーナ型トランジスタの耐圧とを同時に最適化する。

【解決手段】半導体基板10上に、半導体層16A、16Bがエピタキシャル成長により形成される。第1の領域において第1の埋め込み層12が形成され、第2の領域において第2の埋め込み層13が形成される。第1の埋め込み層12はN+型の第1の不純物層12Aと、それより広い範囲に拡散されたN型の第2の不純物層12Bとによって形成される。第2の埋め込み層13はN+型の不純物層のみで形成される。第1の領域において半導体層16Aの表面からN型の第3の不純物層18が深く拡散される。第1の領域にはトレンチゲート型トランジスタが形成され、第2の領域にはプレーナ型トランジスタが形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート酸化膜の信頼性を阻害せずに、ゲート電極の低抵抗化を実現可能な半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、炭化珪素からなり、表面にエピタキシャル結晶成長層2が形成された半導体基板1と、エピタキシャル結晶成長層2上部に選択的に形成されたウェル領域3とを備える。そして、ウェル領域3上部に選択的に形成されたソース領域4と、ソース領域4とエピタキシャル結晶成長層2とに挟まれたウェル領域3の表面を覆うゲート絶縁膜6上に形成されたゲート電極7とを備える。ゲート電極7は、珪素層7aと、炭化珪素層7bとの積層構造からなり、ゲート電極7上部に形成されたシリサイド層7cをさらに備える。

(もっと読む)

半導体装置及びその製造方法

【課題】高電圧動作時においても良好な特性を得ることができる半導体装置及びその製造方法を提供する。

【解決手段】半絶縁性のSiC基板1上に化合物半導体領域2が形成されている。i−GaN層2aの表層部分は電子走行層として機能し、その下の部分はバッファ層として機能する。バッファ層は、SiC基板1の表面に存在する格子欠陥の電子走行層への伝播を防止している。n−AlGaN層2cは電子供給層として機能する。n−GaN層2dには、n−AlGaN層2cを露出する2個の開口部が形成されており、開口部の各々に、オーミック電極がソース電極4又はドレイン電極5として形成されている。更に、n−GaN層2d、ソース電極4及びドレイン電極5を覆うシリコン窒化膜10が形成されている。シリコン窒化膜10には、1.4×1022個/cm3以上のSi−H結合基が含まれている。

(もっと読む)

121 - 140 / 276

[ Back to top ]