Fターム[4M104FF07]の内容

Fターム[4M104FF07]に分類される特許

81 - 100 / 276

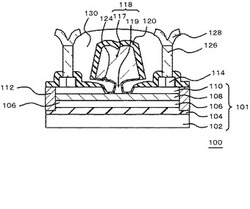

半導体装置およびその製造方法

【課題】ゲート電極の内部に腐食が進行することを抑制する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置100は、化合物半導体基板101と、化合物半導体基板101上の一部に形成された接続部119と接続部119上に形成されかつ接続部119より幅広の本体部117とを有しており、かつアルミニウムを含むゲート電極118と、ゲート電極118の表面上に設けられた保護絶縁層(シリコン窒化膜120)と、シリコン窒化膜120が被覆していないゲート電極118の表面に設けられており、アルミニウムよりも酸化されにくい不動態膜124と、を備える。

(もっと読む)

窒化物半導体装置

【課題】GaN系の窒化物半導体を用いたデバイスのゲートリセス量の制御性を向上することで、閾値電圧の面内均一性を向上することができる窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、基板101上に形成された第1のGaN系半導体からなるバッファ層102と、第2のGaN系半導体からなるキャリア走行層103と、第3のGaN系半導体からなるキャリア供給層104とを備えている。キャリア供給層104の上には第1の絶縁膜105と、アルミニウムを含む第2の絶縁膜106と、第1の絶縁膜105より膜厚が厚い第3の絶縁膜107とが形成されている。ソース電極108及びドレイン電極109は第1の絶縁膜105上に形成されている。ゲート電極110は、リセス構造を含む第2の絶縁膜106及び第3の絶縁膜107上に形成されている。

(もっと読む)

周期的な酸化およびエッチングのための装置と方法

半導体装置

【課題】Ti、PtおよびAuからなるゲート電極を有するリセス構造を有し、Ti上のPt若しくはAuが、素子領域表面のAlGaAs層に拡散することを抑制する半導体装置を提供する。

【解決手段】GaAs基板11上に形成された素子領域16と、第1のリセス領域25と、第2のリセス領域26と、第1のリセス領域25外の素子領域16上に、互いに離間して形成されたドレイン電極13およびソース電極14と、第2のリセス領域26の表面の一部に接し、第1のリセス領域25の表面の一部に接するゲート電極15を具備し、最下層が、第1のリセス領域25、および第2のリセス領域26の表面の一部に接するように、隙間を有して形成された第1のTi層29と、第1のTi層29上に、第1のTi層29の隙間を埋めるように形成されたAl層30と、Al層30上に形成されたPt層32と、Pt層上に形成されたAu層33と、を含むように構成する。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】最大発振周波数fmaxを高くしてダイヤモンド電界効果トランジスタの特性を大きく向上させ、かつ電圧降下を小さく抑えることにより実用レベルに到達させること。

【解決手段】「ソース・ゲート電極間隔dSG、ゲート・ドレイン電極間隔dGDを狭くすること」と「ソース電極の厚さtS、ドレイン電極の厚さtDを厚くすること」とを両立させるために、ソース電極およびドレイン電極を、エッチング溶液を用いてエッチングする層とレジストを用いてリフトオフする層とに分けて形成する。これにより電極の逆メサ部を小さくすることができるため、ソース電極とゲート電極との間隔を小さくして最大発振周波数fmaxを上げ、かつソース電極およびドレイン電極の厚みを厚くして電圧降下を小さく抑えることができる。

(もっと読む)

金属及びシリコンの交互層を含むコンタクト構造体並びに関連デバイスの形成方法

半導体デバイスを形成する方法であって、この方法は、半導体層を準備するステップと、半導体層上に第1の金属の第1の層を準備するステップとを含む。第1の金属の第1の層上に第2の層を準備することができる。第2の層は、シリコン層及び第2の金属の層を含むことができ、第1の金属及び第2の金属は異なり得る。第1の金属はチタンとすることができ、第2の金属はニッケルとすることができる。関連するデバイス、構造体、及び他の方法もまた説明される。 (もっと読む)

半導体装置

【課題】 占有面積の増加もなく、十分なESD保護機能を持たせたESD保護用のN型のMOSトランジスタを有する半導体装置を得ることを目的とする。

【解決手段】 絶縁膜が埋め込まれたトレンチ素子分離領域と、凹部に周囲をゲート絶縁膜で覆われたゲート電極が埋め込まれたトレンチチャネル領域と、絶縁膜が埋め込まれた凹部の周囲を濃いN型の拡散層で覆ったトレンチドレイン領域とが形成されており、ESD保護用のN型MOSトランジスタのチャネル領域には、トレンチチャネル領域が形成され、なおかつESD保護用のN型MOSトランジスタのドレイン領域には、トレンチドレイン領域が形成されている。

(もっと読む)

GaN系MOS型電界効果トランジスタ

【課題】ノーマリオフ動作を可能にし、かつしきい値電圧を自由に制御出来るGaN系MOSFETを提供する。

【解決手段】p−GaNからなる電子走行層13とゲート電極18との間にゲート絶縁膜15が形成されたGaN系MOSFET10である。ゲート電極18は、AlGaInP混晶からなる。ゲート電極18は、p型AlGaInP混晶からなる第1のゲート層19と、この上に形成されたp型GaAsからなる第2のゲート層20と、この上に形成された金属層(AuGe/Au電極)21とを有する。AlGaInP混晶の混晶比を変化させることにより、しきい値電圧を制御することが出来る。

(もっと読む)

III族窒化物系半導体素子およびIII族窒化物系半導体素子の製造方法

【課題】低コストで製造することができ、かつ、高い絶縁破壊耐圧を有するIII族窒化

物系半導体素子、およびIII族窒化物系半導体素子の製造方法を提供する。

【解決手段】シリコン層、絶縁層、および表面にシリコンからなる複数の核領域と前記複

数の核領域の間を埋める絶縁領域を有する複合層がこの順に形成された基板と、前記基板

上に形成されたIII族窒化物系半導体からなるバッファ層と、前記バッファ層上に形成

されたIII族窒化物半導体からなる動作層と、前記動作層上に形成された第1の電極お

よび第2の電極とを備え、前記核領域のそれぞれの最大幅L1が、前記第1の電極および

前記第2の電極の間の距離L2よりも小さいことを特徴とする。

(もっと読む)

ヘテロ接合電界効果型トランジスタ及びその製造方法

【課題】ゲートリーク電流を抑制する、窒化物半導体からなるリセスゲート構造のヘテロ接合FET及びその製造方法を提供することを目的とする。

【解決手段】本発明のヘテロ接合電界効果トランジスタは、窒化物半導体からなるヘテロ接合電界効果トランジスタであって、バリア層4とバリア層4の上に形成されたキャップ層5を含む半導体層と、半導体層に下部を埋没するようにして半導体層上に設けられたゲート電極9と、ゲート電極9の側面と半導体層の間に設けられた絶縁膜10と、を備え、ゲート電極9は、下面のみが半導体層と接触することを特徴とする。

(もっと読む)

半導体装置

【課題】GaN電子走行層、AlGaN電子供給層、およびGaNキャップ層が順次積層された半導体装置において、高周波数動作および高出力動作を実現することが可能な半導体装置を提供すること。

【解決手段】本発明は、基板10上に順次積層されたGaN電子走行層12、AlGaN電子供給層14、およびGaNキャップ層16と、GaNキャップ層16上に形成されたゲート電極18と、ゲート電極18の両側であって、AlGaN電子供給層14上に形成されたソース電極20およびドレイン電極22と、ゲート電極18とソース電極20との間のGaNキャップ層16に形成された第1の凹部30と、を具備し、第1の凹部30が有する底面32下におけるGaNキャップ層16の厚さは、ゲート電極18下におけるGaNキャップ層16の厚さに比べて薄い半導体装置である。

(もっと読む)

高温印刷部分と低温印刷部分の2つの部分を有する光起電力電池導体

半導体材料(1)上に少なくとも1つの導体を形成する方法は、(E1)−シルクスクリーン印刷によって第1の高温ペーストを堆積させるステップと、(E2)−前のステップの間に堆積された第1の高温ペーストに少なくとも部分的に重ねて、シルクスクリーン印刷によって、低温ペーストを堆積させるステップとを有する。 (もっと読む)

化合物半導体装置及びその製造方法

【課題】オン抵抗を大幅に低減し、十分な高電圧動作且つ高出力を得ることができる信頼性の高い化合物半導体装置を実現する。

【解決手段】ソース電極12及びドレイン電極13の下方の凹部7,8を充填し、電子供給層4の上方を覆う、Siを含むn−GaN層9が形成されており、n−GaN層9は、ソース電極12の下方及びドレイン電極13下方に含まれるSiの方が、ゲート電極15の近傍に含まれるSiよりも濃度が大きくなるように、Si添加量を漸減させながら成長形成される。

(もっと読む)

半導体装置の製造方法

【課題】RC型トランジスタのチャネル領域の高さを所望の範囲に調整するとともに、前記チャネル領域に近接して残存する薄皮状のバリ部を完全に除去して、半導体装置を製造するという課題があった。

【解決手段】半導体基板1の一面に、溝部と、溝部に囲まれ、側壁面の少なくとも一部が傾斜面である凸部39とを形成してから、溝部を埋める素子分離用絶縁膜を形成する第1工程と、素子分離用絶縁膜をマスクの一部にして半導体基板1の一面をドライエッチングして凸部39内に凹部27を設けるとともに、凹部27と素子分離用絶縁膜との間にチャネル領域4となる薄肉部41を形成する第2工程と、ウェットエッチングにより、薄肉部41の高さを調整する第3工程と、を有する半導体装置の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲートリセス構造を採用してノーマリーオフ動作を可能とするも、バラツキの小さい安定した閾値を有し、十分な高耐圧を実現する信頼性の高い化合物半導体装置を実現する。

【解決手段】電子走行層3と電子供給層4との間にi−AlNからなる中間層5を形成し、キャップ構造7上のゲート電極の形成予定部位に中間層5をエッチングストッパとして用いて開口11aを形成した後、中間層5の開口11aに位置整合する部位に熱リン酸を用いたウェットエッチングにより開口11bを形成して、開口11a,11bからなる開口11をゲート絶縁膜12を介して下部が埋め込み、上部がキャップ構造7上方に突出するゲート電極13を形成する。

(もっと読む)

ゲート電極の形成方法、AlGaN/GaN−HEMTの製造方法及びAlGaN/GaN−HEMT

【課題】リソグラフィ限界以下のゲート長を有するゲート電極の形成方法、及び高周波特性のよいAlGaN/GaN-HEMTの製造方法及びAlGaN/GaN-HEMTを提供する。

【解決手段】基板1表面に第1SiN表面保護層2を成膜する工程と、第1SiN表面保護層表面のレジスト3にリソグラフィ限界のレジスト開口部3aを形成し第1SiN表面保護層をエッチング開口する工程と、第1SiN表面保護層の開口部2a及び第1SiN表面保護層の表面に第2SiN表面保護層4を成膜する工程と、第2SiN表面保護層の表面のレジスト5にリソグラフィ限界のレジスト開口部5aを形成し異方性RIEにて第2SiN表面保護層をエッチングして第2SiN表面保護層の開口部4aと第2SiN表面保護層のサイドウォール4bとを形成する工程と、サイドウォールの内側の基板表面とサイドウォールと第2SiN表面保護層の開口部とを被覆するゲート電極6を形成する工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極のテーパ形状の傾斜度を緩やかにすることができるようにして、ゲート電極の破損が起こらないようにしながら、確実にさらなる微細化を実現した下部電極を形成できるようにする。

【解決手段】ソース電極2及びドレイン電極3を有する半導体領域1上に絶縁膜4を形成し、絶縁膜4上に複数のレジスト層5,6,7を含む積層レジスト8を形成し、積層レジスト8の最下層以外のレジスト層6,7に開口9を形成し、最下層のレジスト層5にリフロー用開口10を形成し、熱処理を施してリフロー用開口10に露出している最下層のレジスト層5の一部PTcをリフローさせ、リフローさせることによって最下層のレジスト層5の表面に形成された傾斜面11に連なるように最下層のレジスト層5に第1ゲート下部開口12Aを形成し、開口9、傾斜面11及び第1ゲート下部開口12Aの形状に応じた形状を持つゲート電極13を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】応答特性を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、GaN層10と第1および第2の絶縁層13、14と電極層とFP電極17とを備える。GaN層10は、高欠陥領域10aと、高欠陥領域10aよりも欠陥密度の低い低欠陥領域10bとを含み、主表面10cを有する。第1の絶縁層13は、GaN層10の主表面10cにおける高欠陥領域10aを覆うように形成される。第2の絶縁層14は、GaN層10の主表面10aにおける低欠陥領域10bの上に形成され、開口部が形成される。電極層は、開口部の内部に、GaN層10の主表面10aに接触するように形成される。FP電極17は、電極層に接続するとともに、第2の絶縁層14に重なるように形成される。第1の絶縁層13は、第2の絶縁層14を構成する材料の誘電率よりも小さい誘電率を有する材料を含む。

(もっと読む)

多結晶シリコン・ゲート上のサリサイドの抵抗を改善するための方法およびデバイス

【課題】幅の狭いポリサイドゲートにおけるシリサイドの抵抗が改善されたゲート電極構造の製造方法を提供する。

【解決手段】リセスが形成されたシリコン酸化膜からなる厚い内部スペーサ、およびシリコン窒化膜からなる厚い外部スペーサを有する多結晶シリコンゲートを形成する。多結晶シリコン上にチタンをデポジションし、アニールによりチタンシリサイド層260を形成する。チタンシリサイド層は多結晶シリコンより幅広く形成され、シリコン酸化膜からなる厚い内部スペーサによって制約を受けず、応力を受けない。

(もっと読む)

フィールドプレートを有する半導体デバイス

III−N材料層と、III−N材料層の表面上に設けられた絶縁体層と、III−N材料層から反対側の絶縁体層上記に設けられたエッチング停止層と、絶縁体層から反対側のエッチング停止層上に設けられた電極画定層とを備えるIII−Nデバイスを開示する。電極画定層内には、凹部が形成される。凹部内には、電極が形成される。絶縁体は、特に電極とIII−N材料層との間で、正確に制御された厚さを有することができる。 (もっと読む)

81 - 100 / 276

[ Back to top ]