Fターム[4M104FF11]の内容

Fターム[4M104FF11]に分類される特許

1 - 20 / 514

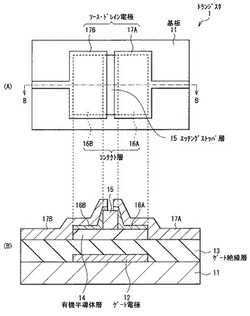

トランジスタ、トランジスタの製造方法、表示装置および電子機器

【課題】歩留り良く製造可能なトランジスタ、トランジスタの製造方法、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層上のエッチングストッパ層と、前記半導体層上の、少なくとも前記エッチングストッパ層の両側に設けられた一対のコンタクト層と、前記半導体層に前記一対のコンタクト層を介して電気的に接続されると共に前記絶縁層に接するソース・ドレイン電極と、を備えたトランジスタ。

(もっと読む)

窒化物半導体ダイオード

【課題】高耐圧、低逆方向リーク電流特性を有する二次元電子ガスを導電層とした性能の高い窒化物半導体ダイオードを提供する。

【解決手段】窒化物半導体積層膜の上面に塩素ガスを用いたドライエッチングにより形成した凹部6の底面および側面部に対して、所望の不純物を拡散させる、または所望の不純物を添加した窒化物半導体を再成長することにより、アノード電極7が接触する窒化物半導体積層膜の側面部を高抵抗化させ、逆方向リーク電流を低減する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化されたトランジスタのオン特性を向上させる。微細化されたトランジスタを歩留まりよく作製する。

【解決手段】一対の低抵抗領域及び該低抵抗領域に挟まれるチャネル形成領域を含む酸化物半導体層と、ゲート絶縁層を介してチャネル形成領域と重畳する第1のゲート電極層と、第1のゲート電極層のチャネル長方向の側面及びゲート絶縁層の上面と接し、一対の低抵抗領域と重畳する一対の第2のゲート電極層と、第2のゲート電極層上の、側端部を第2のゲート電極層の側端部と重畳する一対の側壁絶縁層と、を有する半導体装置を提供する。

(もっと読む)

トレンチ型ショットキー接合型半導体装置及びその製造方法

【課題】 耐圧を低下させることなく、トレンチ開口幅を小さくすることができるショットキー接合型半導体装置を提供する。

【解決手段】 トレンチの断面形状を、トレンチの底面部の中央が高く、周辺が低いサブトレンチ形状とし、p型不純物をドリフト層表面に対して垂直に導入することで、サブトレンチが設けられたトレンチの内壁部に接するように形成されたp+SiC領域が、トレンチの底面の中央での接合位置よりも、トレンチの底面の周辺での接合位置が深くなるように形成する。

(もっと読む)

エアギャップを備えるグラフェントランジスタ、それを備えるハイブリッドトランジスタ及びその製造方法

【課題】エアギャップを備えるグラフェントランジスタ、それを備えるハイブリッドトランジスタ及びその製造方法を提供する。

【解決手段】基板上のゲート電極と、ゲート電極上のゲート絶縁層と、ゲート絶縁層上のグラフェンチャネルと、グラフェンチャネル上で互いに離隔しているソース電極及びドレイン電極と、ソース電極及びドレイン電極の上面を覆い、グラフェンチャネル上でソース電極とドレイン電極との間にエアギャップを形成するカバーと、を備えるグラフェントランジスタ。前記ソース電極と前記ドレイン電極との間の前記グラフェンチャネルの長さが、10nm〜100nmである。

(もっと読む)

窒化物半導体装置

【課題】櫛型形状のソース電極とドレイン電極が交差指状に配置された電極構造を有し、各櫛形電極の先端部での電界集中が緩和された窒化物半導体装置を提供する。

【解決手段】ゲート電極5と電気的に接続され、ゲート電極5とドレイン電極4間で絶縁膜7上に配置されたゲートフィールドプレート50と、ソース電極3と電気的に接続され、絶縁膜8を介して窒化物半導体層と対向するようにゲートフィールドプレート50とドレイン電極4間の上方に配置されたソースフィールドプレート30とを備え、ゲート電極5とドレイン電極4間の距離、ゲートフィールドプレート50のドレイン側端部とゲート電極5のドレイン側端部間の距離、及びソースフィールドプレート30のドレイン側端部とゲートフィールドプレート50のドレイン側端部間の距離の少なくともいずれかが、ソース電極3とドレイン電極4の、歯部分の直線領域よりも歯部分の先端領域において長い。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層の溝に埋め込まれた電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設ける。チャネル形成領域は、サイドウォールを側壁に有するゲート電極層と重なる位置に形成される。溝は、深い領域と浅い領域を有し、サイドウォールは、浅い領域と重なり、配線との接続は、深い領域と重なる。

(もっと読む)

半導体装置、モジュール、及び電子機器

【課題】大量生産上、大型の基板に適している液滴吐出法を用いた製造プロセスを提供す

る。

【解決手段】液滴吐出法で感光性の導電膜材料液を選択的に吐出し、レーザ光で選択的に

露光した後、現像またはエッチングすることによって、レーザ光で露光した領域のみを残

し、吐出後のパターンよりも微細なソース配線およびドレイン配線を実現する。TFTの

ソース配線およびドレイン配線は、島状の半導体層を横断して重ねることを特徴としてい

る。

(もっと読む)

半導体装置

【課題】低コンタクト抵抗を実現し得る半導体基板上の半導体層と電極配線層とのオーミック電極構造を提供する。

【解決手段】半導体基板106と、半導体基板106上に形成された第1のバリア層107と、第1のバリア層107上に形成された厚さ1nm以上40nm以下のチャネル層108と、チャネル層108の上に形成された第2のバリア層102と、少なくとも第2のバリア層102及びチャネル層108を厚さ方向に貫通する第1の電極領域109と、少なくとも第2のバリア層102及びチャネル層108を厚さ方向に貫通する第2の電極領域109とを備える半導体装置であって、少なくとも第1の電極領域109は、チャネル層108と接触する側の面が凹凸形状で構成されている。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】酸化物半導体層、第1の導電層及び第2の導電層の積層によって構成されるソース電極層又はドレイン電極層、ゲート絶縁層、及びゲート電極層が順に積層されたコプレナー型のトランジスタにおいて、該ゲート電極層は、該第1の導電層と該ゲート絶縁層を介して重畳し、該第2の導電層と前記ゲート絶縁層を介して非重畳とする。

(もっと読む)

光透過型金属電極、電子装置及び光学素子

【課題】シート抵抗が低く、広い波長範囲で高い透過率を有する光透過型金属電極、電子装置及び光学素子を提供する。

【解決手段】実施形態によれば、複数の第1金属線と、複数の第2金属線と、を含む光透過型金属電極が提供される。複数の第1金属線は、第1方向に沿って並ぶ。第1金属線は、第1方向と交差する第2方向に沿って延びる。複数の第2金属線は、第1方向と第2方向を含む平面に対して平行で第1方向と交差する第3方向に沿って並び、第1金属線と接触する。第2金属線は、その平面に対して平行で第3方向と交差する第4方向に沿って延びる。複数の第1金属線の第1方向における中心どうしの第1距離は、可視光を含む波長帯の最短の波長以下である。複数の第2金属線の第3方向における中心どうしの第2距離は、波長帯の最長の波長を超える。第1金属線と第2金属線の厚さは、最短の波長以下である。

(もっと読む)

窒化物半導体素子及び製造方法

【課題】耐圧が高く、かつ、リーク電流が効果的に低減された窒化物半導体素子及びその製造方法を提供する。

【解決手段】ベース基板210と、ベース基板の上方に形成されたバッファ層280と、バッファ層280上に形成された活性層290と、活性層の上方に形成された少なくとも2つの電極292および294とを備え、バッファ層280は格子定数の異なる複数の窒化物半導体層を含む複合層を1層以上有し、複合層の少なくとも1層は、複数の窒化物半導体層のうち格子定数が最も大きい窒化物半導体層のキャリア領域に予め定められた濃度の炭素原子及び予め定められた濃度の酸素原子が意図的にドープされている窒化物半導体素子。

(もっと読む)

光透過型金属電極、電子装置及び光学素子

【課題】低い電気抵抗を維持しながら、広い波長範囲で十分な透明性を得ることができる金属電極、半導体発光素子及び光学素子を提供する。

【解決手段】実施形態に係る金属電極は、部材の主面上に設けられ、金属細線と、前記金属細線により形成される複数の開口部と、を有する金属層である。金属細線は、前記主面に対して平行な第1方向に沿う複数の第1直線部と、前記主面に対して平行で前記第1方向と交差する前記第1方向とは異なる方向に沿う複数の直線部と、を有する。前記複数の第1直線部の前記第1方向に沿う長さの最大値及び前記複数の第2直線部の前記第1方向とは異なる方向に沿う長さの最大値は、可視光の波長以下である。前記主面の法線方向にみた前記金属層の面積に対する前記法線方向にみた前記金属細線の面積の比は、20パーセントを超え80パーセント以下である。

(もっと読む)

窒化物系発光素子及びその製造方法

【課題】窒化物系発光素子及びその製造方法を提供する。

【解決手段】窒素物系発光素子は、基板110、n型クラッド層130、活性層140、

p型クラッド層150、格子セル層160及びオーミック接触層が順次に積層された構造

よりなっている。また格子セル層160は導電性を有する素材で30μm以下の大きさを

有する粒子型セルがオーミック接触層内に埋め込まれて、相互離隔されて形成されている

発光素子である。このような窒素物系発光素子とその製造方法は、p型クラッド層とのオ

ーミック接触特性が改善されているため発光効率及び素子寿命を向上させ、かつウェーハ

成長後の活性化工程を省略できて、製造工程を単純化させうる。

(もっと読む)

半導体発光装置及びその製造方法

【課題】高いオーミック性と反射率を併せ有する電極構造を備える、低駆動電圧で駆動し、良好な光取り出し効率を有する半導体発光装置及びその製造方法を提供すること。

【解決手段】n型半導体層と、p型半導体層と、前記n型半導体層と前記p型半導体層との間に設けられた活性層と、前記n型半導体層に接して設けられたn電極と、前記p型半導体層に接して設けられたp電極とを具備する半導体発光素子。前記p電極が前記p型半導体層上に少なくとも一部が網目状に形成されたNiO層と、このNiO層に接して形成されたAg層とを含む。

(もっと読む)

パワー絶縁ゲート型電界効果トランジスタ

【課題】酸化物半導体を用いたパワー絶縁ゲート型電界効果トランジスタ(パワーMISFET)を提供する。

【解決手段】半導体層103を挟んでゲート電極105とドレイン電極102を形成し、ゲート電極105の側面に半導体層109を形成し、ゲート電極105の頂上部と重なる部分で、半導体層109とソース電極112が接する構造を有する。このようなパワーMISFETのドレイン電極とソース電極の間に500V以上の電源と負荷を直列に接続し、ゲート電極105に制御用の信号を入力して使用する。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

電界効果トランジスタ

【課題】ゲート電極とソース電極との間に印加される電圧がソース電極パッドの電気抵抗による電圧降下で低下することを防止でき、安定した動作を実現できる電界効果トランジスタを提供する。

【解決手段】このGaN HFETによれば、ボンディング部16Bの第2のパッド部16B‐2は、電極接続部16Aが含有する複数の接続部分19のうちの第2の方向(ソース電極12とドレイン電極11が対向している方向)の一端に配置された接続部分19の上記第2の方向の外端を電極延在方向へ延長した仮想延長線L1に関して第1のパッド部16B‐1とは反対側に位置している。第2のパッド部16B‐2に接続された第2のソース配線24のボンディング箇所の第2の方向の位置を電極接続部16Aのソース電極12との接続部分19の第2の方向の位置と重ならないようにして、ソース電極12からの電流が第2のソース配線24に流れにくくできる。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、製造コストを低減し、さらにゲート電極およびゲートコンタクトの抵抗を低減した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、ゲート電極7の少なくとも上層は、第2金属シリサイド膜としてのWSix膜72からなり、第1金属シリサイド膜としてのNiSi2膜18に含まれる第1金属(Ni)とシリコンとの結合エネルギーが、WSix膜72に含まれる第2金属(W)とのシリコンとの結合エネルギーよりも小さく、WSix膜72の組成MSix(Mは第2金属を示す)において、xが1.5以上2.0未満であることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】本願発明者らが、プラズマ処理等による半導体ウエハのチャージアップの影響を検討したところによると、半導体ウエハ等にドライエッチング等を施すと、通常、その結果として、半導体ウエハは、主に電気的に正側に偏った不均一な帯電状態となることが明らかとなった。これは、ドライエッチング等によって、正の可動イオン等がウエハの表面やその近傍に残存し、不均一に分布していることを示すものであり、個々の半導体チップとされた後も残存して、動作に悪影響を及ぼす恐れがある。

【解決手段】本願発明は、通常、ポリマー除去液等を使用する必要のないメタル膜加工工程に於いて、加工用レジスト膜の除去後、ポリマー除去液類似の導電性処理液との摩擦により、ウエハ全体を負に帯電させるものである。

(もっと読む)

1 - 20 / 514

[ Back to top ]