Fターム[4M104FF16]の内容

Fターム[4M104FF16]の下位に属するFターム

Fターム[4M104FF16]に分類される特許

61 - 80 / 149

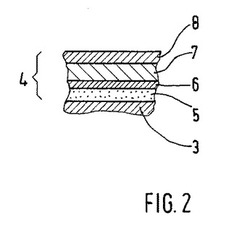

光起電モジュールおよびその製造方法

【課題】銀の反射層に高い反射率を達成する付着向上層を設けた光起電力モジュールおよびその製造方法を提供する。

【解決手段】光起電モジュールが、透明な基板上に、透明な前側電極層、半導体層3、および後ろ側電極層4を有している。後ろ側電極層4が、銀の層7と、ドープされた半導体で構成されて銀の層7と半導体層3との間に位置する中間層5とを有している。銅の層6が、銀の層7と中間層5との間に設けられている。好ましくは、前記銀の層7の層の厚さが、50〜500nm、前記銅の層6の層の厚さが、1〜50nm、前記中間層5の層の厚さが、10〜300nmである。

(もっと読む)

半導体装置

【課題】曲げ等の外力が加わり応力が生じた場合であってもトランジスタ等の損傷を低減する半導体装置を提供することを目的とする。

【解決手段】可撓性を有する基板上に設けられた第1の島状の補強膜と、第1の島状の補強膜上に、チャネル形成領域と不純物領域とを具備する半導体膜と、チャネル形成領域の上方にゲート絶縁膜を介して設けられた第1の導電膜と、第1の導電膜及びゲート絶縁膜を覆って設けられた第2の島状の補強膜とを有している。

(もっと読む)

半導体装置、電気光学装置、及び電子機器

【課題】構造を複雑化させることなく安定した特性が得られ、さらには抵抗素子を含む回路の高集積化を実現できる半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、基板本体(基板)10Aと、基板本体10A上に形成された半導体素子(インバータINV1,INV2)と、半導体素子に接続された配線121,122と、配線121,122に形成された抵抗素子R1,R2とを備えており、配線121,122が、積層された複数の導電層131,132を有しており、異なる抵抗値を有する複数の抵抗素子R1,R2が、複数の導電層のうち少なくとも一部の導電層を用いて配線121,122に形成されていることを特徴とする。

(もっと読む)

薄膜トランジスター

【課題】薄膜トランジスターを提供する。

【解決手段】ガラス基板1の上にゲート電極膜2を形成し、前記ガラス基板1およびゲート電極膜2の上に窒化珪素膜3を形成し、前記窒化珪素膜3の上にアモルファスSi膜4を形成し、前記アモルファスSi膜4の上に燐ドープアモルファスSi膜4´を形成し、前記燐ドープアモルファスSi膜4´の上にバリア膜を形成し、前記バリア膜の上に純銅または銅合金膜8からなるドレイン電極膜5およびソース電極膜6を形成し、前記ドレイン電極膜5およびソース電極膜6の上に窒化珪素膜3´を被覆形成してなる薄膜トランジスターにおいて、前記バリア膜は、Si、燐、Cuおよび酸素からなり、必要に応じてその他の元素を含有するCu燐ドープ酸化ケイ素膜12´で構成されていることを特徴とする。

(もっと読む)

集積回路チップ上の電気めっき相互接続構造

【解決課題】集積回路用のサブミクロン相互接続構造を製作する方法を提供する。

【解決手段】添加剤を含み、平坦で光沢があり延性があり低応力のCu金属を付着させるのに通常用いられる浴からCuを電気めっきすることによって、ボイドのないシームレスな導体が得られる。ボイドまたはシームを残すことなくフィーチャを超充填できるこの方法の能力は独特であり、他の付着方法より優れている。この方法で電気めっきされたCuを利用する構造のエレクトロマイグレーションの抵抗は、AlCu構造または電気めっき以外の方法で付着されたCuを用いて製作された構造のエレクトロマイグレーションの抵抗より優れている。

(もっと読む)

半導体装置

【課題】 ゲート電極上のシリサイド膜の断線を抑制する。

【解決手段】 ソース・ドレイン領域をデュアルシリサイド構造とし、ゲート電極の仕事関数はn型MISトランジスタ、p型MISトランジスタそれぞれの有するメタルゲート電極により定める構造とし、且つ、メタルゲート電極上の多結晶シリコン層は共通のn+ドーピング層とし、ゲート上シリサイド膜はn型領域に対しショットキー障壁が低くなる材料で形成する。

(もっと読む)

薄膜トランジスター

【課題】薄膜トランジスターを提供する。

【解決手段】ガラス基板1の上にゲート電極膜2を形成し、前記ガラス基板1およびゲート電極膜2の上に窒化珪素膜3を形成し、前記窒化珪素膜3の上にアモルファスSi膜4を形成し、前記アモルファスSi膜4の上にバリア膜を介して純銅からなるドレイン電極膜5およびソース電極膜6を形成し、前記アモルファスSi膜4、ドレイン電極膜5およびソース電極膜6の上に窒化珪素膜3´を被覆形成してなる薄膜トランジスターにおいて、前記バリア膜は、炭化ケイ素膜12で構成されており、微量炭素含有銅膜15は有ることが好ましいが無くてもよい。

(もっと読む)

ショットキーダイオードを備える相変化メモリ素子

【課題】相変化メモリ素子を提供する。

【解決手段】基板上に一方向に延伸しているワードラインと、ワードライン上に位置する第1半導体パターンと、第1半導体パターン上に位置するノード電極と、第1半導体パターンとノード電極との間に形成されたショットキーダイオードと、ノード電極上に位置する相変化抵抗体と、を備える半導体メモリ素子。

(もっと読む)

半導体装置

【課題】それぞれが適した閾値を有するフィン型MOSFETとプレーナ型MOSFETが混載され、且つ少ない工程で製造することができる半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、第1のゲート電極と、前記第1のゲート電極にフェルミレベルピニングを発生させない第1のゲート絶縁膜と、を有するプレーナ型MOSFETと、第2のゲート電極と、前記第2のゲート電極にフェルミレベルピニングを発生させる第2のゲート絶縁膜と、を有するフィン型MOSFETと、を有する。

(もっと読む)

半導体装置の製造方法

【課題】バリアメタルが薄い場合でもAl配線のモフォロジ及びエレクトロマイグレーションを改善することができる半導体装置の製造方法を得る。

【解決手段】まず、半導体基板11上にSiO2層間膜13(酸化膜)を形成する。次に、SiO2層間膜13上にTi膜18を形成する。次に、Ti膜18上にTiN膜32を形成する。次に、TiN膜32上にAl配線33を形成する。ここで、Ti膜18を形成する工程において、圧力が0.3Pa以下の雰囲気中で物理気相成長法を用いる。これにより、Ti膜18とSiO2層間膜13との間にTiO2膜31が形成される。

(もっと読む)

半導体装置の製造方法

【課題】 半導体ウェハ外周部近傍にめっき膜を形成せず、かつ、パーティクルやシール不良などの不具合の発生を防止することができる半導体装置の製造方法を実現する。

【解決手段】 SOI基板10の素子形成基板10aの表面に、フォトレジストにより、素子形成領域10fを囲む遮断部材13を突出形成する。これにより、めっき液Lの素子形成基板10aの面方向への移動を遮断し、遮断部材13に囲まれた領域にのみめっき液Lを接触させて電気めっきを行うことができるため、素子形成領域10fにのみCuめっき膜Mを形成することができる。遮断部材13は、素子形成基板10a上に形成されているため、めっき装置20からSOI基板10を取り外すときに、遮断部材13に付着したCuめっき膜Mがめっき槽21に落下するおそれがない。

(もっと読む)

金属膜の成膜方法、多層配線構造の形成方法、半導体装置の製造方法、成膜装置

【課題】金属膜を吸着および分解プロセスの繰り返しにより、効率よく成膜する。

【解決手段】成膜方法は、被処理基板表面に金属元素のカルボニル原料を気相分子の形で、前記気相分子の分解を抑制する気相成分と共に、前記気相成分の分圧を、前記カルボニル気相原料分子の分解が抑制される第1の分圧に設定して供給する第1の工程と、前記被処理基板表面において前記気相成分の分圧を、前記カルボニル原料の分解が生じる第2の分圧に変化させ、前記被処理基板表面に前記金属元素を堆積させる第2の工程と、よりなることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化が進みゲート長のバリエーションが増大した場合にも、高駆動力MISFETを搭載した高性能デバイスを安定して実現できる簡便なFUSI化技術を提供する。

【解決手段】第1のゲート長(相対的に短いゲート長)を持つ第1のゲート電極105Aがフルシリサイド化されているのに対して、第2のゲート長(相対的に長いゲート長)を持つ第2のゲート電極105Bはフルシリサイド化されていない。

(もっと読む)

絶縁ゲート電界効果トランジスタ及びその製造方法

【課題】ゲート電極の上方にコンタクトプラグを形成するときに、ゲート絶縁膜やゲート電極を構成する材料がエッチングされることが無く、高い信頼性を有するゲート電極を有する絶縁ゲート電界効果トランジスタを提供する。

【解決手段】絶縁ゲート電界効果トランジスタは、ソース/ドレイン領域13及びチャネル形成領域12、ゲート電極23、並びに、ゲート絶縁膜30を備えており、ゲート絶縁膜30は、ゲート電極23とチャネル形成領域12との間に形成されたゲート絶縁膜本体部30A、及び、ゲート絶縁膜本体部30Aからゲート電極23の側面部23Aの途中まで延在するゲート絶縁膜延在部30Bから構成されており、チャネル形成領域12の表面を基準としたゲート電極23の高さをHGate、ゲート絶縁膜延在部30Aの高さをHInsとしたとき、HIns<HGateを満足する。

(もっと読む)

窒化物半導体素子の製造方法

【課題】p型のIII族窒化物半導体層(チャネル層)に対してコンタクト電極を良好にオーミック接触させることができる窒化物半導体素子の製造方法を提供すること。

【解決手段】III族窒化物半導体からなる電界効果トランジスタの製造工程において、まず、基板12の上にn型GaN層2およびp型GaN層3が形成される。次いで、このp型GaN層3の上に、コンタクト電極15が形成される。コンタクト電極15が形成された後には、p型GaN層3からコンタクト電極15上に至る領域にn型GaN層4が形成され、このn型GaN層4の表面からコンタクト電極15に至るコンタクトホール14が形成される。そして、このコンタクトホール14にソース電極11が埋め込まれる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体層の上の領域を有効利用することができる、半導体装置およびその製造方法を提供する。

【解決手段】半導体装置100は、半導体基板120と、半導体基板120の上に設けられた絶縁層130と、絶縁層130の上に設けられたSOI層140とからなるSOI基板110を含む。半導体基板120において、不純物拡散層122が設けられている。不純物拡散層122は、SOI層140の上に設けられた配線層162と電気的に接続されている。不純物拡散層122は、配線層または抵抗層として機能させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】選択ゲートトランジスタのゲート電極間のビット線コンタクトのコンタクトホール形成を確実にできるようにする。

【解決手段】シリコン基板1にメモリセルトランジスタおよび選択ゲートトランジスタのゲート電極MG、SGが形成されたもので、選択ゲートSG−SG間の構成として、ゲート電極SGの対向する側壁にシリコン窒化膜12の厚いスペーサを設ける。シリコン窒化膜12はシリコン基板1に対してシリコン酸化膜11を介した状態で形成される。ゲート電極MG、SGの上部にはコバルトシリサイドの金属シリサイド層8が形成される。ビット線コンタクトのコンタクトホール16は、シリコン窒化膜13、12の部分で自己整合的に制約を受けて狭くなり、確実にコンタクトプラグ17を形成できる。

(もっと読む)

電気銅めっき方法及び硫酸銅めっき液

【課題】結晶粒径を小さくしてストレスマイグレーションを抑制した銅めっき膜を、より簡便に基板上に成膜できるようにする。

【解決手段】シード層で覆われた配線用凹部を表面に形成した基板を用意し、シード層を、硫酸銅及び硫酸由来の硫黄を2.0M以上含む硫酸銅めっき液に接触させ、シード層をカソードとして、該カソードと硫酸銅めっき液中に浸漬させたアノードとの間に電圧を印加して、シード層の表面に銅めっき膜を成膜する。

(もっと読む)

パターン形成方法及び薄膜トランジスタの作製方法

【課題】フォトレジストの回数を削減し、且つ微細な薄膜加工を容易に行う方法を提供することを課題とする。

【解決手段】基板上に形成された第1の層及び光吸収性を有する第2の層上に選択的にレーザービーム照射を行い、光吸収層の一部を除去し、光吸収層をマスクとして第1の層の露出させた部分をエッチングにより除去する。次に少なくとも第1の層及び第2の層の除去された部分を覆うように第2の層上の一部にマスクとなる層を液滴吐出法により形成し、マスクとなる層をマスクとして第1の層及び第2の層をエッチングする。所定の場所に適した方法を選択して薄膜加工を行うことができるため、スループットが向上する。

(もっと読む)

電子的構成部材

本発明は、半導体材料からなる基板(3)上に金属層(9)を有する電子的構成部材に関し、この場合金属層(9)と基板(3)との間には、拡散遮断層(7)が形成されており、この拡散遮断層は、金属層(9)の金属に対して小さな拡散係数を有する材料から完成されている。  (もっと読む)

(もっと読む)

61 - 80 / 149

[ Back to top ]