Fターム[4M104FF16]の内容

Fターム[4M104FF16]の下位に属するFターム

Fターム[4M104FF16]に分類される特許

21 - 40 / 149

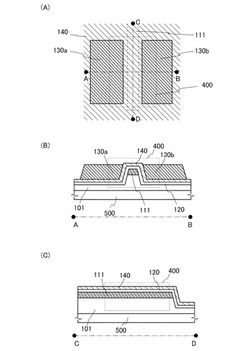

半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを用いて、高速動作が可能で、信頼性も高い半導体装置を歩留まりよく作製する。

【解決手段】絶縁膜上にマスクを形成し、該マスクを微細化する。微細化されたマスクを用いて凸部を有する絶縁層を形成し、これを用いて、微細なチャネル長(L)を有するトランジスタを形成する。また、トランジスタを作製する際に、微細化された凸部の上面と重なるゲート絶縁膜の表面に平坦化処理を行う。これにより、トランジスタの高速化を達成しつつ、信頼性を向上させることが可能となる。また、絶縁膜を凸部を有する形状とすることで、自己整合的にソース電極及びドレイン電極を形成することができ、製造工程の簡略化、また生産性を向上させることが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体集積回路の高集積化と機能素子の高性能化とを同時に実現する。

【解決手段】実施形態に係わる半導体装置は、半導体基板1の表面領域に配置されるスイッチ素子3,4と、下面がスイッチ素子3,4に接続されるコンタクトプラグ6と、コンタクトプラグ6の上面の直上に配置される機能素子7とを備える。コンタクトプラグ6の上面の最大表面粗さは、0.2nm以下である。

(もっと読む)

薄膜トランジスタとその製造方法、及びアクティブマトリックス基板

【課題】電極/配線の材料としてAl及び/又はその合金が用いられており、オフリーク電流が小さく良好な素子特性を有する薄膜トランジスタ(TFT)を提供する。

【解決手段】TFT101は、基板1上にゲート電極2とゲート絶縁膜3とチャネル層として機能する半導体膜4とを備え、半導体膜4上にソース電極6とドレイン電極7とが互いに離間して設けられたものであり、ソース電極6及びドレイン電極7は、アルミニウム及び/又はその合金を主成分とする少なくとも1層のアルミニウム(合金)膜を含む単層膜又は積層膜からなり、半導体膜4の表面のソース電極6及びドレイン電極7の間の領域8に、電気的に不活性な少なくとも1種のアルミニウム化合物9が形成されたものである。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】バリアメタル層を有する半導体装置を製造するに際し、パーティクルの発生を抑制可能な製造方法、及びこの製造方法を用いる半導体装置の製造装置を提供する。

【解決手段】

2つの金属層の間に金属化合物層が挟まれてなるバリアメタル層を有する半導体装置を製造するに際し、チタン及びタンタルのいずれか一方の金属元素から構成されるターゲットを希ガスの雰囲気でスパッタして、複数の金属層を下地配線上に積層する過程において最下層となる第1金属層に酸化処理を施す。次いで、最下層となる第1金属層の表面に第1金属酸化物層を形成した後に、層間において構成元素が異なるように、一つ以上の金属層を含む下地の表面に対して酸化処理、窒化処理、及び酸窒化処理のいずれかの処理を施す。こうした処理より第2金属化合物層を形成する。上記金属化合物層は、金属酸化物層の他、金属窒化物層や金属酸窒化物層であってもよい。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu系合金配線膜と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに密着性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記半導体層と前記Cu合金層との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、前記(N、C、F、O)層を構成する窒素、炭素、フッ素および酸素のいずれかの元素は前記半導体層のSiと結合しており、前記Cu合金層は、Cu−X合金層(第一層)と第二層とを含む積層構造である。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、電極表面を平坦化した高い信頼性を有する半導体装置およびその製造方法を提供することを目的とする。

【解決手段】n形ベース層2と、n形ベース層2の表面に設けられたp形ベース領域3と、p形ベース領域3の表面に選択的に設けられたn形エミッタ領域4と、p形ベース領域3およびn形エミッタ領域4とゲート絶縁膜を介して対向するゲート電極5と、p形ベース領域3およびn形エミッタ領域4に電気的に接続されたエミッタ電極21と、エミッタ電極21の表面に形成された凹部31を埋め込んだ絶縁部材25と、エミッタ電極21と絶縁部材25との上に設けられたエミッタ電極23と、を備えたことを特徴とする半導体装置が提供される。

(もっと読む)

半導体装置及びその製造方法

【課題】接合リーク電流が低減されるとともに、セル容量への書き込み・読み出しに十分な電流駆動能力を確保することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1に形成された複数の埋め込みゲート型MOSトランジスタ2を有し、半導体基板1には素子分離領域と活性領域とが形成されており、ゲートトレンチの内部に形成され、少なくとも一部がワード線として設けられるとともに、その他の残部が、活性領域を複数の素子領域に分離する素子分離として設けられる埋め込みゲート電極31A、31Bと、ソース・ドレイン拡散層15、45とが備えられ、埋め込みゲート電極31A、31Bは、上部電極31aと下部電極31bとの積層構造とされ、且つ、半導体基板1の上面側のソース・ドレイン拡散層15、45側に配置される上部電極31aが、下部電極31bに比べて、仕事関数の低いゲート材料からなる。

(もっと読む)

基板の配線方法及び半導体製造装置

【課題】基板上に形成された配線用パターンの底部までCu埋め込みが可能な基板の配線方法を提供する。

【解決手段】真空状態に保持された処理容器100内にて配線用パターンが形成された基板を配線する方法であって、ウエハ上の配線用パターンを所望のクリーニングガスにより洗浄する前工程と、前工程後、クラスタ化された金属ガス(金属ガスクラスタCg)を用いて配線用パターン内に金属ナノ粒子を埋め込む埋め込み工程と、を含むことを特徴とする基板の配線方法が提供される。

(もっと読む)

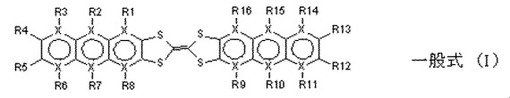

新規有機導電性膜を使用した有機電極

【課題】複雑な工程を経ることなく、テトラチアフルバレン誘導体と電子受容性化合物とを積層させるだけで、簡便かつ高電気伝導度を有する積層膜を提供する。

【解決手段】一般式(I)で表されるテトラチアフルバレン誘導体と電子受容性化合物の積層膜

(式(I)中、Xは炭素原子または硫黄原子または窒素原子から選択される原子であり同一でも異なっていても良い。Xに炭素原子及び窒素原子が選択される場合においてR1〜R16は水素原子、ハロゲン原子、置換および無置換のアルキル基またはアルコシキ基またはチオアルコキシ基から選択される基であり同一でも異なっていても良い。)。

(もっと読む)

薄膜トランジスタ基板および表示デバイス

【課題】Cu系合金配線膜を半導体層と直接接続しても接触抵抗率が低く、かつ密着性に優れた薄膜トランジスタ基板を提供する。

【解決手段】薄膜トランジスタの半導体層33と、Cu合金層28b、29bとを有する薄膜トランジスタ基板において、前記半導体層33と前記Cu合金層28b、29bとの間に、酸素含有層28a、29aを含んでおり、前記酸素含有層28a、29aを構成する酸素の一部若しくは全部は、前記薄膜トランジスタの前記半導体層33のSiと結合しており、前記Cu合金層28b、29bは、合金元素としてX(Xは、Mn、Ni、Zn、およびMgよりなる群から選ばれる少なくとも1種)を合計で2原子%以上20原子%以下含有し、前記Cu合金層28b、29bは、前記酸素含有層28a、29aを介して前記薄膜トランジスタの前記半導体層33と接続していることを特徴とする薄膜トランジスタ基板である。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のMISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、第1,第2のMISトランジスタTr1,Tr2を備えている。第1,第2のMISトランジスタは、第1,第2の活性領域10a,10b上に形成され、第1,第2の高誘電率膜13a,13bを有する第1,第2のゲート絶縁膜13A,14Bと、第1,第2のゲート絶縁膜上に形成された第1,第2のゲート電極18A,18Bとを備えている。第1のゲート絶縁膜13Aと第2のゲート絶縁膜14Bとは、第1の素子分離領域11L上において分離されている。第1の素子分離領域11Lを挟んで対向する第1の活性領域10aの一端と第2の活性領域10bの一端との距離をsとし、第1の活性領域10aの一端から第1の素子分離領域11L上に位置する第1のゲート絶縁膜13Aの一端までの突き出し量をd1としたとき、d1<0.5sの関係式が成り立っている。

(もっと読む)

半導体素子

半導体素子(例えば、フリップチップ)は、介在層によってドレインコンタクトから分離されたサブストレートを含む。前記介在層を通じて延びる前記素子の動作時において、トレンチ状のフィードスルー要素を用いて、前記ドレインコンタクトおよび前記サブストレートを電気的に接続する。 (もっと読む)

半導体素子の製造方法

【課題】本発明は、歩留まりを向上できる半導体素子の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体素子の製造方法は、半導体基板上に第1の絶縁膜を形成する工程と、前記第1の絶縁膜の一部をエッチングして複数段の段部を形成する工程と、前記第1の絶縁膜上に前記段部を覆うように導電層を形成する工程と、前記導電層の前記段部を覆う部分をエッチングする工程と、を備えることを特徴とするものである。

(もっと読む)

薄膜トランジスタアレイ基板、発光パネル及びその製造方法並びに電子機器

【課題】製造中のパーティクルの発生を低減して、歩留まりを改善することができる基板構造を有する薄膜トランジスタアレイ基板、該薄膜トランジスタアレイ基板を適用した発光パネル及びその製造方法、並びに、該発光パネルを実装した電子機器を提供する。

【解決手段】基板11上に形成されるトランジスタTr11、Tr12に接続される配線層のうち、最上層に形成される配線(電源電圧ラインLa、選択ラインLs)表面の少なくとも一部が陽極酸化膜で形成されている。

(もっと読む)

半導体基板表面を活性化するための溶液及びプロセス

【課題】半導体基板表面を活性化するための溶液及びプロセスの提供。

【解決手段】本発明は、その後の工程で無電解法により金属層を堆積させて被覆できるように、ポリマーから形成される少なくとも1つの領域を含む基板表面を活性化するための溶液及びプロセスに関する。また、本発明によれば、この組成物は、A)1以上のパラジウム錯体から形成される活性化剤と;B)少なくとも2つのグリシジル官能基及び少なくとも2つのイソシアネート官能基を含む各化合物から選択される1以上の有機化合物から形成される結合剤と;C)上記活性化剤及び上記結合剤を溶解可能な1以上の溶媒から形成される溶媒系とを含有する。用途:特に集積回路、とりわけ3次元集積回路、などの電子デバイスの製造。

(もっと読む)

半導体装置およびその作製方法

【課題】半導体装置の製造コストを低減することを課題の一とする。半導体装置の開口率を向上することを課題の一とする。半導体装置の表示部を高精細化することを課題の一とする。高速駆動が可能な半導体装置を提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と表示部とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され、且つチャネル層が酸化物半導体によって構成された駆動回路用TFTと、金属によって構成された駆動回路用配線とを有すればよい。また、当該表示部はソース電極及びドレイン電極が酸化物導電体によって構成され、且つ半導体層が酸化物半導体によって構成された画素用TFTと、酸化物導電体によって構成された表示部用配線とを有すればよい。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に第1の薄膜トランジスタを有する画素部と第2の薄膜トランジスタを有する駆動回路を有し、画素部の薄膜トランジスタは、ゲート電極層、ゲート絶縁層、膜厚の薄い領域を周縁に有する酸化物半導体層、酸化物半導体層の一部と接する酸化物絶縁層、ソース電極層及びドレイン電極層、及び画素電極層とを有し、第1の薄膜トランジスタのゲート電極層、ゲート絶縁層、酸化物半導体層、ソース電極層、ドレイン電極層、酸化物絶縁層、及び画素電極層は透光性を有し、駆動回路部の薄膜トランジスタのソース電極層及びドレイン電極層は、保護絶縁層で覆われ、画素部のソース電極層及びドレイン電極層よりも低抵抗の導電材料である半導体装置を提供する。

(もっと読む)

電子デバイス及びオーミック電極形成方法

【課題】低温短時間のアニールによっても、低いコンタクト抵抗を得ることのできるオーミック電極を備える電子デバイスを提供する。

【解決手段】電子デバイスは、ワイドバンドギャップ化合物半導体層16と、ワイドバンドギャップ化合物半導体層16上に形成されるオーミック電極であるソース電極18及びドレイン電極とを含む電子デバイスであって、オーミック電極は、密着層40、オーミック層42、及び、酸化防止層46が、ワイドバンドギャップ化合物半導体層16側からこの順に積層されて形成された電極であり、密着層40は、バナジウム(V)からなり、かつ、厚みが300Å以下であるようにする。

(もっと読む)

半導体装置及びその製造方法

【課題】エロージョンの発生及び研磨残渣の発生がない金属からなる配線又はプラグを形成できるようにする。

【解決手段】半導体基板1上の層間絶縁膜3にコンタクトホール3aを形成する。続いて、層間絶縁膜3上に金属を含む化合物及び第1の還元性ガスを供給することにより、コンタクトホール3aを含む層間絶縁膜3の上に第1のシード層5を形成する。続いて、第1のシード層5上に金属を含む化合物及び第2の還元性ガスを供給することにより、第1のシード層5の上に第2のシード層6を形成する。続いて、第2のシード層6の上に、金属をコンタクトホール3aを埋め込むように形成する。続いて、CMP法により、層間絶縁膜3のコンタクトホール3aを除く上面に残存する金属、第2のシード層6及び第1のシード層5を除去することにより、コンタクトホール3aにプラグ7Aを形成する。

(もっと読む)

堆積錫酸カドミウム層のアニール方法および装置

マルチレイヤ構造を製造する方法は、積層体をアニールする工程を含み、該アニール工程は、不活性ガスの存在下で前記積層体を加熱する工程を含むことができ、前記積層体はカドミウムおよび錫を含む層を含む。  (もっと読む)

(もっと読む)

21 - 40 / 149

[ Back to top ]