Fターム[4M104FF27]の内容

半導体の電極 (138,591) | 構造 (12,435) | コンタクト面の位置、配置 (799) | 基板の凹部 (569)

Fターム[4M104FF27]に分類される特許

161 - 180 / 569

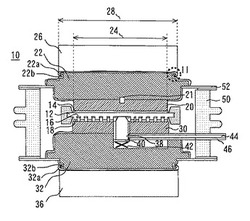

圧接型半導体装置

【課題】主電極にめっきを施しつつ、主電極の端部を含む面に圧接電極を面接合させることができる圧接型半導体装置を提供する。

【解決手段】半導体基体12と、めっき処理され、該半導体基体12の主面に固着されためっき付き主電極22と、該めっき付き主電極22のめっき22aが形成された面に重なるように圧接された圧接電極と、を備える。そして、該めっき付き主電極22の側面には溝22bが形成され、該溝22bは、該半導体基体12と該めっき付き主電極22が重なる部分の直上領域より外側に形成されたことを特徴とする。

(もっと読む)

整流器ブリッジ回路

【課題】本発明の課題は、ロードダンプの場合、すなわち負荷の遮断の急に行われる場合にも、ロードダンプエネルギが全てのダイオードに均等に分配される整流器ブリッジ回路を提供することである。

【解決手段】前記課題は、請求項1に従う整流器ブリッジ回路によって解決される。

(もっと読む)

DC/DCコンバータ用半導体装置

【課題】半導体装置の電源電圧の変換効率を向上させる。

【解決手段】ハイサイドスイッチ用のパワーMOS・FETとローサイドスイッチ用のパワーMOS・FETとが直列に接続された回路を有する非絶縁型DC−DCコンバータにおいて、ローサイドスイッチ用のパワーMOS・FETと、そのローサイドスイッチ用のパワーMOS・FETに並列に接続されるショットキーバリアダイオードD1とを同一の半導体チップ5b内に形成した。ショットキーバリアダイオードD1の形成領域SDRを半導体チップ5bの短方向の中央に配置し、その両側にローサイドのパワーMOS・FETの形成領域を配置した。また、半導体チップ5bの主面の両長辺近傍のゲートフィンガ6aから中央のショットキーバリアダイオードD1の形成領域SDRに向かって、その形成領域SDRを挟み込むように複数本のゲートフィンガ6bを延在配置した。

(もっと読む)

半導体装置

【課題】III-V族窒化物半導体に設けるオーミック電極のコンタクト抵抗を低減しながらデバイスの特性を向上できるようにする。

【解決手段】半導体装置(HFET)は、SiC基板11上にバッファ層12を介在させて形成された第1の窒化物半導体層13と、該第1の窒化物半導体層13の上に形成され、該第1の窒化物半導体層13の上部に2次元電子ガス層を生成する第2の窒化物半導体層14と、該第2の窒化物半導体層14の上に選択的に形成されたオーム性を持つ電極16、17とを有している。第2の窒化物半導体層14は、底面又は壁面が基板面に対して傾斜した傾斜部を持つ断面凹状のコンタクト部14aを有し、オーム性を持つ電極16、17はコンタクト部14aに形成されている。

(もっと読む)

凹部バリア層を備えた高電子移動度トランジスタ

【課題】高電子移動度トランジスタ(HEMT)で、凹部バリア層を備え、バリア層間にゲート電極を形成することにより、エンハンスメント型FETを提供する。

【解決手段】基板上104上にバッファ108層を形成し、バッファ層上にスペーサ層112を形成し、スペーサ層上にバリア層116を形成する。バリア層内に凹部を形成し、凹部を通して、少なくてもその一部が前記スペーサ層上に配置されるようにゲート構造140を形成する。

(もっと読む)

ショットキダイオードおよびその製造方法

【課題】確実なノーマリオフ動作とリーク電流の少ないショットキダイオードを提供する。

【解決手段】基板31表面にバッファ層32とUID-GaN層33とUID-AlGaN層34とが順次積層され、UID-GaN層とUID-AlGaN層との界面のUID-GaN層側に2DEG層35が発生するエピタキシャル基板と、UID-AlGaN層の表面に形成されたオーミックアノード電極39とオーミックカソード電極40と、オーミックアノード電極とオーミックカソード電極との間のオーミックアノード電極の側面に隣接して形成されたショットキアノードリセス36を少なくとも覆う熱CVDSiNショットキアノード絶縁膜37と、絶縁膜の表面のショットキアノードリセス内に形成されたショットキアノード電極41とを少なくとも備え、オーミックアノード電極とショットキアノード電極とが接続されている。

(もっと読む)

半導体装置

【課題】コンタクト抵抗が小さいオーミック電極を備えたIII−V族窒化物半導体を用いた半導体装置を実現できるようにする。

【解決手段】半導体装置は、基板11の上に順次形成された、第1のIII−V族窒化物半導体層12及び第1のIII−V族窒化物半導体12と比べてバンドギャップが大きい第2のIII−V族窒化物半導体層13と、p型の導電型を有する第3のIII−V族窒化物半導体層21と、第1のオーミック電極14とを備えている。第1のオーミック電極14は、下部が第2のIII−V族窒化物半導体層13及び第3のIII−V族窒化物半導体層21を貫通し且つ第1のIII−V族窒化物半導体層12における2次元電子ガス層よりも下側の領域に達するように形成されている。

(もっと読む)

III族窒化物半導体素子、III族窒化物半導体素子の製造方法、および電子装置

【課題】 アクセス抵抗およびオン抵抗が低いIII族窒化物半導体素子、III族窒化物半導体素子の製造方法、および電子装置を提供する。

【解決手段】

障壁層902は、チャネル層901上方にヘテロ接合され、

チャネル層901の上部の一部およびその上方の障壁層902が除去されて凹部が形成され、

チャネル層901および障壁層902の一部にn型導電層領域904が形成され、

n型導電層領域904は、前記凹部の表面を含み、

n型導電層領域904の深さTimpが、n型導電層領域904表面の各部から前記表面と垂直方向の測定値で15nm以上であり、

オーミック電極906および907は、前記凹部の表面を介して前記n型導電層領域にオーミック接触していることを特徴とする、III族窒化物半導体素子。

(もっと読む)

DC/DCコンバータ用半導体装置

【課題】半導体装置の電源電圧の変換効率を向上させる。

【解決手段】ハイサイドスイッチ用のパワーMOS・FETとローサイドスイッチ用のパワーMOS・FETとが直列に接続された回路を有する非絶縁型DC−DCコンバータにおいて、ローサイドスイッチ用のパワーMOS・FETと、そのローサイドスイッチ用のパワーMOS・FETに並列に接続されるショットキーバリアダイオードD1とを同一の半導体チップ5b内に形成した。ショットキーバリアダイオードD1の形成領域SDRを半導体チップ5bの短方向の中央に配置し、その両側にローサイドのパワーMOS・FETの形成領域を配置した。また、半導体チップ5bの主面の両長辺近傍のゲートフィンガ6aから中央のショットキーバリアダイオードD1の形成領域SDRに向かって、その形成領域SDRを挟み込むように複数本のゲートフィンガ6bを延在配置した。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の内部に腐食が進行することを抑制する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置100は、化合物半導体基板101と、化合物半導体基板101上の一部に形成された接続部119と接続部119上に形成されかつ接続部119より幅広の本体部117とを有しており、かつアルミニウムを含むゲート電極118と、ゲート電極118の表面上に設けられた保護絶縁層(シリコン窒化膜120)と、シリコン窒化膜120が被覆していないゲート電極118の表面に設けられており、アルミニウムよりも酸化されにくい不動態膜124と、を備える。

(もっと読む)

高電圧スイッチング回路

【課題】高電圧処理能力および改善された実行能力を有する効率的なスイッチング回路を提供する。

【解決手段】第1および第2のIII−V族トランジスタを有し、第2のIII−V族トランジスタは、第1のIII−V族トランジスタよりも大きな降伏電圧を有する。さらに、第1のIII−V族トランジスタと並列に配置されるシリコンダイオードを有し、この並列配置は、第2のIII−V族トランジスタと直列に接続、効率的な3端子デバイスであり、第1端子は第2のIII−V族トランジスタのゲート、第1のIII−V族トランジスタのソースおよびシリコンダイオードのアノードに結合する。第2端子は第1のIII−V族トランジスタのゲートと結合し、第3端子は第2III−V族トランジスタのドレインと結合する。

(もっと読む)

半導体装置

【課題】高電圧を印加した際に逆バイアスにおけるリーク電流が少なく、順方向電圧降下Vfが低い整流素子を有する単一基板上にトランジスタ素子と整流素子を一体にした半導体装置を提供する。

【解決手段】半導体装置10は、単一の基板11上にトランジスタ素子12と整流素子13とを備える半導体装置10であって、トランジスタ素子12は、基板11上に形成された活性層14と、活性層14に接合されたソース電極15とドレイン電極16とゲート電極17を備え、整流素子13は、活性層14に接合されたアノード電極18と、ドレイン電極16を用いたカソード電極と、アノード電極18とカソード電極の間に第1の補助電極19を備えた。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、電極表面を平坦化した高い信頼性を有する半導体装置およびその製造方法を提供することを目的とする。

【解決手段】n形ベース層2と、n形ベース層2の表面に設けられたp形ベース領域3と、p形ベース領域3の表面に選択的に設けられたn形エミッタ領域4と、p形ベース領域3およびn形エミッタ領域4とゲート絶縁膜を介して対向するゲート電極5と、p形ベース領域3およびn形エミッタ領域4に電気的に接続されたエミッタ電極21と、エミッタ電極21の表面に形成された凹部31を埋め込んだ絶縁部材25と、エミッタ電極21と絶縁部材25との上に設けられたエミッタ電極23と、を備えたことを特徴とする半導体装置が提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】製造が容易で、かつ高い耐圧を確保しながら低損失化を図ることができる半導体装置を提供すること、およびその半導体装置を製造するための製造方法を提供する。

【解決手段】半導体装置としてのショットキーダイオード10は、半導体からなる基板11と、基板11上に形成されたn型層12とを備えている。n型層12は基板11側の表面である第1の面12Aとは反対側の表面である第2の面12Bから第1の面12Aに向けて延びるように形成された溝13を有している。溝13の底部である底壁13Aに接触する位置には絶縁体としての酸化物層14が配置されており、かつ溝13の側壁13Bに接触するようにn型層12とショットキー接触可能な金属膜15が溝13を埋めるように形成されている。さらに、n型層12の第2の面12Bに接触するようにアノード電極16が配置されている。

(もっと読む)

半導体装置およびその製造方法

【課題】特性を劣化させることなく、微細化することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、主表面を有する半導体基板SBと、主表面に互いに間隔をおいて形成されたソース領域SRおよびドレイン領域DRと、ソース領域SRとドレイン領域DRとに挟まれる主表面上に形成されたゲート電極層GEと、ソース領域SRの表面に接するように形成された第1導電層PL1と、ドレイン領域DRの表面に接するように形成された第2導電層PL2とを備え、第1導電層PL1とソース領域SRとの接触領域CR1からゲート電極層GEの下側を通って第2導電層PL2とドレイン領域DRとの接触領域CR2まで延びるように溝REが主表面に形成されている。

(もっと読む)

半導体発光素子

【課題】電流密度分布の分散化を図り、発光分布の均質化を図ることができる半導体発光素子を提供する。

【解決手段】第1導電型の第1半導体層と、第2導電型の第2半導体層と、第1半導体層10と第2半導体層2との間に設けられた発光部と、を有する積層構造体と、積層構造体の第1半導体層の第1主面において、第2半導体層及び発光部が選択的に除去され、第1主面の側において第1半導体層が露出した面に設けられた第1電極40と、第1主面の側において、第2半導体層の一部に設けられた第2電極50と、を備え、第1電極40は、第1パッド部41と、第1パッド部41から延出する第1延出部42と、を有し、第1延出部42は、第1延出部42の延出方向に対して直交する方向に沿った幅が、第1パッド部41から第1延出部42の先端に向かうに従って漸増する漸増部分421を含む。

(もっと読む)

シリコンおよびIII−V族のモノリシック集積デバイス

【課題】シリコン基板上にIII−V族半導体で形成されたHEMTとシリコン面に形成されたショツトキーダイオードのモノリシック集積デバイスを開示する。

【解決手段】少なくとも1つのビアは、III−V族半導体を通じて延在して、III−V族トランジスタの少なくとも1つの端子をシリコン基板に形成されたシリコンデバイスに結合させる。シリコンデバイスはショットキーダイオードと、III−V族トランジスタはGaNHEMTとすることができる。ショットキーダイオードのアノードは、一実施形態においては、シリコン基板202に形成され、他の実施形態においては、シリコン基板上の低濃度にドープされたエピタキシャルシリコン層204に形成される。HEMTはGANで構成されたチヤネル層212、AlGaNで構成された電子供給層214より構成される。

(もっと読む)

パワー素子を備えた半導体装置の製造方法

【課題】電子線照射等の後に行う水素アニール時に水素が十分にデバイスを構成する半導体のダメージ部分まで到達し、ダメージ回復が行えるようにすると共に、表面電極の劣化を抑制することができるようにする。

【解決手段】IGBTが形成されたセル領域全面に形成された表面電極11に含まれるバリアメタル12の第1金属膜12aをチタン(Ti)ではなく、ニッケル(Ni)やコバルト(Co)等のVIII族の金属材料により構成する。これにより、水素アニールの際に、電子線照射等によってダメージを受けたシリコン表面に水素が到達するようにできる。また、バリアメタル12の第1金属膜12aを構成する金属材料が水素と結合しないようにできる。したがって、水素アニール時に水素が十分にシリコン表面のダメージ部分まで到達し、ダメージ回復が行えるようにすることができると共に、表面電極11の劣化を抑制することができる。

(もっと読む)

窒化物半導体デバイス

【課題】 窒化物半導体デバイスを提供する。

【解決手段】 一実施形態では、デバイスはIII族窒化物チャネル層(3)とIII族窒化物チャネル層(3)上のIII族窒化物障壁層(4)とを含み、III族窒化物障壁層(4)は第1部分(4−1)と第2部分(4−2)とを含み、第1部分(4−1)は第2部分(4−2)より薄い厚さを有する。pドープIII族窒化物ゲート層部(5)は、III族窒化物障壁層(4)の少なくとも第1部分(4−1)上に配置され、ゲートコンタクト(10)はpドープIII族窒化物ゲート層部(5)上に形成される。

(もっと読む)

半導体装置

【課題】Ti、PtおよびAuからなるゲート電極を有するリセス構造を有し、Ti上のPt若しくはAuが、素子領域表面のAlGaAs層に拡散することを抑制する半導体装置を提供する。

【解決手段】GaAs基板11上に形成された素子領域16と、第1のリセス領域25と、第2のリセス領域26と、第1のリセス領域25外の素子領域16上に、互いに離間して形成されたドレイン電極13およびソース電極14と、第2のリセス領域26の表面の一部に接し、第1のリセス領域25の表面の一部に接するゲート電極15を具備し、最下層が、第1のリセス領域25、および第2のリセス領域26の表面の一部に接するように、隙間を有して形成された第1のTi層29と、第1のTi層29上に、第1のTi層29の隙間を埋めるように形成されたAl層30と、Al層30上に形成されたPt層32と、Pt層上に形成されたAu層33と、を含むように構成する。

(もっと読む)

161 - 180 / 569

[ Back to top ]