Fターム[4M104GG10]の内容

Fターム[4M104GG10]に分類される特許

201 - 220 / 2,910

半導体装置、半導体集積回路装置及び半導体装置の製造方法

【課題】高耐圧且つ低オン抵抗な半導体装置及びこれを含む半導体集積回路装置を歩留まり良く、安価に提供する。

【解決手段】第1導電型の半導体基板(1)と、前記第1導電型と反対の第2導電型であって前記半導体基板の表面側に形成されたソース領域(11)、低濃度ドレイン領域(12)及び高濃度ドレイン領域(13)と、前記半導体基板上に形成されたゲート絶縁膜(14)と、前記ゲート絶縁膜上に形成されたゲート電極と、を備える半導体装置(10)であって、

前記ゲート電極は、前記低濃度ドレイン領域の少なくとも一部を覆うように形成され、且つ、前記低濃度ドレイン領域の上方において開孔(16)を有することを特徴とする半導体装置。前記低濃度ドレイン領域と高濃度ドレイン領域とは互いに隣接することが好ましい。

(もっと読む)

薄膜トランジスタ、発光装置、電子機器、及び、薄膜トランジスタの形成方法

【課題】ソース−ドレイン間等の電圧−電流特性を改善することができる薄膜トランジスタ、発光装置、電子機器、及び、薄膜トランジスタの形成方法を提供する。

【解決手段】薄膜トランジスタ100は、半導体膜119と、半導体膜119の上方に形成されたソース電極層140と、半導体膜119の上方に形成されたドレイン電極層142と、ソース電極層140とドレイン電極層142との間、かつ、半導体膜119の上方に形成されたチャネル保護膜113と、を備える薄膜トランジスタであって、ソース電極層140とドレイン電極層142の少なくとも何れか一方は、チャネル保護膜113と接し、その上面がチャネル保護膜113の上面を超えない接触領域を有して、チャネル保護膜113の上面と重なっていない。

(もっと読む)

半導体装置およびその製造方法

【課題】MRAMを含む半導体装置において、MRAMの特性を向上することができる技術を提供する。

【解決手段】配線L3およびデジット配線DLを形成した層間絶縁膜IL3の表面に対してプラズマ処理を実施する。まず、半導体基板1Sをチャンバ内に搬入し、窒素を含有する分子(アンモニアガス)と窒素を含有しない不活性分子(水素ガス、ヘリウム、アルゴン)とからなる混合ガスをチャンバ内に導入する。このとき、窒素を含有する分子の流量よりも窒素を含有しない不活性分子の流量が多い条件で、混合ガスを導入し、混合ガスをプラズマ化してプラズマ処理を実施する。

(もっと読む)

高電子移動度トランジスタの構造、その構造を含んだデバイス及びその製造方法

【課題】MMICのSPDTスイッチなど、半導体デバイスとして用いるのに適したMOS−PHEMTの構造及びその製造方法を開示する。

【解決手段】MOS−PHEMT構造は、Al2O3、HfO2、La2O3及びZrO2からなる群から選ばれる材料からなるゲート誘電体層107を有することを特徴とし、これにより、このMOS−PHEMTの構造を含む、高周波スイッチデバイスなどの半導体構造が、直流電流の損失及び挿入損失の低下を防ぎ、隔絶性を向上させることができる。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】オフ電流および漏れ電流が抑制された薄膜トランジスタ、および前記薄膜トランジスタを歩留り良く製造することのできる薄膜トランジスタの製造方法を提供する。

【解決手段】ゲート電極12上にゲート絶縁膜12を介して順次形成されるSi(i)膜13およびSi(n)膜14上に金属膜を形成し、フォトレジストパターン22をマスクとしてエッチングし、ソース電極15およびドレイン電極16を形成する。酸素を含むプラズマで処理して、フォトレジストパターン22の側面を後退させるとともに、ソース電極15およびドレイン電極16の側面および露出した上面にAl酸化皮膜17を形成する。残存するフォトレジストパターン22およびAl酸化皮膜17をマスクとして、チャネル部18のSi(n)膜14およびSi(i)膜13の表面の一部をエッチングする。

(もっと読む)

半導体装置及びその製造方法

【課題】n型MISトランジスタとp型MISトランジスタとで異なる閾値電圧制御用金属が高誘電率ゲート絶縁膜に添加されたトランジスタ構造において、トランジスタ特性の変動を防止できるようにする。

【解決手段】第1の活性領域1a上から素子分離領域2上を経て第2の活性領域1b上まで、ゲート絶縁膜となる高誘電率膜6が形成されている。第1の活性領域1aに隣接する部分の素子分離領域2の上部には第1の切り欠き部2aが形成されている。第2の活性領域1bに隣接する部分の素子分離領域2の上部には第2の切り欠き部2bが形成されている。第2の切り欠き部2bは第1の切り欠き部2aよりも浅く形成されている。

(もっと読む)

シリサイドの形成方法及び半導体装置

【課題】 ウェット洗浄工程を増加させることなく、かつ、より低温でシリサイドを形成することが可能なシリサイドの形成方法を提供すること。

【解決手段】 表面にシリコンとシリコン酸化物とが露出している基板101上にシリサイドを形成するシリサイドの形成方法であって、基板101の温度を400℃以上として、シリコンとシリコン酸化物とが露出している基板101の表面上にマンガン有機化合物ガスを供給し、基板101の表面に露出したシリコンを選択的にマンガンシリサイド化する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を高い製造歩留まりで提供し得る半導体装置の製造方法を提供することにある。

【解決手段】側壁にサイドウォール絶縁膜が形成されたゲート配線20を形成する工程と、第1の応力膜38を形成する工程と、第1の応力膜上にエッチングストッパ膜40を形成する工程と、エッチングストッパ膜をエッチングし、第1の応力膜のうちのサイドウォール絶縁膜を覆う部分上にエッチングストッパ膜を選択的に残存させる工程と、第2の領域4を露出する第1のマスクを用いて第2の領域内の第1の応力膜をエッチングする工程と、第2の応力膜42を形成する工程と、第1の領域2を露出する第2のマスクを用いて第1の領域内の第2の応力膜をエッチングする工程と、第1の領域と第2の領域との境界部におけるゲート配線に達するコンタクトホール46aを形成する工程とを有している。

(もっと読む)

薄膜トランジスタアレイ基板、発光パネル及びその製造方法並びに電子機器

【課題】製造中のパーティクルの発生を低減して、歩留まりを改善することができる基板構造を有する薄膜トランジスタアレイ基板、該薄膜トランジスタアレイ基板を適用した発光パネル及びその製造方法、並びに、該発光パネルを実装した電子機器を提供する。

【解決手段】基板11上に形成されるトランジスタTr11、Tr12に接続される配線層のうち、最上層に形成される配線(電源電圧ラインLa、選択ラインLs)表面の少なくとも一部が陽極酸化膜で形成されている。

(もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置

【課題】MIPS構造を採るメタル膜とコンタクトプラグとの界面抵抗を低減できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を形成し、形成したゲート絶縁膜3の上に、TiN膜4及びポリシリコン膜5を順次形成する。続いて、ポリシリコン膜5にTiN膜4を露出するコンタクトホール5aを形成する。続いて、ポリシリコン膜5における第1のコンタクトホール5aの少なくとも底面及び壁面上に金属膜7を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】フィンの下部に適切に不純物が導入された半導体装置及びその製造方法を提供する。

【解決手段】半導体装置としてのFinFET1は、基体としての半導体基板10と、半導体基板10上に形成された複数のフィン20とを有し、複数のフィン20は、第1の間隔と第1の間隔よりも間隔が狭い第2の間隔とを繰り返して形成され、第1の間隔を形成する側に面した第1の側面221の下部の不純物濃度が、第2の間隔を形成する側に面した第2の側面222の下部の不純物濃度よりも高い半導体領域を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】シリサイド領域と非シリサイド領域が混在する半導体装置において、シリサイド領域の狭ゲート電極間にシリサイドプロテクション膜残りによるシリサイド形成不良を防止し、非シリサイド領域において確実にシリサイド化反応を防止する製造方法を提供する。

【解決手段】同一の半導体基板のシリサイド領域Aと非シリサイド領域Bを備える半導体装置の製造方法は、半導体基板101上の全面にゲート電極103を覆うように堆積した第1のシリコン酸化膜104をエッチングして、ゲート電極103の側面に断面I字状のオフセットサイドウォール104aをシリサイド領域Aに形成し、シリサイドプロテクション膜104bを非シリサイド領域Bに形成する。続いて、内側サイドウォール106、外側サイドウォール107、及び不純物拡散層108を形成した後、シリサイド領域Aのゲート電極103及び不純物拡散層108上に金属シリサイド層110を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】より高い耐熱性を有するシリサイド層を備えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100の製造方法は、半導体基板2上にゲート絶縁膜4を介してゲート電極5を形成する工程と、半導体基板2上のゲート電極5の両側に、Ge含有領域8を形成する工程と、半導体基板2およびGe含有領域8のゲート電極5の両側の領域中に、ソース・ドレイン領域9を形成する工程と、Ge含有領域8上に、濃度5原子%以上のPdを含む金属シリサイドからなるシリサイド層11を形成する工程と、シリサイド層11を形成した後、半導体基板2に650〜750℃の熱処理を施す工程と、を含む。

(もっと読む)

PFETチャネルSiGeを有する金属ゲート及び高k誘電体デバイス

【課題】SiGeから成るチャネルを有し、金属ゲート及び高kゲート誘電体を有するPFETを提供する。

【解決手段】Si表面上にSiGe層10をエピタキシャル成長させ、SiGe層の上に、高k誘電体及び金属をブランケット配置し、ゲートスタックを形成した後、NFET側のゲート誘電体、及びSiGe層を除去し、第2の高k誘電体53及び第2の金属52を配置する。PFETは、SiGeチヤネル10の上の高k誘電体を有するゲート誘電体、金属を有するゲート及び、シリサイドを有するソース、ドレインから成る。NFETは、第2の高k誘電体53、第二の金属52を有するゲート及び、シリサイドを有するソース、ドレインからなる。基板表面上のエピタキシャルSiGe層は、PFETのチヤネルのみに形成される。PFET及びNFETデバイス・パラメータは、各ゲート誘電体及びゲートスタックの組成によって別個に最適化することができる。

(もっと読む)

酸素拡散バリア層を有する半導体デバイスおよびそれを製造するための方法

方法および装置はトランジスタを製造するために提供される。トランジスタが、半導体材料104、106、108、110上に配置されたゲートスタック142、144、146を備える。ゲートスタックが、半導体材料上に堆積される酸化物層126、堆積された酸化物層上に配置された酸素拡散バリア層128、酸素拡散バリア層上に配置された高誘電率の誘電体層134、および高誘電率の誘電体層上に配置された酸素ゲッター導電性層138を備える。酸素拡散バリア層が、堆積された酸化物層から酸素ゲッター導電性層への酸素の拡散を防止する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の下部からゲート電極の形成されていない基板上の領域に斜め方向のイオン注入を行って形成される不純物拡散領域を有する半導体装置において、半導体装置のサイズを従来に比して縮小化することができる半導体装置を提供する。

【解決手段】N型半導体層13の表面に形成されるP型のベース領域21と、ベース領域21内に形成されるP+型ソース領域22およびN+型ソース領域23を有するソース領域と、N型半導体層13の表面にベース領域21から離れて形成されるN+型のドレイン領域26と、ソース領域とドレイン領域26との間にゲート絶縁膜41を介して形成されるゲート電極42と、ドレイン領域26からゲート電極42の下部にかけて、ドレイン領域26に隣接して形成されるN型のドリフト領域と、を備え、ゲート電極42とゲート絶縁膜41との積層体のソース領域側側面の高さが、ドレイン領域側側面の高さよりも高く形成される。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に対する不純物の突き抜けを抑止する。

【課題を解決するための手段】半導体装置の製造方法は、基板上方に成膜した多結晶シリコンをエッチングして基板の第1領域上方に第1ゲート電極を形成し、基板の第2領域上方に第2ゲート電極を形成し、第1領域及び第1ゲート電極を覆う第1パターンを形成し、第2ゲート電極及び第1パターンをマスクにして第2領域に第1不純物を第1ドーズ量で注入して第2領域に第1エクステンション領域を形成し、第1ゲート電極、第1領域及び第2ゲート電極の上面を露出させた第2パターンを形成し、第1エクステンション領域を覆い、第1ゲート電極、第2ゲート電極及び第2パターンをマスクにして第1領域に第2不純物を第1ドーズ量よりも多いドーズ量で注入して第1領域に第2エクステンション領域を形成するとともに、第1ゲート電極及び第2ゲート電極の少なくとも上部をアモルファス化する。

(もっと読む)

半導体デバイスおよびその製造方法

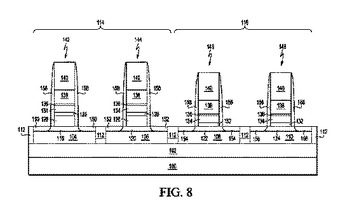

【課題】複数ゲートトランジスタの改良された構造、およびその製造プロセスの提供。

【解決手段】相補型金属酸化膜半導体(CMOS)デバイス100は、第1のパラメータを有する少なくとも2つの第1のゲート電極を備えたPMOSトランジスタと、上記第1のパラメータとは異なる第2のパラメータを有する少なくとも2つの第2のゲート電極を備えたNMOSトランジスタと、を有している。上記第1のパラメータおよび上記第2のパラメータは、上記PMOSおよびNMOSトランジスタの上記ゲート電極材料120の厚さ、またはドーパントプロファイルを含んでいる。上記少なくとも2つの第1のゲート電極および上記少なくとも2つの第2のゲート電極の上記第1および第2のパラメータは、それぞれ、上記PMOSおよびNMOSトランジスタの仕事関数を規定する。

(もっと読む)

半導体装置

【課題】駆動電力の高いフィン型のトランジスタを提供する。

【解決手段】所定の間隔で配置され、それぞれの中央部がチャネル領域、その両側部がソース/ドレイン領域となるフィン状の第1の半導体11層及び第2の半導体層11と、第1の半導体層11及び第2の半導体層11それぞれのチャネル領域の両側面にゲート絶縁膜12を介して形成されたゲート電極13と、第1の半導体層11のソース/ドレイン領域と第2の半導体層11のソース/ドレイン領域との間の溝を埋め込むように形成された絶縁膜19と、第1の半導体層11のソース/ドレイン領域及び第2の半導体層11のソース/ドレイン領域の絶縁膜19で覆われていない側面にそれぞれ形成されたシリサイド16とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生抵抗の低下を図る。

【解決手段】半導体装置は、半導体基板10と、前記半導体基板上のソース/ドレイン領域に形成された第1半導体層11と、前記第1半導体層上に形成された第1部分12aと、前記ソース/ドレイン領域の間に位置するチャネル領域に形成された第2部分12bとを有する第2半導体層12と、前記第2半導体層の前記第1部分上に形成された第3半導体層13と、前記第2半導体層の前記第2部分の周囲に絶縁膜21を介して形成されたゲート電極22と、前記第1半導体層、前記第2半導体層の第1部分および前記第3半導体層内に形成されたコンタクトプラグ31と、を具備し、前記第2半導体層内における前記コンタクトプラグの径は、前記第1半導体層及び前記第3半導体層内における前記コンタクトプラグの径より小さい。

(もっと読む)

201 - 220 / 2,910

[ Back to top ]