Fターム[4M104GG10]の内容

Fターム[4M104GG10]に分類される特許

161 - 180 / 2,910

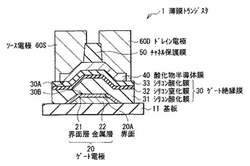

薄膜トランジスタおよびその製造方法、並びに表示装置

【課題】チャネルへの不純物添加を行うことなく閾値電圧を大きくすることが可能な薄膜トランジスタおよびその製造方法、並びに表示装置を提供する。

【解決手段】基板11にゲート電極20を形成したのち、このゲート電極20の表面から厚み方向における一部を、熱処理またはプラズマ処理を用いて酸化させることにより、ゲート電極20のゲート絶縁膜30との界面20Aから厚み方向における一部を、金属酸化物よりなる界面層21とする。ゲート電極20のゲート絶縁膜30との界面20Aにおける仕事関数が大きくなるので、ゲート電極20と酸化物半導体膜40との仕事関数差φMSが大きくなり、閾値電圧Vthが大きくなる。

(もっと読む)

半導体装置及びその製造方法

【課題】MISトランジスタにおけるシリコン混晶層からなるソースドレイン領域を、不純物の拡散による不具合を防止しながらチャネル領域に近づけることができるようにする。

【解決手段】半導体装置は、半導体基板10からなるn型の活性領域の上に、ゲート絶縁膜12を介在させて形成されたゲート電極13と、活性領域におけるゲート電極13の両側方の領域に形成されたp型ソースドレイン領域20と、活性領域における各p型ソースドレイン領域20の側面からそれぞれゲート電極13の下側に向かって形成されたn型ポケット領域18とを有している。p型ソースドレイン領域20は、シリコンとIV族元素との混晶層からなり、混晶層は、ゲート長方向におけるゲート電極側の側面がゲート電極側に突き出す凸部20aを有している。凸部20aの先端は、ポケット領域18によって覆われている。

(もっと読む)

半導体素子の製造方法

【課題】埋込みビットラインのビットラインコンタクトの形成方法を提供する。

【解決手段】半導体基板をエッチングして複数のピラー115を形成するステップと、ピラーの側壁に第1保護膜120を蒸着するステップと、第1保護膜が蒸着されたピラーをマスクとして半導体基板を1次エッチングするステップと、1次エッチングされた半導体基板及びピラーの側壁に第1絶縁膜125を形成するステップと、第1絶縁膜が形成されたピラーをマスクとして半導体基板を2次エッチングするステップと、2次エッチングされた半導体基板の表面に第2保護膜130及び第2絶縁膜135を形成するステップと、第2絶縁膜を含むピラーの側壁にバリア膜140を蒸着するステップと、ピラーの一側面のバリア膜、第1及び第2絶縁膜を除去し、第1保護膜及び第2保護膜により画成されるコンタクトホールを形成するステップと、を含む。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減と、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】凹部4c内に形成されたi型(イントリンシック半導体)側壁層5を介してp+型ゲート領域6を形成する。このような構成とすれば、n+型層4とp+型ゲート領域6との間にさらにp+型ゲート領域6よりも低濃度のp-型層が必要とされない。このため、n-型チャネル層3に直接接触している高濃度のp+型ゲート領域6によって、n-型チャネル層3内に伸びる空乏層幅を制御できる。したがって、n+型層4とp+型ゲート領域6との間にさらにp-型層が備えられる場合と比較して、ゲート印加電圧が高電圧になることを抑制できる。また、p+型ゲート領域6の側面がi型側壁層5によってn+型層4と分離されるため、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスを低減できる。

(もっと読む)

半導体装置

【課題】ロジック系CMOSトランジスタおよびパワー系DMOSトランジスタのそれぞれが最適な構造を有する半導体装置を提供する。

【解決手段】第1半導体領域2の表面側に設けられた第1ソース領域3、ドレイン領域4と、第1ゲート13と、第1ゲートの両側面に形成された第1サイドウォール15と、第1LDD領域17とを有する第1のMOSトランジスタと、第2半導体領域22の表面側に設けられた第2ソース領域23、ドレイン領域24と、第2ゲート33と、第2ゲートの第2ドレイン側の側面に形成され、第1サイドウォールよりも広い第2サイドウォール41と、第2サイドウォール直下に形成されたドリフト領域43と、第2ゲートの第2ソース側の側面に形成され、第1サイドウォールよりも狭い第3サイドウォール35と、第3サイドウォール直下に形成された第2LDD領域37とを有する第2のMOSトランジスタを備えた半導体装置を提供する。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】ゲート電極構造の垂直方向の抵抗を低減する。

【解決手段】半導体基板1と、半導体基板1の上に形成されたゲート絶縁膜2と、ゲート絶縁膜2の上に形成された仕事関数制御層3と、仕事関数制御層3の上に形成された第1のシリサイド層4と、第1のシリサイド層4の上に形成されたポリシリコンゲート電極5と、ポリシリコンゲート電極5の下の半導体基板1中の領域を挟んで半導体基板1中に形成されるソース領域6およびドレイン領域7と、を有する半導体装置を提供する。

(もっと読む)

電界効果型トランジスタ

【課題】電流許容値の低下を抑制する。

【解決手段】Y方向に沿って延在する延在ゲート電極G11と、Y方向に沿って延在するダミーゲート電極DM1と、Y方向に沿って延在する延在ソース電極S11と、Y方向に沿って延在する延在ドレイン電極D11とを含む。延在ソース電極G11は、X方向においてダミーゲート電極DM1を覆う形状を有する。また、延在ドレイン電極G11は、X方向においてダミーゲート電極DM1を覆う形状を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極抵抗の増大や工程数の増加を招くことなく、シリコン混晶層を用いた歪技術により、半導体装置の高性能化を実現する。

【解決手段】半導体基板100における第1のゲート電極106Aから見て第1の絶縁性サイドウォールスペーサ111Aの外側に第1のソースドレイン領域114Aを形成する。その後、半導体基板100における第2のゲート電極106Bから見て第2の絶縁性サイドウォールスペーサ111Bの外側にリセス部119を形成すると共に、第2のゲート電極106Bを部分的に除去する。その後、リセス部109内に、第2のソースドレイン領域114Bとなるシリコン混晶層120を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】CMPによるダミーゲート電極の頭出し工程およびCMPによるメタルゲート電極の形成工程を回避できる製造方法を提供する。

【解決手段】シリサイド膜24S,24D上に選択的に、シリコン膜25S,25Dを形成する工程と、側壁絶縁膜23WA,23WBの間にシリコン基板の表面を露出する凹部23Vを形成する工程と、側壁絶縁膜23WA,23WBの表面および露出されたシリコン基板表面を連続して覆うように、誘電体膜を形成する工程と、シリコン基板上に金属または導電性金属窒化物を含む導電膜を、凹部23Vに誘電体膜を介して充填するように形成する工程と、導電膜をエッチバックし、側壁絶縁膜23WA,23WBの間において凹部23Vを誘電体膜を介して充填するゲート電極を形成する工程と、を含む。

(もっと読む)

半導体集積回路および半導体集積回路設計方法

【課題】チップサイズを縮小化すること。

【解決手段】第1領域に形成される活性領域1と第2領域に形成されるウェル領域2とトランジスタゲート電極3とダミーゲート電極5と、コンタクト8とを備えている。活性領域1とトランジスタゲート電極3とは、トランジスタを形成している。トランジスタゲート電極3とダミーゲート電極5とは、互いに平行である複数の直線にそれぞれ沿うように形成されている。ダミーゲート電極5は、その第2領域とその第1領域との両方に配置されるように形成されている。コンタクト8は、その第2領域に形成され、ウェル領域2に同電位である配線層6にダミーゲート電極5を電気的に接続している。このような装置は、活性領域1とウェル領域2とが配置される領域のレイアウトサイズを小さくすることができ、その結果、チップサイズを縮小化することができる。

(もっと読む)

半導体装置

【課題】 占有面積の増加もなく、十分なESD保護機能を持たせたESD保護用のN型のMOSトランジスタを有する半導体装置を得ることを目的とする。

【解決手段】 絶縁膜が埋め込まれたトレンチ素子分離領域と、凹部に周囲をゲート絶縁膜で覆われたゲート電極が埋め込まれたトレンチチャネル領域と、絶縁膜が埋め込まれた凹部の周囲を濃いN型の拡散層で覆ったトレンチドレイン領域とが形成されており、ESD保護用のN型MOSトランジスタのチャネル領域には、トレンチチャネル領域が形成され、なおかつESD保護用のN型MOSトランジスタのドレイン領域には、トレンチドレイン領域が形成されている。

(もっと読む)

エピタキシャルソース/ドレインが自己整合したマルチゲート半導体デバイス

低寄生抵抗であるチャネル歪みされたマルチゲートトランジスタとその製造方法に係る。ゲートを連結したチャネル側壁の高さがHsiである半導体フィンのチャネル領域の上にゲートスタックを形成されてよく、ゲートスタックに隣接する半導体フィンのソース/ドレイン領域内に、エッチングレートを制御するドーパントを注入してよい。ドーピングされたフィン領域をエッチングして、半導体フィンの、略Hsiに等しい厚みを除去して、ゲートスタックの一部の下にある半導体基板の部分を露呈させるソース/ドレイン延長キャビティを形成してよい。露呈した半導体基板の上に材料を成長させて、再成長したソース/ドレイン・フィン領域を形成して、ソース/ドレイン延長キャビティを充填して、ゲートスタックからの長さを、チャネルの長さに実質的に平行な方向に離れる方向に延ばしてよい。 (もっと読む)

電気光学装置用基板及びその製造方法、電気光学装置並びに電子機器

【課題】電気光学装置用基板において、製造コストを低減すると共に、アライメント精度を高める。

【解決手段】電気光学装置用基板は、基板上に設けられた第1の絶縁膜(310)と、複数の画素(20)と、複数の画素にわたって第1の絶縁膜に設けられた第1の凹部と、第1の凹部の底面に設けられた第2の凹部と、第2の凹部に設けられた有機半導体層(241)と、該有機半導体層の上に設けられたゲート絶縁膜(245)と、該ゲート絶縁膜の上に設けられたゲート電極と、を含み、複数の画素のうち一の画素に対応づけられた薄膜トランジスタ(24)と、ゲート絶縁膜の上層であって、複数の画素にわたって第1の凹部に設けられた走査線(40)と、薄膜トランジスタと電気的に接続されたデータ線(50)と、を備える。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いたpチャネル型トランジスタを提供することを目的の一とする。また、酸化物半導体を用いたnチャネル型トランジスタとpチャネル型トランジスタとのCMOS(相補型金属酸化物半導体)構造を提供することを目的の一とする。

【解決手段】ゲート電極層と、ゲート絶縁層と、酸化物半導体層と、前記酸化物半導体層と接するソース電極層及びドレイン電極層とを含み、前記酸化物半導体層に用いる酸化物半導体の電子親和力をχ(eV)、バンドギャップをEg(eV)とすると、前記ソース電極層及び前記ドレイン電極層に用いる導電体の仕事関数φmは、φm>χ+Eg/2を満たし、かつ、χ+Eg−φmで表される正孔に対する障壁φBPは0.25eV未満である、酸化物半導体を用いたpチャネル型トランジスタを提供する。

(もっと読む)

半導体素子、半導体装置及びそれらの作製方法

【課題】チャネル長Lが短く微細化が可能な、酸化物半導体を用いたトップゲート型の半導体素子を提供することを課題とする。また、該半導体素子の作製方法を提供することを課題とする。

【解決手段】絶縁表面上に酸化物半導体層と、酸化物半導体層上にソース電極層及びドレイン電極層と、酸化物半導体層、前記ソース電極層、及び前記ドレイン電極層上にゲート絶縁層と、ゲート絶縁層上にゲート電極層とを有し、ソース電極層及びドレイン電極層は側壁を有し、側壁は前記酸化物半導体層の上面と接する半導体素子である。

(もっと読む)

半導体装置、および、その製造方法

【課題】半導体素子の特性を向上させると共に、半導体素子の微細化を容易に実現する。

【解決手段】半導体素子101にてゲート電極111gが設けられる部分の表面を凹凸面に形成する。ここでは、凹凸面のうち凸部CVでは、一対のソース・ドレイン領域112s,112dの表面と同一の面を覆うようにゲート絶縁膜111zを形成し、そのゲート絶縁膜111zの上面にゲート電極111gを設ける。これに対して、凹部TRでは、一対のソース・ドレイン領域112s,112dの表面から内部へ向けて設けられた溝Mの面を覆うようにゲート絶縁膜111zを形成し、その溝Mの内部を埋め込むようにゲート電極111gを設ける。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を提供し得る半導体装置の製造方法を提供することにある。

【解決手段】第2の応力膜44に対する第2の絶縁膜48の選択比が第1の値である第1の条件でエッチングを行うことにより、第1のコンタクトホール60eを少なくとも第2の応力膜の途中まで開口し、第2のコンタクトホールを少なくとも第2の絶縁膜の途中まで開口するエッチング工程と、第2の応力膜に対する第2の絶縁膜の選択比が第1の値より大きい第2の値である第2の条件でエッチングを行うことにより、第1のコンタクトホールにより第2の応力膜44を貫き、第2のコンタクトホールにより第2の絶縁膜及び第1の絶縁膜40を貫くエッチング工程と、更なるエッチングを行い、第1のコンタクトホールをゲート配線20まで到達させ、第2のコンタクトホールをトランジスタのソース/ドレインまで到達させる第3のエッチング工程とを有している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】SiGe等の半導体膜が形成された領域と、酸化シリコン膜から成るゲート絶縁膜が形成された領域とが同一基板上に形成される際に、ゲート絶縁膜を精度良く形成する。

【解決手段】基板10を熱酸化することにより、第1素子領域101及び第2素子領域201に、第1ゲート絶縁膜110及び第2ゲート絶縁膜210を形成し、かつ第3素子領域301及び第4素子領域401それぞれに位置する基板10に熱酸化膜を形成する。次いで、第4素子領域401に位置する熱酸化膜を除去する。次いで、第4素子領域401に位置する基板10上に半導体膜414を成膜する。次いで、第3素子領域301に位置する熱酸化膜を除去する。次いで、第4素子領域401に位置する半導体膜414上、及び第3素子領域301に位置する基板10上に第3ゲート絶縁膜310及び第4ゲート絶縁膜410を形成する。

(もっと読む)

半導体集積回路装置

【課題】近年のCMOS型LSIの設計においてはリーク電力の削減が非常に大きな課題となっている。リーク電力を削減する手段としてはトランジスタの閾値電圧を複数使用し、速度の必要な場所には閾値電圧の低いトランジスタを、不要な場所には閾値電圧の高いトランジスタを使用する方法が広く用いられている。しかしながら先端プロセスほど閾値電圧制御だけではリーク電力が十分に抑制できず、様々なリーク電力削減手法が必要となってきている。

【解決手段】本願の一つの発明は、CMOSまたはCMIS型LSIにおいて、一部の論理ゲートを構成するPチャネルFETおよびNチャネルFETの両側のゲート電極形状を近接効果を利用して平面的に湾曲させることによって、実効的なゲート長を長くするものである。

(もっと読む)

シリコン層の形成方法、半導体装置の製造方法

【課題】シリコン層表面の溶解を防止しつつ、エピタキシャル成長により形成された凝集性異物を除去する。清浄な表面を有し、膜厚が均一なシリコン層を形成する。

【解決手段】シリコン基板上にエピタキシャル成長によりシリコン層を形成した後に、シリコン層の表面を酸化する。このシリコン層の表面を洗浄して、エピタキシャル成長時にシリコン層の表面に発生した異物を除去する。

(もっと読む)

161 - 180 / 2,910

[ Back to top ]