Fターム[4M104GG10]の内容

Fターム[4M104GG10]に分類される特許

141 - 160 / 2,910

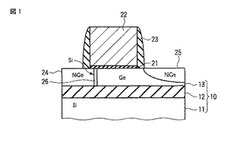

半導体装置及びその製造方法

【課題】トンネルFETの閾値ばらつきの抑制をはかる。

【解決手段】Si1-x Gex (0<x≦1)の第1の半導体層13上にゲート絶縁膜21を介して形成されたゲート電極22と、Geを主成分とする第2の半導体と金属との化合物で形成されたソース電極24と、第1の半導体と金属との化合物で形成されたドレイン電極25と、ソース電極24と第1の半導体層13との間に形成されたSi薄膜26とを具備した半導体装置であって、ゲート電極22に対しソース電極24のゲート側端部とドレイン電極25のゲート側端部とは非対称の位置関係にあり、ドレイン電極25のゲート側の端部の方がソース電極24のゲート側の端部よりも、ゲート電極22の端部からゲート外側方向に遠く離れている。

(もっと読む)

半導体装置

【課題】シリサイドプロセス前にイオン注入を行う半導体装置であって、より確実にMISFETにおけるリーク電流の抑制が図れるものを実現する。

【解決手段】マスク層RMによりPチャネル型MISFETを覆いつつ、Nチャネル型MISFETのN型ソース領域およびN型ドレイン領域に、イオン(F,Si,C,Ge,Ne,Ar,Krのうち少なくとも一種類を含む)を注入する。その後、Nチャネル型MISFETおよびPチャネル型MISFETの各ゲート電極、ソース領域およびドレイン領域にシリサイド化(Ni,Ti,Co,Pd,Pt,Erのうち少なくとも一種類を含む)を行う。これにより、Pチャネル型MISFETにおいてドレイン−ボディ間オフリーク電流を劣化させること無く、Nチャネル型MISFETにおいてドレイン−ボディ間オフリーク電流(基板リーク電流)の抑制が図れる。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化されたMISFETのゲート電極の加工精度を向上することができる技術を提供する。

【解決手段】シリコン上にニッケルプラチナ合金膜を形成する(S101)。そして、第1加熱処理を実施する(S102)。このとき、第1加熱処理において、加熱温度は250℃〜270℃であり、加熱時間は30秒未満である。続いて、未反応のニッケルプラチナ合金膜を除去する(S103)。その後、第2加熱処理を実施する(S104)。このとき、第2加熱処理において、加熱温度は、450℃〜600℃である。

(もっと読む)

半導体装置

【課題】メタルゲート電極内に基板面に対して平行な金属とシリコンなどとの境界又はシリサイドとシリコンなどとの境界を含むメタルゲート電極において、トランジスタの接続抵抗が小さく、高速動作時のトランジスタの遅延又はトランジスタ特性のばらつきなどの特性劣化の懸念がなく、且つ、低コストな構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に、ゲート絶縁膜105と、pMIS用金属材料109又はnMIS用金属材料111と、ゲート電極材料112と、ゲート側壁メタル層122とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリ混載ロジックデバイスのRAM領域の閾値電圧のばらつきを低減する。

【解決手段】本発明の半導体装置は、ロジック領域101と、RAM領域102とが設けられたシリコン基板1と、ロジック領域101に形成されたNMOSトランジスタ20と、RAM領域102に形成されたNMOSトランジスタ40と、を備える。NMOSトランジスタ20、40は、ゲート絶縁膜5とメタルゲート電極6との順でシリコン基板1上に積層された積層構造を有する。NMOSトランジスタ20は、シリコン基板1とメタルゲート電極6との間に、構成元素として、ランタン、イッテルビウム、マグネシウム、ストロンチウム及びエルビウムからなる群から選択される元素を含む、キャップメタル4を有する。NMOSトランジスタ40には、キャップメタル4が形成されていない。

(もっと読む)

有機半導体デバイスの製造方法および薄膜トランジスタの製造方法

【課題】有機半導体層の上で導電層を迅速かつ容易にパターニングすると共に安定な性能を得ることが可能な薄膜トランジスタの製造方法を提供する。

【解決手段】有機半導体層4の上に、開口部5A,5Bを有する絶縁性保護層5を形成したのち、その絶縁性保護層5(開口部5A,5Bを含む)を覆うように、電極層6を形成する。こののち、絶縁性保護層5の形成領域(開口部5A,5Bを除く)における電極層6にレーザLを照射し、その電極層6をレーザアブレーションにより選択的に除去してソース電極およびドレイン電極を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】マイクロローディング効果を防止しながら、上層配線となる金属配線のレイアウト制約のない構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3の上に形成されたゲート電極4と、半導体基板1に形成された拡散層5と、半導体基板1の上に形成された絶縁膜7及び絶縁膜8と、絶縁膜及び絶縁膜8を貫通するホール9Dに埋め込まれ、側面を絶縁膜11で覆われた金属材料からなるプラグ12と、絶縁膜8を貫通しないホール10Bに埋め込まれ、絶縁膜11からなる絶縁体10Cと、絶縁膜8の上に形成され、プラグ12と電気的に接続する金属配線13Bとを備えている。

(もっと読む)

電界効果型トランジスタ

【課題】従来の電界効果型トランジスタでは、ソース領域およびドレイン領域に形成する高濃度不純物のイオン注入工程により半導体基板表面がアモルファス化されるため、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、活性化熱処理により結晶欠陥を誘発し、電界効果型トランジスタの信頼性を低下させる問題があった。

【解決手段】本発明の電界効果型トランジスタは、ソース領域およびドレイン領域を構成する部分の上部に高濃度不純物を含有する導電性膜を設ける。高濃度不純物のイオン注入を行う必要がないことから、この領域の半導体基板表面がアモルファス化することがない。これにより、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、再結晶化による結晶欠陥の発生を防ぐことができる。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】 微結晶Si薄膜トランジスタの光リーク電流を抑制し、液晶ディスプレイ等の光照射下で使用する場合に、クロストークやコントラストの低下等の表示特性の劣化を低減する。

【解決手段】 基板上に設けられたゲート電極と、ゲート電極を被覆するように設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられ、微結晶Si層と非晶質Si層とを含むチャネル層と、チャネル層上の一方に設けられたソース電極と、チャネル層上の他方に設けられたドレイン電極とを備えた薄膜トランジスタに関する。そして、この実施形態において、ソース電極およびドレイン電極の夫々は、第1の層と、前記第1の層よりも下側に設けられた第2の層とを含み、前記第2の層は第1の層よりも反射率が低い導電膜の層で構成される。

(もっと読む)

表示装置

【課題】TFTと接続するソース電極あるいはドレイン電極のスルーホールにおけるコンタクト抵抗を減少させ、表示装置の動作効率を向上させる。

【解決手段】スルーホールにおいて、TFTのソース部とソース電極8が接続している。ソース電極8は、バリヤメタル、Al合金82、キャップメタル83の3層から形成されている。バリヤメタルは半導体層と接触する下層81aとAl合金と接触する上層81bとに分かれている。バリヤメタルの下層81aをスパッタリングして形成した後、熱処理し、その後、ベースメタルの上層81b、Al合金82、キャップメタル83を連続してスパッタリングによって形成する。Al合金82と接触するバリヤメタルの上層81bは酸化されていないので、スルーホールにおけるコンタクト抵抗の上昇を防止することが出来る。

(もっと読む)

半導体装置およびその製造方法

【課題】適切な仕事関数を有する金属ゲート電極を備え、トランジスタ特性のばらつきが抑えられた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1001と、半導体基板1001内に形成された第1導電型の第1の活性領域1003と、第1の活性領域1003上に形成された第1のゲート絶縁膜1030aと第1のゲート電極1032aとを有し、第1の活性領域1003上に形成された第1チャネル型の第1のMISFET1050とを備える。第1のゲート電極1032aは、第1のゲート絶縁膜1030a上に形成され、金属原子を含む第1の下部ゲート電極1011aと、炭素の単体を含む材料、または分子中に炭素を含む材料からなる第1の酸化防止膜1012aと、第1の上部ゲート電極1013aとを有している。

(もっと読む)

薄膜トランジスタ基板および表示デバイス

【課題】Cu系合金配線膜を半導体層と直接接続しても接触抵抗率が低く、かつ密着性に優れた薄膜トランジスタ基板を提供する。

【解決手段】薄膜トランジスタの半導体層33と、Cu合金層28b、29bとを有する薄膜トランジスタ基板において、前記半導体層33と前記Cu合金層28b、29bとの間に、酸素含有層28a、29aを含んでおり、前記酸素含有層28a、29aを構成する酸素の一部若しくは全部は、前記薄膜トランジスタの前記半導体層33のSiと結合しており、前記Cu合金層28b、29bは、合金元素としてX(Xは、Mn、Ni、Zn、およびMgよりなる群から選ばれる少なくとも1種)を合計で2原子%以上20原子%以下含有し、前記Cu合金層28b、29bは、前記酸素含有層28a、29aを介して前記薄膜トランジスタの前記半導体層33と接続していることを特徴とする薄膜トランジスタ基板である。

(もっと読む)

半導体装置、設計装置、及びプログラム

【課題】リングゲート型MOSトランジスタ間の領域だけでなく、リング内の領域においてもディッシング現象の発生を抑止する。

【解決手段】半導体装置1は、基板10と、基板10上に形成されたリング形状のゲート電極21を有するトランジスタ20bと、ゲート電極21の外側に配置され、ゲート電極21と同層に設けられる複数の外部ダミーパターン40と、ゲート電極21の内側に配置され、ゲート電極21と同層に設けられる少なくとも1つの内部ダミーパターン41とを備える。

(もっと読む)

コンタクトプラグ、配線、半導体装置およびコンタクトプラグ形成方法

【課題】金属シリサイド膜と銅コンタクトプラグ本体との間の拡散バリア層として、薄膜の酸化マンガンで構成された拡散バリア層を用いてはいるものの、金属シリサイド膜への銅原子の拡散、侵入を確実に抑止することができるようにする。

【解決手段】本発明のコンタクトプラグ10は、半導体装置の絶縁膜4に設けられたコンタクトホール5に形成され、コンタクトホール5の底部に形成された金属シリサイド膜3と、コンタクトホール5内で金属シリサイド膜3上に形成され、非晶質でシリコンを含む第1の酸化マンガン膜6aと、その第1の酸化マンガン膜6a上に形成され、微結晶を含む非晶質の第2の酸化マンガン膜6bと、その第2の酸化マンガン膜6b上に、コンタクトホール5を埋め込むように形成された銅プラグ層7と、を備えることを特徴としている。

(もっと読む)

トランジスタ及びその製造方法

【課題】Siチヤネルを有するNMOSとSiGeチャネルを有するPMOSで、NMOSには引張り歪みを与える、PMOSには、表面のダングリングボンドを減少させることができる半導体装置を提供する。

【解決手段】単結晶シリコン基板50の一部領域にシリコンゲルマニウムチャネル膜54aを形成し、PMOSトランジスタを、シリコン膜60aを形成し、NMOSトランジスタを形成する。単結晶シリコン基板、シリコンゲルマニウムチャネル膜、PMOSトランジスタ、NMOSトランジスタの表面上に、反応ガス、雰囲気ガス及び水素ガスを含む蒸着ガスを用いて、シリコン窒化膜82を形成し、PMOSトランジスタは、シリコンゲルマニウムチャネル膜表面のダングリングボンドの除去により、ホールスキャタリングが抑制され、NMOSトランジスタには引張り歪みを与えることにより動作特性の改善ができる。

(もっと読む)

窒化物半導体を用いた半導体装置およびその製造方法

【課題】ソース領域およびドレイン領域とゲート電極との位置制御性を向上させ、製造バラツキを低減する。

【解決手段】窒化物半導体を用いた半導体装置10は、窒化物半導体層2に所定間隔を隔てて形成されたソース領域3およびドレイン領域4の間のチャネル領域上に形成され、少なくとも一部がシリサイド合金から形成されたゲート電極6を備え、ソース領域3上にあるゲート電極6の端からゲート電極6と上下に重なるソース領域3の端までの距離L1と、ドレイン領域4上にあるゲート電極6の端からゲート電極6と上下に重なるドレイン領域4の端までの距離L2と、が等しい。

(もっと読む)

表示装置およびその製造方法

【課題】ゲート絶縁層内に拡散する汚染元素によってトランジスタ特性が低下するのを防止した薄膜トランジスタを有する表示装置、および、その製造方法を提供することを目的とする。

【解決手段】基板101の上側に積層された半導体層104と、半導体層104の上側に積層されるゲート電極106と半導体層104とゲート電極106との間に積層されるゲート絶縁層105と、ソース電極112およびドレイン電極111と、を含む薄膜トランジスタを有する表示装置であって、ソース電極112およびドレイン電極111の少なくとも一方は、ゲート絶縁層105の上側に形成されて、ゲート絶縁層105に形成されるコンタクトホール109を介して半導体層に接続され、コンタクトホール109の側壁には、窒素化合物を含む側壁膜110が形成される、ことを特徴とする表示装置。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率ゲート絶縁膜、及び、ゲート電極としてメタル膜を含む半導体装置において、逆短チャネル効果の発生を防止して高性能化を実現する。

【課題手段】半導体装置は、半導体基板101の上に形成されたランタンを含有する高誘電率ゲート絶縁膜102と、高誘電率ゲート絶縁膜102の上に形成されたキャップ膜103と、キャップ膜103の上に形成されたメタル膜104と、メタル膜104の上に形成されたポリシリコン膜105と、高誘電率ゲート絶縁膜102、キャップ膜103、メタル膜104、及びポリシリコン膜105それぞれの両側面に形成されたランタンを含有するゲート側壁絶縁膜106とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のMISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、第1,第2のMISトランジスタTr1,Tr2を備えている。第1,第2のMISトランジスタは、第1,第2の活性領域10a,10b上に形成され、第1,第2の高誘電率膜13a,13bを有する第1,第2のゲート絶縁膜13A,14Bと、第1,第2のゲート絶縁膜上に形成された第1,第2のゲート電極18A,18Bとを備えている。第1のゲート絶縁膜13Aと第2のゲート絶縁膜14Bとは、第1の素子分離領域11L上において分離されている。第1の素子分離領域11Lを挟んで対向する第1の活性領域10aの一端と第2の活性領域10bの一端との距離をsとし、第1の活性領域10aの一端から第1の素子分離領域11L上に位置する第1のゲート絶縁膜13Aの一端までの突き出し量をd1としたとき、d1<0.5sの関係式が成り立っている。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減と、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】凹部4c内に形成されたi型(イントリンシック半導体)側壁層5を介してp+型ゲート領域6を形成する。このような構成とすれば、n+型層4とp+型ゲート領域6との間にさらにp+型ゲート領域6よりも低濃度のp-型層が必要とされない。このため、n-型チャネル層3に直接接触している高濃度のp+型ゲート領域6によって、n-型チャネル層3内に伸びる空乏層幅を制御できる。したがって、n+型層4とp+型ゲート領域6との間にさらにp-型層が備えられる場合と比較して、ゲート印加電圧が高電圧になることを抑制できる。また、p+型ゲート領域6の側面がi型側壁層5によってn+型層4と分離されるため、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスを低減できる。

(もっと読む)

141 - 160 / 2,910

[ Back to top ]