Fターム[4M104HH15]の内容

Fターム[4M104HH15]に分類される特許

161 - 180 / 948

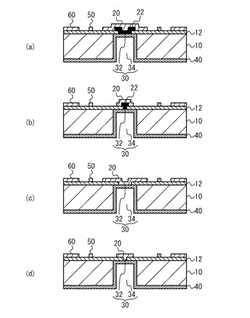

半導体装置及び製造方法

【課題】 ビアホール上にオーミック電極が形成された半導体装置において、装置の小型化を図ること。

【解決手段】 本半導体装置は、基板10と、基板10上に形成された半導体層12と、半導体層上12に形成されたソースまたはドレイン電極を構成するオーミック電極20と、を備え、基板10及び半導体層12には、基板10及び半導体層12を貫通するビアホール30が形成され、ビアホール30は、少なくとも半導体層を貫通する第1ビアホール32と、第1ビアホール32下の基板10に形成された、第1ビアホール32より開口断面積が大きい第2ビアホール34と、を含み、オーミック電極20は、第1ビアホール32の上に設けられている。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】n型及びp型の少なくともいずれかの不純物が添加された不純物領域を有する半導体膜と、配線とを有し、配線は、導電性を有する金属酸化物を含む拡散防止膜と、該拡散防止膜上の低抵抗導電膜とを有し、配線と半導体膜とのコンタクト部において、拡散防止膜と不純物領域とが接する。拡散防止膜は、導電膜を酸化性ガス及びハロゲン系ガスの混合ガスから生成されるプラズマに暴露して該導電膜に含まれる金属材料の酸化物を形成し、金属材料の酸化物が形成された導電膜を、水を含む雰囲気に暴露して導電膜を流動化させ、流動化した導電膜を固化することで形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】素子面積の増大を抑制しつつ、信頼性に優れた構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置100は、化合物半導体基板12と、化合物半導体基板12に埋め込まれた埋込電極と、を備え、化合物半導体基板12の主面に溝22、24が設けられており、少なくとも溝22、24の側壁上に設けられた第一の金属膜10a、10bと、少なくとも溝22、24の底面上に設けられており、第一の金属膜10a、10bと異種材料で構成される第二の金属膜9a、9bと、を含む積層体により溝22、24を埋め込むことで、上記埋込電極が構成されており、第一の金属膜10a、10bのフェルミエネルギーは化合物半導体基板12の真性フェルミエネルギーと異なり、第二の金属膜9a、9bのフェルミエネルギーは化合物半導体基板12の真性フェルミエネルギーと異なる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置において、電界効果移動度が大きい酸化物半導体層を用いた半導体装置の作製方法を提供することを課題の一つとする。また、高速動作可能な半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化物半導体層をハロゲン元素により終端化させて、酸化物半導体層と、酸化物半導体層と接する導電層のコンタクト抵抗の増大を抑制することで、酸化物半導体層と導電層のコンタクト抵抗が良好になり、電界効果移動度が高いトランジスタを作製することができる。

(もっと読む)

シリコンデバイス構造、及びその形成に用いるスパッタリングターゲット材

【課題】シリコンデバイスの飽和移動度特性を向上する。

【解決手段】シリコン半導体膜上に、Pドープn+型アモルファスシリコン膜と、該Pドープn+型アモルファスシリコン膜上に形成された配線とを有するシリコンデバイス構造において、前記配線が、前記Pドープn+型アモルファスシリコン膜の表面に形成されたシリコン酸化膜と、銅合金膜とからなり、前記銅合金膜は、1原子%以上5原子%以下のMn及び0.05原子%以上1.0原子%以下のPを含む銅合金をスパッタリングにより形成した膜である。

(もっと読む)

炭化珪素半導体装置

【課題】微細化してもソース領域およびベース領域に繋がるコンタクト領域とソース電極とのコンタクトが十分に取れるようにする。

【解決手段】コンタクトホール12aの長手方向、つまりソース電極11とn+型ソース領域4およびp+型ボディ層5とのコンタクト領域の長手方向とn+型ソース領域4およびp+型ボディ層5の長手方向も直交させる。これにより、n+型ソース領域4やp+型ボディ層5それぞれのソース電極11へのコンタクト幅をコンタクトホール12aの幅分とすることが可能となる。このため、コンタクトを広く取ることが可能となる。これにより、素子を微細化してもn+型ソース領域4やp型ベース領域3に繋がるp+型ボディ層5とソース電極11とのコンタクトが十分に取れるようにすることが可能となる。

(もっと読む)

窒化物半導体装置

【課題】活性層の上に電極パッドを形成する場合に生じる問題を解決し、オン抵抗の上昇を抑えた窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、活性領域102Aを有する窒化物半導体層積層体102と、活性領域の上に互いに間隔をおいて形成されたフィンガー状の第1の電極131及び第2の電極132とを備えている。第1の電極の上に接して第1の電極配線151が形成され、第2の電極の上に第2の電極配線152が接して形成されている。第1の電極配線及び第2の電極配線を覆うように第2の絶縁膜が形成され、第2の絶縁膜の上に第1の金属層161が形成されている。第1の金属層は、第2の絶縁膜を介して活性領域の上に形成され、第1の電極配線と接続されている。

(もっと読む)

半導体装置の製造方法

【課題】コンタクト抵抗率を低く抑えることが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、Al組成比が0.2以上のAlGaN層をエッチングして、RMS粗さが0.3nm未満の底面を有する凹部を形成する工程と、前記凹部の底面に接して、4nmから8nmの厚さの第1Ta層を形成する工程と、前記第1Ta層に熱処理を施して、前記AlGaN層にオーミック接触させる工程と、を有する半導体装置の製造方法である。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】半導体層とソース電極、ドレイン電極とのコンタクト抵抗が小さい電界効果トランジスタを提供すること。

【解決手段】SiC基板11の表面上に形成された、活性層を含む半導体層12と、半導体層12上に互いに離間して形成され、チタン層18、およびこのチタン層18に対する膜厚比が12〜15であるアルミニウム層19を有するソース電極16およびドレイン電極15と、半導体層12上のうち、ソース電極16とドレイン電極15との間に形成されたゲート電極17と、を具備する電界効果トランジスタ。

(もっと読む)

電界効果トランジスタ

【課題】オン抵抗の低減を図ることができる電界効果トランジスタ(FET)を提供する。

【解決手段】FET101は、化合物半導体基板1と、化合物半導体基板1上に形成され、当該基板側から見て、n型キャリアが蓄積するチャネル層5、ショットキー層8、及びキャップ層9を順次含む半導体積層構造10と、ゲート電極20、ソース電極21、及びドレイン電極22とを備えている。キャップ層9は、ショットキー層8側から見て、自然超格子構造を有するアンドープの又はn型キャリアが添加された第1のInGaP層9Aと、自然超格子構造を有しないn型キャリアが添加された第2のInGaP層9Bとを順次含んでいる。

(もっと読む)

半導体装置、光学装置及びセンサ装置

【課題】ソース電極及びドレイン電極と有機半導体材料層との間の接触抵抗を低下させることができ、これを簡便な製造プロセスで実現できる半導体装置、光学装置及びセンサ装置を提供すること。

【解決手段】ソース電極5と、ドレイン電極6と、少なくともこれらの電極間に設けられた有機半導体材料層7とを有し、有機半導体材料層7を介してソース電極5とドレイン電極6との間で電荷を移動させるように構成された有機電界効果トランジスタにおいて、ソース電極5及びドレイン電極6が、導電性高分子材料と電荷移動錯体との混合物からなる、有機電界効果トランジスタ1a。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】不純物ドープを用いることなく、低温プロセスでオーミック電極を形成することができる半導体装置の製造方法を提供する。

【解決手段】n+型基板1の表面側に素子構造や表面電極を形成した後、n+型基板1の裏面1bにアモルファス層12を形成する。そして、アモルファス層12が形成された裏面1b上に金属薄膜110を形成した後、n+型基板1の裏面1b側に光子エネルギーとレーザ出力の積が1000eV・mJ/cm2以上かつ8000eV・mJ/cm2以下となるような条件でレーザ光を照射することでシリサイド層111を含むドレイン電極11を形成する。これにより、n+型基板1に高温処理を行うことなく、n+型基板1にドレイン電極11にシリサイド層111を生成できる。したがって、不純物ドープ層を用いることなく、かつ低温プロセスによってドレイン電極11をオーミック電極にできる。

(もっと読む)

半導体装置

【課題】 表面保護膜中へのホットキャリアの侵入に起因する半導体装置の出力低下を抑制すること。

【解決手段】 本半導体装置100は、窒化ガリウム系半導体からなる電子走行層12と、電子走行層12上に設けられ、窒化ガリウム系半導体からなる電子供給層16と、電子供給層16上に設けられ、窒化ガリウムからなるキャップ層18と、キャップ層18上に設けられたゲート電極24と、電子供給層16上にゲート電極24を挟んで設けられたソース電極20及びドレイン電極22と、キャップ層18上に設けられた表面保護膜30と、キャップ層18と表面保護膜30との間に介在し、少なくともゲート電極24とドレイン電極22との間の領域に設けられたAlxGa1−xN(0.5≦x≦1)からなるバリア層50と、を備える。

(もっと読む)

ドナー元素拡散機能を有する電極形成用ペースト組成物、太陽電池セル、及び太陽電池セルの製造方法

【課題】半導体基板上に不要なn型拡散層を形成させることなく、特定の部分にn型拡散層を形成することが可能で、選択的なn型拡散層形成のためのプロセスを新たに設けることなく、電極を形成する際の熱処理時に、n型拡散層を形成することが可能な電極形成用ペースト組成物、および、該電極形成用ペースト組成物を用いて形成されたn型拡散層及び電極を有する太陽電池を提供する。

【解決手段】n型拡散層形成機能を付与した電極形成用ペースト組成物を、金属粒子と、ドナー元素を含むガラス粒子と、樹脂と、溶剤と、を含んで構成する。また、該電極形成用ペースト組成物を用いて形成した選択的なドナー元素拡散領域131A及び電極133を有する太陽電池セルである。

(もっと読む)

半導体素子及び該半導体素子を備える半導体素子構造

【課題】本発明は、かかる事情に鑑み、トランジスタの遮断状態を自然に実現し、半導体領域に金属領域との界面近傍の空乏層の形成を抑制しつつ、ショットキー障壁を実質的に下げることができるようにソース領域のフェルミ準位を選択することにより、駆動電流を増加させる半導体素子及び該半導体素子を備える半導体素子構造を提供することを課題とする。

【解決手段】ソース領域6及びドレイン領域7は、フェルミ準位が異なる第1金属領域10及び第2金属領域11を有し、第1金属領域10は、半導体領域5の価電子帯の頂上のエネルギーレベル以上で且つ半導体領域5の真性フェルミ準位以下のフェルミ準位を有する金属であり、第2金属領域11は、第1金属領域10のフェルミ準位以上で且つ伝導帯の底のエネルギーレベル以下のフェルミ準位を有する金属であることを特徴とする。

(もっと読む)

薄膜トランジスタとその製造方法、及びアクティブマトリックス基板

【課題】電極/配線の材料としてAl及び/又はその合金が用いられており、オフリーク電流が小さく良好な素子特性を有する薄膜トランジスタ(TFT)を提供する。

【解決手段】TFT101は、基板1上にゲート電極2とゲート絶縁膜3とチャネル層として機能する半導体膜4とを備え、半導体膜4上にソース電極6とドレイン電極7とが互いに離間して設けられたものであり、ソース電極6及びドレイン電極7は、アルミニウム及び/又はその合金を主成分とする少なくとも1層のアルミニウム(合金)膜を含む単層膜又は積層膜からなり、半導体膜4の表面のソース電極6及びドレイン電極7の間の領域8に、電気的に不活性な少なくとも1種のアルミニウム化合物9が形成されたものである。

(もっと読む)

III族窒化物半導体電子デバイス、III族窒化物半導体電子デバイスを作製する方法

【課題】Id―max特性低下を低減可能なIII族窒化物半導体電子デバイスが提供される。

【解決手段】III族窒化物半導体電子デバイス11では、チャネル層21はAlGaNからなると共に、バリア層23はチャネル層21より大きなバンドギャップのAlGaNからなる。チャネル層21が、GaNではなく、AlGaNからなるので、III族窒化物半導体電子デバイス11においてId―max特性低下を低減可能である。また、第1及び第2の電極17、19は、それぞれ、チャネル層21の第1及び第2の部分21a、21b上に設けられる。チャネル層21において第1の部分21aの不純物濃度が第2の部分21bの不純物濃度と同じであるから、チャネル層21における第1の部分にイオン注入が行われていない。半導体積層15に部分的にイオン注入を行っていない。このイオン注入の使用回避により、Id―max特性低下を更に低減可能である。

(もっと読む)

導電性薄膜の形成方法及び導電性薄膜形成装置

【課題】スパッタ成膜において、あらゆる膜特性を同時に満足させる手法を提供すること。

【解決手段】スパッタ現象を利用して基板上に導電性薄膜を形成する方法であって、薄膜形成中に、スパッタ電力、スパッタガス、および反応性ガスを含む成膜パラメータの少なくとも1つを2つの値に変動させ、その時間分割比を制御することを特徴とする導電性薄膜の形成方法である。また、p型またはn型の導電型を有する半導体上に導電性薄膜を形成する方法において、半導体上への成膜開始時点に、強度にプラズマ照射を行うことを特徴とする導電性薄膜の形成方法も採用できる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において低抵抗なオーミック性を有し、酸・アルカリによる腐食に対し高い耐性を持つ電極を得ることを目的とする。

【解決手段】本発明に係る第1の半導体装置は、窒化物半導体層1と、窒化物半導体層上に設けられた電極とを備え、窒化物半導体層1は電極下に、それ以外の部分よりも高濃度にn型不純物を含む高濃度不純物領域2を備え、電極は、窒化物半導体層1上に設けられた第一金属層3と、第一金属層3上に設けられた第二金属層4と、第二金属層4上に設けられた第三金属層5と、を備え、第一金属層3は第二金属層4よりも窒化物半導体層1との高い密着性を有する金属を含み、第三金属層5は水素よりもイオン化傾向の小さい金属を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のコンタクトプラグのゲート電極への短絡を防止する。第1の不純物拡散層と第1のコンタクトプラグの接続抵抗、及び第1と第2のコンタクトプラグの接続抵抗を低減することにより、縦型MOSトランジスタのオン電流を増加させる。

【解決手段】シリコンピラー上部に、非晶質シリコン層及び単結晶シリコン層を形成する。次に、2度の選択エピタキシャル成長法により、シリコンピラー上に順に非晶質シリコン層、及び非晶質シリコンゲルマニウム層を形成する。この後、熱処理により、シリコンピラー上部に単結晶シリコン層を有する第1の不純物拡散層を形成すると同時に、シリコンピラー上に単結晶シリコン層及び多結晶シリコンゲルマニウム層を有する第1のコンタクトプラグを形成する。次に、第1のコンタクトプラグに接続されるように、金属から構成される第2のコンタクトプラグを形成する。

(もっと読む)

161 - 180 / 948

[ Back to top ]