Fターム[4M104HH15]の内容

Fターム[4M104HH15]に分類される特許

121 - 140 / 948

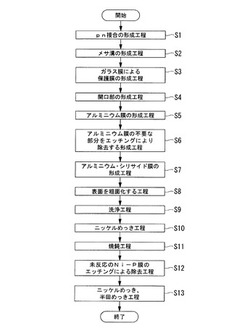

半導体装置の製造方法、および、半導体装置

【課題】ニッケルめっき電極を備え、低VFを兼ね備えた半導体装置の製造方法、および、半導体装置を提供することを目的としている。

【解決手段】n型半導体基板の一方の表面近傍に、小電流領域の電圧降下を得るべく濃度設定されたp型の半導体層を形成してpn接合を形成する工程と、p型の半導体層表面に、鉛を含有するガラスパッシベーション膜を形成し、形成したガラスパッシベーション膜の一部を除去して開口部を形成する工程と、開口部を形成した後、p型の半導体層表面に、アルミニウムの膜を形成する工程と、アルミニウムとp型の半導体層のシリコンを、熱処理により反応させてアルミニウム・シリサイド膜を生成する工程と、アルミニウム・シリサイド膜上部に存在するシリコンと未反応のアルミニウムを、エッチングにより除去して表面を粗面化する工程と、粗面化されたアルミニウム・シリサイド膜の上にニッケル電極を形成する工程とを備える。

(もっと読む)

半導体装置

【課題】電流コラプスの発生を抑制できるIII族窒化物半導体トランジスタおよびその製造方法を提供する。

【解決手段】FET1では、第1窒化物半導体層103の上に第2窒化物半導体層104が設けられ、少なくとも一部が第2窒化物半導体層104に接するようにソース電極106およびドレイン電極107が設けられている。第2窒化物半導体層104の上面においてソース電極106とドレイン電極107との間に位置するように凹部110aが形成されており、ゲート電極108が凹部110aの開口を覆うように凹部110aの上方に設けられている。

(もっと読む)

半導体装置及びその作製方法

【課題】ノーマリーオフのトランジスタ、或いは当該トランジスタを含んで構成される回路を有する半導体装置を提供する。

【解決手段】チャネル形成領域として機能する第1の酸化物半導体層と、当該第1の酸化物半導体層と重なるソース電極層及びドレイン電極層と、当該第1の酸化物半導体層、当該ソース電極層、及び当該ドレイン電極層と接するゲート絶縁層と、当該ゲート絶縁層に接して当該第1の酸化物半導体層と重なる第2の酸化物半導体層と、当該第2の酸化物半導体層上に設けられたゲート電極層とを有する半導体装置及びその作製に関する。

(もっと読む)

n型ゲルマニウム上への低抵抗コンタクトの作製方法

【課題】n型Ge上に形成されるコンタクトの接触抵抗を低減する。

【解決手段】第1ドーパントレベルのn型ドーパントがドープされたゲルマニウム領域(10)を上部に有する半導体基板を得る工程と、n型ドープされたゲルマニウム領域(10)を覆う界面シリコン層(11)を形成する工程であって、界面シリコン層(11)は第2ドーピングレベルのn型ドーパントでドープされて臨界膜厚より大きな膜厚を有し、これにより界面シリコン層(11)は少なくとも部分的に緩和される工程と、界面シリコン層(11)を覆うように、1×10−2Ωcmより小さい電気抵抗率を有する材料の層(12、13)を形成する工程とを含む方法。本発明はまた、対応する半導体デバイスを提供する。

(もっと読む)

ラジカルクリーニング方法及びラジカルクリーニング装置

【課題】Si基板上に形成されたSiO2膜を除去するラジカルクリーニング方法であって、ラジカルクリーニングを行う際に生成する残留生成物も除去することができるラジカルクリーニング方法を提供する。

【解決手段】プラズマによりHラジカル生成用ガスを分解してHラジカルを生成させ、このHラジカルとNF3ガスを反応させてN、F及びHからなるラジカルを生成するNFHラジカル生成工程と、真空槽内で、Si基板上に形成されたSiO2膜に前記N、F及びHからなるラジカルを照射することにより前記SiO2膜を除去するエッチング工程と、真空槽内で、前記エッチング工程で前記Si基板上に生成した残留生成物にマイクロ波を照射することにより、前記残留生成物を加熱して蒸発させて除去する残留生成物除去工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されたN+型ソース層とソース電極のコンタクト抵抗が低減されたパワーMOSトランジスタの実現を図る。

【解決手段】N型ドリフト層2の表面にP型ボディ層6を形成し、該P型ボディ層6の表面にN+型ソース層7を形成する。N+型ソース層7上を被覆する層間絶縁膜8に第1のコンタクトホール9を形成し、N+型ソース層7の一部を露出する。第1のコンタクトホール9の底面に露出したN+型ソース層7の表面からP型ボディ層6内まで第2のコンタクトホール10を形成する。第2のコンタクトホール10の底面に露出したP型ボディ層6の表面にP+型コンタクト層11を形成する。第1のコンタクトホール9の底面にフォトリソグラフィ工程のマスク合わせ精度のばらつき幅より小さい幅のN+型層7aを形成し、第1、第2のコンタクトホール9、10内をタングステン層12等で埋設する。

(もっと読む)

薄膜トランジスタ表示板の製造方法

【課題】半導体層の側壁がデータ線の側壁に対して突出することを最小化する。

【解決手段】ゲート絶縁膜140上に第1、第2非晶質シリコン層150,160、データ金属層170形成段階と、上部データ金属層170r上に第1感光膜パターン50形成段階と、第1感光膜パターンをマスクとしてデータ金属層170をエッチングして、第1下部データ金属パターン及び側壁が突出した突出部を含む第1上部データ金属パターン形成段階と、第1感光膜パターンをマスクとして第1及び第2非晶質シリコン層をエッチングして、非晶質シリコン層パターン形成段階と、第2感光膜パターンをマスクとして第1上部データ金属パターンをエッチングして、第2上部データ金属パターン形成段階と、第2感光膜パターンをマスクとして第1下部データ金属パターン、非晶質シリコン層パターンをエッチングして、半導体、データ線等を形成する段階、とを含む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】基板表面にシリサイド膜が形成された半導体装置において、ゲート電極パターンの粗密に関わらず、コンタクトの深さの差を緩和する。

【解決手段】半導体装置100は、活性領域(104)に、表面にシリコン酸化膜122aが選択的に形成されたシリサイド膜120aを形成する工程と、その上に、シリコン酸化膜120aとの間でエッチング選択比を有するライナー絶縁膜124を形成する工程と、その上に、ライナー絶縁膜124との間でエッチング選択比を有する絶縁膜(126)を形成する工程と、絶縁膜(126)、ライナー絶縁膜124、およびシリコン酸化膜122aを貫通してシリサイド膜120aに達する第1のコンタクトホール144を形成する工程と、により製造される。

(もっと読む)

成膜装置

【課題】 埋め込み工程におけるスループットを向上でき、埋め込み工程が多用される半導体集積回路装置であっても、優れた生産能力を発揮することが可能な成膜装置を提供すること。

【解決手段】 アミノシラン系ガスを供給する供給機構122、及びアミノ基を含まないシラン系ガスを供給する供給機構121を備え、アミノシラン系ガスを供給して前記導電体に達する開孔を有した絶縁膜の表面、及び前記開孔の底の表面にシード層を形成する処理、及びアミノ基を含まないシラン系ガスを供給してシード層上にシリコン膜を形成する処理を、一つの処理室内101において順次実行する。

(もっと読む)

半導体装置の作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間に金属酸化物層でなるバッファ層が設けられ

た逆スタガ型(ボトムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース

電極層及びドレイン電極層と半導体層との間に、バッファ層として金属酸化物層を意図的

に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

表示装置用金属配線膜

【課題】Si半導体層および/または透明導電膜との間のバリアメタル層を省略しても、低抵抗のオーミック特性を有する電気的接触を確保でき、更に十分な耐熱性を有する表示装置用金属配線膜を提供する。

【解決手段】Moを20原子%以上含有しており、且つ、Si、Nd、Ni、Mn、Mg、Fe、及びZnよりなる群から選択される少なくとも一種を5原子%以上含有しているAl合金膜53と、純CuまたはCu合金膜28,29とからなる積層膜であって、前記Al合金膜が、半導体層33と直接接続していると共に、前記CuまたはCu合金膜が透明導電膜55と直接接続している表示装置用金属配線膜。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

液晶表示装置及びその製造方法

【課題】製造に際して配線にヒロックが発生せず、かつエッチング形状の制御が容易な液晶表示装置を提供する。

【解決手段】液晶表示装置は、基板上にマトリクス配置された走査線と、信号線12と、前記走査線及び信号線に接続される薄膜トランジスタと、前記薄膜トランジスタに接続される画素電極27とを有する液晶表示装置において、前記走査線が下層からアルミニウム−ネオジム合金層211と高融点金属層212との積層構造からなり、前記信号線12が下層から高融点金属層231とアルミニウム−ネオジム合金層232と高融点金属層233との3層構造からなり、高融点金属の種類に応じて、ネオジム含有量を調整する。

(もっと読む)

太陽電池及びその製造方法

【課題】本発明は、太陽電池及びその製造方法に関する。

【解決手段】本発明の一実施形態による太陽電池は、太陽光を吸収して電気を発生させる太陽電池部と、上記太陽電池部の上面及び下面のうち少なくとも一面に形成され、非共有電子対を有する官能基−Yとアルコキシ基−ORとを有する化合物の縮合反応によって形成された表面処理層と、上記表面処理層の非共有電子対を有する官能基−Yと結合された金属電極層と、を含む。本発明による太陽電池はエネルギー変換効率に優れた特徴を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】電極層の電気伝導度の向上と、電極層の表面へのC原子の析出の抑制とを両立させることができる半導体装置およびその製造方法をを提供する。

【解決手段】電極層16は、炭化珪素基板90上に接し、かつNi原子およびSi原子を有する。Ni原子の数はNi原子およびSi原子の総数の67%以上である。電極層16の少なくとも炭化珪素基板90に接する側はSiおよびNiの化合物を含む。電極層16の表面側においてC原子濃度はNi原子濃度よりも小さい。

(もっと読む)

半導体装置

【課題】オーミック電極のコンタクト抵抗を低減する。

【解決手段】半導体装置は、第1の窒化物半導体層13上に形成され第1の窒化物半導体層13よりバンドギャップが大きい第2の窒化物半導体層14と、第2の窒化物半導体層14を貫通して第1の窒化物半導体層13の一部を除去する形状の凹部と、凹部を埋め込む電極17とを備える。第1の窒化物半導体層13の第2の窒化物半導体層14との界面直下に2次元電子ガス層13aを有する。電極17と第2の窒化物半導体層14とは第1のコンタクト面16aにて接する。電極17と2次元電子ガス層13aの部分とは、第1のコンタクト面16aの下に接続された第2のコンタクト面16bにて接する。第1のコンタクト面16aは凹部の幅が下から上に広くなる形状である。接続箇所において、第2のコンタクト面16bは、第1のコンタクト面16aよりも第1の窒化物半導体層13の上面に対して急峻である。

(もっと読む)

半導体装置

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置を提案することを課題とする。

【解決手段】基板上に形成されたゲート電極と、ゲート電極上に形成された酸素過剰のSiOX膜と、SiOX膜上に形成された酸化物半導体膜と、を有する半導体装置。

(もっと読む)

半導体装置

【課題】コンタクトホールの位置合わせが容易で、コンタクト抵抗の低いフィン型の電界効果型トランジスタを有する半導体装置に提供する。

【解決手段】フィン型の電界効果型トランジスタであって、ソース/ドレイン領域503の少なくともその幅が最も大きい部分では半導体領域502の幅よりも大きく、かつソース/ドレイン領域503の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部510を有し、該傾斜部表面にシリサイド膜504が形成されていることを特徴とする半導体装置とする。

(もっと読む)

薄膜トランジスタ基板およびそれの製造方法

【課題】薄膜トランジスタ基板およびこれの製造方法を開示する。

【解決手段】本発明の薄膜トランジスタ基板は、基板上に形成されたゲート電極、前記ゲート電極上に前記ゲート電極と重なるように形成され、多結晶シリコンを含むアクティブ層、前記アクティブ層上に前記ゲート電極を中心に両側に分離して形成された第1オーミックコンタクト層、前記第1オーミックコンタクト層上に形成された第2オーミックコンタクト層および前記第2オーミックコンタクト層上に形成されたソース電極およびドレーン電極を含む。

(もっと読む)

半導体装置

【課題】トレードオフの関係にある臨界オフ電圧上昇率dV/dtとゲート感度との関係を改善した半導体装置を提供する。

【解決手段】少なくとも、ゲートトリガ電流IGTの経路となるベース層(P型ベース領域、P型半導体領域P1)のゲート電極M1bとのオーミック接触面である高濃度不純物層を、高融点金属シリサイド層LMで形成する。

(もっと読む)

121 - 140 / 948

[ Back to top ]