Fターム[4M104HH15]の内容

Fターム[4M104HH15]に分類される特許

81 - 100 / 948

半導体装置

【課題】酸化物半導体層を用いる薄膜トランジスタにおいて、酸化物半導体層と電気的に

接続するソース電極層またはドレイン電極層との接触抵抗の低減を図ることを課題の一と

する。

【解決手段】ソース電極層またはドレイン電極層を2層以上の積層構造とし、その積層の

うち、酸化物半導体層と接する一層を酸化物半導体層の仕事関数より小さい仕事関数を有

する金属又はそのような金属の合金とする。二層目以降のソース電極層またはドレイン電

極層の材料は、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、または上述

した元素を成分とする合金か、上述した元素を組み合わせた合金等を用いる。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】薄膜トランジスタ液晶表示装置の薄膜トランジスタ及びその製造方法を提供する。

【解決手段】ゲート電極、ゲート絶縁層、活性層及びソースドレイン電極を有した薄膜トランジスタであって、該ゲート電極は該活性層のチャンネル領域と重なり、該ゲート絶縁層は該ゲート電極と該活性層間に設けられており、該ソースドレイン電極と該活性層のソースドレイン領域は重なり、該活性層と前記ソースドレイン電極間に電子の走行を許容する薄いSiNx又はSiOxNy層が設けられる。

(もっと読む)

大きい仕事関数および高い電気伝導度を有する電極を具備した電子素子

【課題】大きい仕事関数および高い電気伝導度を有する電極を具備した電子素子を提供する。

【解決手段】0.1S/cm以上の電気伝導度を有する導電性物質および低表面エネルギー物質を含み、第1面と、前記第1面に対向する第2面と、を有し、前記第2面の低表面エネルギー物質の濃度が、前記第1面の低表面エネルギー物質の濃度より高く、前記第2面の仕事関数が5.0eV以上であり、かつ前記第2面の電気伝導度が1S/cm以上である大きい仕事関数および高い電気伝導度を有する電極、を具備した電子素子である。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体素子および電子機器

【課題】有機半導体層の上面の層の形状不良を抑えることが可能な半導体素子およびこれを備えた電子機器を提供する。

【解決手段】有機半導体層と、有機半導体層の上面に設けられた層とを有し、この層の外形線は、有機半導体層の外形線よりも内側にある半導体素子。この半導体素子を備えた電子機器。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

半導体装置の製造方法

【課題】本実施形態は、コンタクトプラグの抵抗の低減を行うことができる半導体装置の製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、基板にコンタクトホール又はコンタクトトレンチを形成し、コンタクトホール又はコンタクトトレンチの底に、アモルファスシリコン層又は多結晶シリコン層を形成し、アモルファスシリコン層又は多結晶シリコン層を覆うように不純物を含むニッケル膜を形成し、加熱することによりニッケル膜とアモルファスシリコン層又は多結晶シリコン層とを反応させて、ニッケルシリサイド膜を形成し、コンタクトホール又はコンタクトトレンチを埋め込むようにコンタクト金属膜を形成する。

(もっと読む)

素子及び太陽電池並びに電極用ペースト組成物

【課題】焼成時における銅の酸化が抑制され、良好なオーミックコンタクトを有する銅含有電極がシリコンを含む基板上に形成された素子及び該素子を構成するのに好適な電極用ペースト組成物を提供する。

【解決手段】シリコンを含む基板と、前記基板上に配置された電極とを有し、前記電極は、銅含有粒子、ガラス粒子、溶剤及び樹脂を含む電極用ペースト組成物の焼物であり、体積抵抗率が1×10−4Ω・cm以下である素子である。また電極用ペースト組成物に、リン含有銅合金粒子、錫含有粒子、ガラス粒子、溶剤及び樹脂を含ませ、25℃における粘度が80Pa・s〜1000Pa・sの範囲であるように構成する。さらにまた電極用ペースト組成物に、リン含有銅合金粒子、錫含有粒子、ガラス粒子、溶剤及び樹脂を含ませ、固形分濃度が70質量%〜98質量%の範囲であるように構成する

(もっと読む)

半導体装置

【課題】窒化物半導体を用いた半導体装置のオン抵抗を低減できるようにする。

【解決手段】半導体装置は、アンドープのAlGaN層104と、該AlGaN層104の上に形成され、AlGaN層104とオーミック接触するソース電極107及びドレイン電極108とを有している。AlGaN層104の上部における少なくとも各電極107、108と接触する部分には、不純物拡散層110が形成されている。不純物拡散層110は、AlGaN層104に対しアクセプタ性を示す不純物が拡散し、且つ、AlGaN層104における窒素空孔と不純物とが結合してなる不純物準位が、AlGaN層104の伝導帯端の近傍に形成される。

(もっと読む)

半導体デバイス

【課題】低シート抵抗化、リーク電流の低減、および、オーミック電極の接触抵抗の低減を実現する。

【解決手段】基板と、基板上に設けられ第1の窒化物系化合物半導体からなるチャネル層と、チャネル層上に設けられたバリア層と、バリア層上に設けられた第1電極と、チャネル層の上方に設けられた第2電極とを備え、バリア層は、チャネル層上に設けられ第1の窒化物系化合物半導体よりバンドギャップエネルギーが大きい第2の窒化物系化合物半導体からなる障壁層と、第2の窒化物系化合物半導体よりバンドギャップエネルギーが小さい第3の窒化物系化合物半導体からなり量子準位が形成された量子準位層とを有する半導体デバイスを提供する。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】コンタクト抵抗を低減しつつ、イオン注入したp+層の消失を低減できる炭化珪素半導体装置の製造方法の提供を目的とする。

【解決手段】本発明にかかる炭化珪素半導体装置の製造方法は、(a)炭化珪素半導体基体表面にマスクとしての酸化膜マスク層21、酸化膜マスク層22を形成し、室温でイオン注入する工程と、(b)イオン注入を行った炭化珪素半導体基体表面を活性化アニールする工程と、(c)活性化アニール後の炭化珪素半導体基体表面を、ドライエッチングする工程と、(d)ドライエッチング後の炭化珪素半導体基体表面を犠牲酸化し、犠牲酸化膜5を形成する工程と、(e)犠牲酸化膜5を濃度10%以下の希フッ酸で5分以内のエッチングにより除去する工程と、(f)炭化珪素半導体基体裏面にオーミック電極6を、炭化珪素半導体基体表面の所定領域にショットキー電極7をそれぞれ形成する工程とを備える。

(もっと読む)

窒化物半導体発光素子およびその製造方法

【課題】窒化物半導体発光素子の電流拡散効率を向上させるとともに、コンタクト抵抗をも低減でき、大きな駆動電流密度においても発光均一性と高い光出力を得ながら、動作電圧を低減させる得る窒化物半導体発光素子およびその製造方法を提供する。

【解決手段】基板の同一面側にn側およびp側電極パッドが形成された窒化物半導体発光素子であって、p側電極パッド(およびn側電極パッド)から枝状に延伸された延長部を形成し、それによって発光素子中の電流分布を改善する電極構造の窒化物半導体発光素子において、n側およびp側のシート抵抗がいずれも充分に低い場合に、p型窒化物半導体層上に形成された透光性導電膜からなる電流拡散層のシート抵抗を一定条件下において高くすることにより、p型窒化物半導体層と電流拡散層とのコンタクト抵抗を低減し、且つ、シート抵抗の面内分布がより均一になり、光出力も向上する。

(もっと読む)

透明導電膜の作成方法

【課題】アモルファス状態の透明導電膜の光透過率を増加させ、シート抵抗を低下させ、p型半導体層とのオーミックコンタクトを形成する技術を提供する。

【解決手段】

真空排気された真空槽31内に、アモルファス状態の透明導電膜が表面に露出する処理対象物1が配置された状態で、真空槽31内に不活性ガスと酸素ガスとを、不活性ガスに対する酸素ガスの流量比が1/20以上3/7以下になるように導入して圧力を上昇させ、圧力が上昇した状態で処理対象物1を300℃以上800℃以下に加熱する(第一のアニール工程)。次いで、酸素ガスの導入を停止して、真空槽31内の酸素ガスの分圧が第一のアニール工程での酸素ガスの分圧よりも低下した状態で、処理対象物1を300℃以上800℃以下に加熱する(第二のアニール工程)。

(もっと読む)

半導体装置

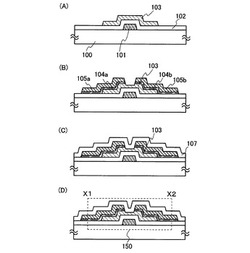

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間にバッファ層が設けられた逆スタガ型(ボト

ムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース電極層及びドレイン

電極層と半導体層との間に、半導体層よりもキャリア濃度の高いバッファ層を意図的に設

けることによってオーミック性のコンタクトを形成する。

(もっと読む)

有機素子の製造方法、有機分子結晶層の接合方法、細線状導電体の製造方法、有機素子および細線状導電体

【課題】電極に対して有機分子結晶層を配向制御して接合することができる有機分子結晶層の接合方法およびこの接合方法を利用した有機素子の製造方法を提供する。

【解決手段】絶縁性基体11上に電極12およびこの電極12と接合する芳香族化合物からなる有機分子結晶層13を形成する場合に、電極12の側面12aの絶縁性基体11の主面に対する傾斜角度を制御することにより、有機分子結晶層13の電極12に対する配向を制御する。電極12の側面を傾斜角度が互いに異なる複数の面により形成するようにしてもよい。

(もっと読む)

非晶質酸化物薄膜トランジスタ及びその製造方法、その薄膜トランジスタを含むディスプレイパネル

【課題】本発明の実施例は非晶質酸化物薄膜トランジスタ及びその製造方法、ディスプレイパネルを開示する。

【解決手段】前記非晶質酸化物薄膜トランジスタは、ゲート電極、ゲート絶縁層、半導体活性層、ソース電極及びドレイン電極を含む。前記半導体活性層はチャネル層とオーミック接触層を含み、前記チャネル層は前記オーミック接触層に比べ酸素含有量が高い。また、前記チャネル層は前記ゲート絶縁層と接し、前記オーミック接触層は二つの独立したオーミック接触領域に分けられ、かつ前記二つの独立したオーミック接触領域はそれぞれ前記ソース電極、ドレイン電極と接する。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化を図ることができる半導体装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極上に設けられた絶縁膜と、を有する積層体と、前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、を備える。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】ドレイン電極とドレイン層とのコンタクト抵抗を低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、第1導電型のドレイン層と、ドレイン層上に形成された第1導電型のドリフト層と、ドリフト層上に選択的に形成された第2導電型のベース層と、ベース層上に選択的に形成された第1導電型のソース層と、ゲート絶縁膜を介して、ドリフト層、ベース層及びソース層に跨って形成されたゲート電極と、ベース層及びソース層に電気的に接続されたソース電極と、ドリフト層を貫通して、底部の少なくとも一部がドレイン層にまで達する第1のトレンチ内に形成され、ドレイン層と電気的に接続されたドレイン電極と、を備え、底部には、凹凸が形成されている。

(もっと読む)

自己整合シリサイドの形成方法、半導体デバイスの製造方法、および半導体構造物

【課題】製造工程の増大を抑制し、コンタクト抵抗および界面抵抗の増大を防止する。

【解決手段】実施形態において、シリコン層は、ゲートラストスキームを用いた機能的ゲート電極の製造後に、形成される。初期的な半導体構造物は、半導体基板上に形成された少なくとも一つの不純物領域、不純物領域の上に形成された犠牲膜、犠牲膜の上に形成された絶縁層、絶縁層の上に形成された絶縁層を備える。ビアは、初期の半導体構造物の絶縁層へ、および、コンタクト開口部が絶縁層に形成されるように絶縁層の厚さを通り抜けて、パターン化される。次に、絶縁層の下にある犠牲膜は、絶縁層の下に空隙を残して除去される。次に、金属シリサイド前駆体は、空隙スペースに配置され、金属シリサイド前駆体は、アニールプロセスを通じてシリサイド層に変換される。

(もっと読む)

半導体素子及び半導体素子形成方法

【課題】ゲルマニウムをチャネル材料とする金属/ゲルマニウムからなるソース/ドレイン構造を有する半導体素子を提供する。

【解決手段】半導体と金属とが接合してソース/ドレイン構造を形成する半導体素子において、ゲルマニウム(Ge)を3価元素(又は5価元素)でドーピングしたp型ゲルマニウム(又はn型ゲルマニウム)をチャネル2の材料とし、当該p型ゲルマニウム(又はn型ゲルマニウム)の任意の結晶面における原子配置と同一の原子配置である結晶面を有する金属3を、前記同一の原子配置である結晶面で接合して界面を形成し、当該形成された界面を用いたソース/ドレイン構造を有する。

(もっと読む)

81 - 100 / 948

[ Back to top ]