Fターム[4M104HH15]の内容

Fターム[4M104HH15]に分類される特許

101 - 120 / 948

自己整合シリサイドの形成方法、半導体デバイスの製造方法、および半導体構造物

【課題】製造工程の増大を抑制し、コンタクト抵抗および界面抵抗の増大を防止する。

【解決手段】実施形態において、シリコン層は、ゲートラストスキームを用いた機能的ゲート電極の製造後に、形成される。初期的な半導体構造物は、半導体基板上に形成された少なくとも一つの不純物領域、不純物領域の上に形成された犠牲膜、犠牲膜の上に形成された絶縁層、絶縁層の上に形成された絶縁層を備える。ビアは、初期の半導体構造物の絶縁層へ、および、コンタクト開口部が絶縁層に形成されるように絶縁層の厚さを通り抜けて、パターン化される。次に、絶縁層の下にある犠牲膜は、絶縁層の下に空隙を残して除去される。次に、金属シリサイド前駆体は、空隙スペースに配置され、金属シリサイド前駆体は、アニールプロセスを通じてシリサイド層に変換される。

(もっと読む)

酸化物半導体用電極、その形成方法、及びその電極を備えた酸化物半導体装置

【課題】薄膜トランジスタなどの素子動作層をなす導電性インジウム含有酸化物半導体層に電気的接触抵抗が小さい金属電極を形成できるようにする。

【解決手段】インジウム含有酸化物半導体層とその層の上方に設けた素子動作電流を流通させる金属電極層との間に、酸化物半導体層をなすインジウム酸化物などを化学的に還元でき、且つ易酸化性の金属からなる金属膜を素材とした金属酸化物層と金属層とを設け、更に、金属酸化物層と金属層との境界には還元されたインジウムを蓄積したインジウム濃化層を設ける構成とする。

(もっと読む)

配線形成方法、及び配線形成装置

【課題】絶縁層が積層された導電層に該絶縁層を貫通するカーボンナノチューブが接続される配線構造にて電気的特性を向上することのできる配線形成方法、及び該方法を用いる配線形成装置を提供する。

【解決手段】

下部配線層32に積層された絶縁層34を貫通するホール35に、その内表面の全体が含まれるように触媒層36,37を形成した後、ホール35の内部にシースShが形成され、且つホール35の内壁面35aに対するシースの厚さがホール35の底壁面35bに対するシースShの厚さよりも小さくなるようにプラズマを生成する。そして、ホール35の内壁面35aに形成された触媒層36,37をプラズマ中のスパッタ粒子Spによって除去した後、ホール35の底壁面35bに残された触媒層36,37を用いて該底壁面35bからカーボンナノチューブ38を形成する。

(もっと読む)

半導体装置

【課題】p型SiC領域と金属との低抵抗コンタクトの実現を可能とする半導体装置を提供する。

【解決手段】実施形態の半導体装置は、導電性材料を用いた電極240と、導電型がp型の炭化珪素(SiC)半導体部220と、を備えており、かかるp型のSiC半導体部220は、前記第1の電極240に接続され、マグネシウム(Mg)、カルシウム(Ca)、ストロンチウム(Sr)、及びバリウム(Ba)のうちの少なくとも1種類の元素が前記電極との界面部に面密度がピークになるように含有されたことを特徴とする。

(もっと読む)

有機電子素子用電極、有機トランジスタ素子、インクジェットインク

【課題】接触抵抗を低減した有機電子素子用電極、及びこれを利用した有機トランジスタ素子を提供することを課題とする。

【解決手段】カーボンナノホーンを含んで構成された有機電子素子用電極、及び当該電極を、ソース電極18、及びドレイン電極20として適用した有機トランジスタ素子。

(もっと読む)

半導体発光素子及び半導体発光装置

【課題】高輝度、高効率、高信頼性を達成する半導体発光素子を提供する。

【解決手段】実施形態に係る半導体発光素子は、積層構造体と、電極と、を備える。積層構造体は、窒化物系半導体からなる第1導電形の第1半導体層と、窒化物系半導体からなる第2導電形の第2半導体層と、前記第1半導体層と前記第2半導体層との間に設けられた発光層と、を有する。電極は、第1金属層、第2金属層及び第3金属層を有する。第1金属層は、第2半導体層の発光層とは反対側に設けられ、銀または銀合金を含む。第2金属層は、第1金属層の第2半導体層とは反対側に設けられ、金、白金、パラジウム、ロジウム、イリジウム、ルテニウム、オスミウムの少なくともいずれかの元素を含む。第3金属層は、第2金属層の第1金属層とは反対側に設けられる。第3金属層の第1半導体層から第2半導体層に向かう方向に沿った厚さは、第2金属層の前記方向に沿った厚さ以上である。

(もっと読む)

有機電子素子用電極、有機トランジスタ素子

【課題】有機半導体に対する接触抵抗を低減した有機電子素子用電極、及びこれを利用した有機トランジスタ素子を提供することを課題とする。

【解決手段】金属層24Aと、金属層24Aの表面の少なくとも一部に付着したカーボンナノチューブ24Bと、を有する有機電子素子用電極、及び当該電極を、ソース電極18、及びドレイン電極20として適用した有機トランジスタ素子。

(もっと読む)

表示装置および半導体装置用Al合金膜

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、膜自体の電気抵抗(配線抵抗)も低く、アルカリ環境下の耐食性にも優れた表示装置用Al合金膜を提供する。

【解決手段】Geを0.01〜2.0原子%と、Ta、Ti、Zr、Hf、W、Cr、Nb、Mo、Ir、Pt、Re、およびOsよりなる群(X群)から選択される少なくとも一種の元素とを含み、450〜600℃の加熱処理を行なったとき、下記(1)の要件を満足する表示装置もしくは半導体装置用Al合金膜である。

(1)Alと、前記X群から選択される少なくとも一種の元素と、Geとを含む第1の析出物について、円相当直径50nm以上の析出物が200,000個/mm2以上の密度で存在する。

(もっと読む)

炭化ケイ素パワーデバイスを有する半導体ウェハを処理する方法

【課題】

ドーパントが注入されたSiC基板がオーミックコンタクトの形成前に薄くされる場合には、オーミックコンタクトを形成するために堆積された金属は、基板上に堆積されたときにオーム特性を持たないことがある。

【解決手段】

炭化ケイ素半導体デバイスを形成する方法は、第1の厚さを有する炭化ケイ素基板の第1の表面に半導体デバイスを形成するステップと、前記第1の表面にキャリア基板を取り付けるステップとを含む。さらに、前記炭化ケイ素基板を、前記第1の厚さ未満の厚さまで薄くするステップ、前記第1の表面とは反対側の前記薄くされた炭化ケイ素基板の表面に金属層を形成するステップ、前記金属層を局所的にアニールするステップを含む。前記炭化ケイ素基板は、個片化された半導体デバイスを提供するために、個片化される。

(もっと読む)

炭化珪素ジャンクションバリアショットキーダイオードおよびその製造方法

【課題】炭化珪素ジャンクションバリアショットキーダイオードの製造において、ハードマスクを使用せずに、pウェル上に選択的にp+領域を形成し、また金属電極とp+領域とコンタクト抵抗を低減する。

【解決手段】n型のエピタキシャル層2の上部全体に高温イオン注入によってp+領域4aを形成し、当該p+領域4aを選択的にエッチングしてp+領域4a下のn型領域を部分的に露出させることにより、そのn型領域の上面より上方へ突出したp+半導体凸部4を形成する。アノード電極は、上記のn型領域の露出した部分およびp+半導体凸部4を覆うように形成される。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コンタクトとアクティブエリアとの間のショートマージンを確保できる半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板と、前記半導体基板の上層部分に形成され、前記上層部分を第1方向に延びる複数本のアクティブエリアに区画する複数本の素子分離絶縁体と、前記アクティブエリアに接続されたコンタクトと、を備える。そして、各前記アクティブエリアの上面のうち、前記第1方向における一部の領域には、前記第1方向に対して直交する第2方向において前記アクティブエリアの全体にわたって凹部が形成されている。前記第1方向において、隣り合う前記アクティブエリアにそれぞれ接続された2本の前記コンタクトの位置は相互に異なる。前記コンタクトは前記凹部の側面に接し、底面には接していない。

(もっと読む)

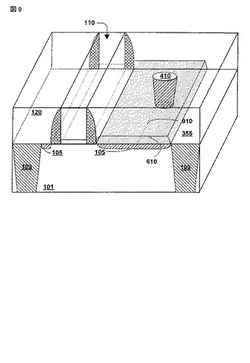

半導体装置の製造方法及び半導体装置

【課題】実施形態によれば、ホールの深さのばらつきを防ぐ半導体装置の製造方法及び半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、複数の第1の開口と第1の開口よりも密に並んだ複数の第2の開口とを有するマスクを用いて層間絶縁層61をドライエッチングし、第1の開口の下で下地層10に達する第1のホールと、第2の開口の下で下地層10に達する第2のホール41とを同時に形成する工程を備えている。第1のホールは他の第1のホールとは接することなく下地層10に達する。ドライエッチングの開始後、複数の第2の開口のそれぞれの下に複数のホールhが形成され、ドライエッチングの進行に伴って、複数のホールhは少なくとも開口端を含む上部42で互いにつながる。

(もっと読む)

へテロ接合電界効果型トランジスタ及びその製造方法

【課題】耐圧特性の低下やゲートリーク電流の増加を生じることなく、低抵抗で高速動作可能なヘテロ接合電界効果型トランジスタおよびその製造方法を提供する。

【解決手段】ヘテロ接合FETの製造方法に関し、(a)チャネル層3及びチャネル層3上に形成されたバリア層4を窒化物半導体層として準備する工程と、(b)窒化物半導体層上に不純物拡散源としてZnO膜9を形成する工程と、(c)ZnO膜9上のドレイン電極6及びソース電極5を形成すべき領域以外に酸化膜10を形成する工程と、(d)窒化物半導体層に対して熱処理を行い、酸化膜10が形成されていない領域の下部のチャネル層3及びバリア層4に選択的に、ZnO膜9からZn及びOを拡散させる工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】低温で高品質な生成膜の生成を可能とし、デバイスの性能の向上を図ると共に歩留りの向上を図る半導体装置の製造方法を提供する。

【解決手段】処理室に基板を搬入する工程と、処理室及び基板を所定の温度に加熱する工程と、処理室に所定のガスを給排するガス給排工程とを含み、ガス給排工程は、シラン系のガスと水素ガスとを処理室に供給する第1の供給工程と、少なくともシラン系のガスを処理室から除去する第1の除去工程と、塩素ガスと水素ガスとを処理室に供給する第2の供給工程と、少なくとも塩素ガスを処理室から除去する第2の除去工程とを、所定回数繰返して実行させる。

(もっと読む)

半導体装置およびその作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置、およびその作製方法を提供することである。

【解決手段】基板上に下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、第1の加熱処理を行って第2の酸化物半導体膜を形成した後、選択的にエッチングして、第3の酸化物半導体膜を形成し、第1の絶縁膜および第3の酸化物半導体膜上に絶縁膜を形成し、第3の酸化物半導体膜の表面が露出するように絶縁膜の表面を研磨して、少なくとも第3の酸化物半導体膜の側面に接するサイドウォール絶縁膜を形成した後、サイドウォール絶縁膜および第3の酸化物半導体膜上にソース電極およびドレイン電極を形成し、ゲート絶縁膜およびゲート電極を形成する。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体発光素子及びその製造方法

【課題】電気的特性が良好で加工性が良好な電極を有する半導体発光素子及びその製造方法を提供する。

【解決手段】実施形態によれば、第1導電形の第1半導体層と、第2導電形の第2半導体層と、発光部と、第1導電層と、第2導電層と、を備えた半導体発光素子が提供される。前記発光部は、前記第1半導体層と前記第2半導体層との間に設けられる。前記第1導電層は、第1平均粒径を有する多結晶を含み、前記発光部から放出される光に対して透過性である。前記第2導電層は、前記第2半導体層と前記第1導電層との間において前記第2半導体層と前記第1導電層とに接し、前記第1平均粒径よりも小さく150ナノメートル以下の第2平均粒径を有する多結晶を含み、前記光に対して透過性である。

(もっと読む)

レーザアニール方法及びレーザアニール装置

【課題】高エネルギ効率でレーザアニールを行う方法及び装置を提供する。

【解決手段】(a)不純物がイオン注入により添加されたSiC基板を準備する。(b)SiC基板に、炭酸ガス(CO2)レーザ発振器から出射された反射率の低い9μm〜10.3μmの範囲内のいずれかの波長のレーザビームを照射して、SiC基板に添加された不純物を活性化させる。

(もっと読む)

薄膜トランジスタ、アクティブマトリクス基板、およびそれらの製造方法

【課題】材料の選択幅が広く、生産性が高いTFT、アクティブマトリクス基板、およびそれらの製造方法を提供すること。

【解決手段】本発明にかかる薄膜トランジスタは、ゲート電極2と、半導体層5と、半導体層5の上に設けられ、半導体層5と電気的に接続されたソース電極7、及びドレイン電極8と、を備えた薄膜トランジスタであって、半導体層5が、透光性半導体膜5aと、透光性半導体膜5a上に配置され、透光性半導体膜5aよりも光透過率の低いオーミック導電膜5bと、を有し、オーミック導電膜5bが、透光性半導体膜5aからはみ出さないように形成され、オーミック導電膜5bが、ソース電極7とドレイン電極8の間のチャネル部9を挟むように分離して形成され、ソース電極7、及びドレイン電極8が、オーミック導電膜bを介して、透光性半導体膜5aに接続されているものである。

(もっと読む)

半導体装置

【課題】十分なチャネル移動度と製造コストの低減とを両立することが可能な半導体装置を提供する。

【解決手段】MOSFET100は、{0001}面に対するオフ角が50°以上65°以下である主面1Aを有する炭化珪素基板1と、主面1A上に形成された活性層7と、活性層7上に接触して形成されたゲート酸化膜91と、活性層7においてゲート酸化膜91と接触する領域を含むように形成され、導電型がp型であるp型ボディ領域4と、p型ボディ領域4内において活性層7の炭化珪素基板1とは反対側の主面を含むように形成され、導電型がn型であるn+領域5と、活性層7上にn+領域5と接触するように形成されたソースコンタクト電極92とを備え、p型ボディ領域4におけるp型不純物密度は5×1017cm−3以上であり、ソースコンタクト電極92とp型ボディ領域4とは直接接触している。

(もっと読む)

101 - 120 / 948

[ Back to top ]