Fターム[4M112DA10]の内容

Fターム[4M112DA10]に分類される特許

41 - 60 / 234

力学量センサ及びその製造方法

【課題】外力の大きさ及び方向並びに加速度を検出することができ、低コストに製造することのできる力学量センサ及びその製造方法を提供すること。

【解決手段】本発明の一実施形態に係る力学量センサは、第1基板と、前記第1基板上に配置された固定部と、前記固定部に一端部が支持されて前記第1基板から離隔して配置された可動電極と、前記可動電極の周囲に位置し力学量の検出方向に配置された固定電極と、前記固定部に電気的に接続された第1端子と、前記固定電極に電気的に接続された第2端子と、を備えることを特徴とする。

(もっと読む)

可動ゲート型加速度センサ

【課題】変位測定範囲を増加させた可動ゲート型加速度センサを提供することにある。

【解決手段】複数のソース電極17a,17bとドレイン電極18a,18bの組みを設け、ソース電極17a,17bそれぞれにソース配線部19a,19bを接続し、ドレイン電極18a,18bそれぞれにドレイン配線部20a,20bを接続し、それぞれの組のチャネル形成領域21の上方に矩形状の可動ゲート15が共通に配置される可動ゲート型加速度センサとした。

(もっと読む)

可動ゲート型電界効果トランジスタ

【課題】可動ゲート電極の変位を制御可能な可動ゲート型電界効果トランジスタを提供する。

【解決手段】ソース電極17とドレイン電極18との上に導電シールド電極20が配置される可動ゲート型電界効果トランジスタ1とした。そして導電シールド電極20の電位を固定することとした。導電シールド電極20が配置されることにより、可動ゲート15とドレイン電極18またはソース電極17との間に発生する静電力を抑制することができる。

(もっと読む)

圧力センサおよび圧力センサの製造方法

【課題】基準圧室としての空洞を基板の内部に設けることにより、低コスト化かつ小型化を実現可能な圧力センサを提供すること。

【解決手段】この圧力センサ1は、シリコン基板2を備えている。シリコン基板2の内部には、シリコン基板2の主面に平行な方向に平たい扁平空間4が形成されており、この扁平空間4とシリコン基板2の表面21との間には貫通孔6が形成されている。貫通孔6にアルミニウム充填体8が充填されて埋め込まれることにより、扁平空間4は、基準圧室として密閉されている。そして、扁平空間4に対してシリコン基板2の表面21側には、シリコン基板2におけるその表面21と扁平空間4との間の部分(ダイヤフラム5)の歪み変形により電気抵抗が変化するピエゾ抵抗R1〜R4が形成されている。

(もっと読む)

半導体圧力センサおよびその製造方法

【課題】第2シリコン基板の第1シリコン基板と対向する面で、凹部と対向する部位と第1シリコン基板と接合された部位との境界における応力集中を緩和することにより、破壊耐圧を向上させることができる半導体圧力センサおよびその製造方法を提供する。

【解決手段】一方の面3に凹部8aが形成された第1シリコン基板2と、凹部8aを封止するように第1シリコン基板2に一方の面7が接合された第2シリコン基板6と、第2シリコン基板6の他方の面12に形成された歪検出素子13と、第2シリコン基板6の一方の面7で凹部8aと対向する部位に、少なくとも凹部8aと対向する部位と第1シリコン基板2の一方の面3と接合された部位との境界を覆うように形成された第1酸化シリコン膜18と、を備える。

(もっと読む)

センサ製造方法

【課題】製造および動作信頼性の改善と共に必要とされる性能特性をもたらす、シングルチップ上に製造された1つまたは複数のセンサを提供すること。

【解決手段】センサ製造方法が開示され、一実施形態では、ダブルシリコンオンインシュレータのウェーハを備えるエッチング済み半導体基板ウェーハ(130)を、エッチング済みデバイスウェーハ(142)に接着して懸垂構造体を作製し、同構造体の撓みが、埋め込まれた圧電抵抗センサ素子(150)によって検知される。一実施形態では、センサは加速度を測定する。他の実施形態では、センサは圧力を測定する。

(もっと読む)

加速度センサの製造方法、1軸加速度センサ

【課題】ピエゾ抵抗素子の形成位置の精度を高め、加速度センサの歩留まりを向上させる。

【解決手段】単結晶シリコンからなる基板の表層に不純物を導入することによってピエゾ抵抗部を形成し、非原型領域のうち、可撓部Fの原型領域の第三端および第四端に隣接し前記第三端と第四端とからそれぞれ一定距離の幅を有する側壁形成領域において、前記基板の表面に、前記基板に対するエッチング選択性を有する側壁14aを形成し、可撓部Fの原型領域および錘部Mの原型領域および枠部Sの原型領域を保護する保護部と、側壁14aとをマスクに用いて前記基板を異方性エッチングすることにより、枠部Sと錘部Mと可撓部Fとを形成するとともに、前記ピエゾ抵抗部からピエゾ抵抗素子P1、P2、P3、P4を形成する。

(もっと読む)

素子構造および素子製造方法

【課題】使用時の電流ばらつきを抑えながら空乏層の接触を防止する素子構造を提供する。

【解決手段】SOI基板の表面(N型層)にP型ドーパントをイオン注入することで、ピエゾ抵抗を形成する。その後、裏面側の支持用基板層のピエゾ抵抗の対向位置をエッチングし、裏面側から全面にN型ドーパントをイオン注入し、N+層を形成する。表面側のN型層基板は、支持用基板層がエッチングされた箇所だけN+層となる。N+層が裏面側の空乏層の広がりを抑止するため、基板の比抵抗を高くしてもピエゾ抵抗の空乏層と接触することがない。例えば、基板の比抵抗を1Ω・cm以上とすれば、ドーパント濃度は1×1016個/cm3以下となり、ピエゾ抵抗のドーパント濃度(例えば1×1018個/cm3)に対して少なくなり、基板の比抵抗のばらつき(1Ω・cm〜10Ω・cm程度)が、ピエゾ抵抗の抵抗値のばらつきに与える影響は非常に小さくなる。

(もっと読む)

半導体圧力センサおよびその製造方法

【課題】半導体圧力センサの製造工程における、貫通穴の形成を抑制し、製造歩留まりの向上を図る。

【解決手段】本発明の半導体圧力センサは、ダイヤフラム部Dを備えた半導体基板3と、前記ダイヤフラム部Dに印加される圧力を抵抗値変化として検出するピエゾ抵抗素子(2a、2b、2c、2d)と、前記ダイヤフラム部表面及び前記ピエゾ抵抗素子表面を含む前記半導体基板表面を覆うアルカリ耐性を持つ第1の絶縁膜8aと、前記第1の絶縁膜の上層に形成され、少なくとも前記第1の絶縁膜の表面を覆う導電性薄膜7と、前記導電性薄膜表面を覆うアルカリ耐性を持つ第2の絶縁膜8bとを具備している。

(もっと読む)

半導体圧力センサ及びその製造方法

【課題】本発明は、半導体圧力センサ及びその製造方法に係り、Si基板の開口部のダイヤフラム側壁すべてをその基板面に対して垂直な面とすることにある。

【解決手段】半導体圧力センサは、単結晶シリコン基板と、前記単結晶シリコン基板を裏面側からエッチングすることによって形成されたダイヤフラム及び4面のダイヤフラム側壁と、前記単結晶シリコン基板の表面側に形成されたリード導体及び歪ゲージ抵抗からなるブリッジ回路と、を備え、前記ダイヤフラムは、面方位が(110)面であり、かつ、平面形状が平行四辺形であり、前記ダイヤフラム側壁は、4面とも面方位が(111)面であり、かつ、2面ずつ互いに平行に向かい合っており、圧力印加に伴う前記ダイヤフラムの撓み量に応じて前記ブリッジ回路の出力値が変動することを利用して、前記ダイヤフラムに印加される被検出対象の圧力を検出する。

(もっと読む)

圧力センサおよびその製造方法

【課題】圧力センサにおいて2枚の単結晶シリコン基板を張り合わせたものやSOI基板を適用せずに、圧力センサにおいて十分な性能(感度等)を確保すると共に、そのコストをより抑制する。

【解決手段】シリコン基板1の一端面側に形成された酸化膜(またはシリコン窒化膜)2表面に対し膜成長によってポリシリコン膜3が形成される。また、ポリシリコン膜3中には、拡散領域5と、その拡散領域5と接触するようにピエゾ抵抗素子7が形成される。そして、前記シリコン基板1他端面側からエッチングされて形成され前記酸化膜におけるピエゾ抵抗素子7の位置に対して、ダイアフラム101が形成される。

(もっと読む)

微小電気機械装置、半導体装置、微小電気機械装置の製造方法、および半導体装置の製造方法

【課題】微小電気機械装置の特性向上および製造工程の簡略化を図る。

【解決手段】微小電気機械装置を、半導体層(1)と、前記半導体層中のチャネル領域の両側に形成されたソース、ドレイン領域(13)と、前記半導体層上に形成されたゲート絶縁膜(19)と、前記ゲート絶縁膜上に形成された空洞(15a)と、前記空洞上に形成されたゲート電極(17)と、を有し、前記ゲート電極は、前記ゲート絶縁膜と接触するよう可動に構成され、前記ゲート電極上に加わる力を、前記ゲート電極と前記ゲート絶縁膜との接触面積により検出するように構成する。このように、上記接触面積によりゲート電極上に加わる力を検出することができる。また、一時的なFET構造を利用することにより、装置および製造工程の簡略化を図ることができる。

(もっと読む)

センサデバイス及びその製造方法

【課題】センサ内部の配線パターンの設計や製造工程を変更せずに、配線パターンを容易に変更可能にするセンサデバイス及びその製造方法を提供する。

【解決手段】センサデバイスは、複数のピエゾ素子231,232と、複数の接続パッド261〜265と、ピエゾ素子231,232と電気的に接続された上層配線240、241と、上層配線240及び241に接続された下層配線251及び252と、下層配線251及び252に対して垂直方向に交差する上層配線242〜244と、上層配線242〜244の下層の下層配線253〜257があり、下層配線253〜257の他端部の上層には、絶縁層を介して接続パッド261〜265が形成される。

(もっと読む)

MEMSセンサ

【課題】安価に製造することができるMEMSセンサを提供する。

【解決手段】MEMSセンサの一例であるシリコンマイク1は、開口5が貫通して形成されたシリコン基板2と、開口5に対向して設けられ、その対向方向に振動可能な振動膜6と、振動膜6に形成された圧電素子9とを含んでいる。

(もっと読む)

1軸加速度センサ

【課題】 少ない工程で製造できる1軸加速度センサを提供する。

【解決手段】 支持部(S)と、平行する二つの面に内周面が開口している凹部(50)が形成され前記凹部内に重心を有する錘部(M)と、一端が前記支持部と結合し他端が前記凹部の底面に結合している板ばね形の可撓部(F)と、前記可撓部の長手方向の両端近傍でかつ前記可撓部の短手方向の両端近傍に少なくとも2つずつ互いに前記可撓部の厚さ方向に離間して設けられる歪み検出素子(P1〜P4)と、を備える。

(もっと読む)

静電容量型超音波振動子

【課題】振動子エレメントの両端に溝部を設けた静電容量型超音波振動子において、全体に占めるセル領域の面積比率を低下させず、かつ発生させる超音波の出力低下のない静電容量型超音波振動子を提供する。

【解決手段】シリコン基板と、該シリコン基板の上面に配設された第1の電極と、該第1の電極と対向し所定の空隙を隔てて配設された第2の電極と、該第2の電極を支持するメンブレンとからなる振動子セルから構成され、駆動制御信号を入出力する最小単位である振動子エレメントと、前記シリコン基板の背面に電極パッドを介して接合したフレキシブルプリント基板とから構成される静電容量型超音波振動子において、隣接する前記振動子エレメント間に溝部が設けられ、該溝部に導電膜が形成されていることにより、上記課題の解決を図る。

(もっと読む)

加速度センサ

【課題】 加速度センサにおいて、検出対象の加速度に対する応答性を改善する。

【解決手段】 支持部と、前記支持部に一端が結合している板ばね形の可撓部と、前記可撓部の他端が結合している錘部と、前記可撓部の歪みを検出する歪み検出手段と、を備え、前記錘部に、前記可撓部の厚さ方向と平行でない面を有する凹部および凸部が形成され、前記支持部に、前記錘部に形成された凹部の内側において当該凹部と対向する凸部と、前記錘部に形成された凸部と内側において対向する凹部とが形成されている。

(もっと読む)

加速度センサ

【課題】 強い衝撃を受けても破損しにくい加速度センサを提供する。

【解決手段】 枠部(S)と、前記枠部の内側に一端が結合している板ばね形の可撓部(F)と、前記可撓部の他端が結合している錘部(M)と、前記可撓部の歪みを検出する第一歪み検出手段(P1〜P4)と、前記枠部および前記可撓部および前記錘部のいずれかに設けられ前記錘部が予め設計された所定範囲より大きく変位することを抑制するダンパであって、前記錘部の運動方向に撓む板ばね形のダンパ(40,41)と、を備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】半導体ウェハ周縁部にフォトレジストを形成することなく半導体ウェハ周縁部の半導体層に不純物イオンが注入されるのを防止し、電解エッチング処理の際に半導体ウェハの表面側と裏面側で電気的に短絡するのを防止する。

【解決手段】半導体ウェハ1の周縁部に、後工程のイオン注入工程でN型領域5に注入されるP型不純物イオンが突き抜けない程度の膜厚で周縁部絶縁膜13を形成する。半導体ウェハ1の主表面上にP型不純物イオンの注入領域を画定するためにフォトレジスト17を形成する。イオン注入法により、フォトレジスト17及び周縁部絶縁膜13をマスクにして半導体ウェハ1のN型領域5の所定の領域にP型不純物イオンを注入してP型領域19を形成する。フォトレジスト17を除去し、半導体ウェハ1の主表面に配線処理を行なった後、半導体ウェハ1のP型シリコン基板3に対して電解エッチング処理を行なう。

(もっと読む)

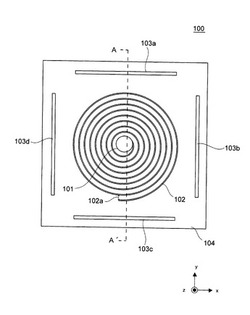

加速度センサ素子、加速度センサ装置及び加速度センサ素子の製造方法

【課題】重り部の強度を維持しつつ梁部を長くすることが可能な加速度センサ素子を提供する。

【解決手段】加速度センサ素子1は、開口部13が形成された固定部3と、開口部13内に配置される重り部7と、一方端が重り部7に連結され、他方端が固定部3に連結される梁部5と、梁部5に設けられ、梁部5の変形に伴って抵抗値が変化する抵抗素子9とを有する。重り部7は、梁部5の一方端が連結される主部15と、主部15に連結され、梁部5の重り部7側の端部よりも固定部3側に突出する付属部17とを有する。付属部17(非重なり部19)は、開口部13の開口方向に見て梁部5と重ならない位置において主部15に連結されている。さらに、付属部17(重なり部21)は、梁部5よりも第2主面Sb側、且つ、開口方向に見て梁部5と重なる位置において主部15に連結されている。

(もっと読む)

41 - 60 / 234

[ Back to top ]