Fターム[4M118DD12]の内容

Fターム[4M118DD12]に分類される特許

41 - 60 / 2,088

撮像装置及びその駆動方法

【課題】ランダムノイズの影響を低減した撮像装置を提供することを課題とする。

【解決手段】入射光に応じて発生した電荷を蓄積して信号を出力する複数画素の有効画素領域及び入射光に依存しない信号を出力する複数画素の非有効画素領域を含む画素部と、前記画素部の画素の列毎に設けられる複数の垂直信号線と、前記画素部の画素を行単位に走査して選択することにより前記選択された同一行の画素の信号を前記複数の垂直信号線に出力させる垂直走査回路と、前記複数の垂直信号線の信号を走査して選択することにより前記選択された垂直信号線の信号を出力させる水平走査回路とを有し、前記垂直走査回路は、1フレームの間に前記有効画素領域の同一行の画素を行単位で1回選択し、1フレームの間に前記非有効画素領域の同一行の画素を行単位で複数回選択することを特徴とする撮像装置が提供される。

(もっと読む)

裏面照明ピクセルアレイの動作方法

【課題】光を感知するピクセル面積量が減少することがなく、低照度性能が低下することがないイメージセンサを提供する。

【解決手段】裏面照明(「BSI」)イメージセンサピクセル(400)は、フォトダイオード領域(420)と、ピクセル回路(430)とを含む。フォトダイオード領域は、BSIイメージセンサピクセルの裏面上に入射する光に応答してイメージ電荷を蓄積するために半導体ダイ内に配置される。ピクセル回路が、半導体ダイの前面とフォトダイオード領域との間で半導体ダイ内に配置されたトランジスタピクセル回路を含む。ピクセル回路の少なくとも一部はフォトダイオード領域に重なり合っている。

(もっと読む)

固体撮像装置及び電子機器

【課題】複数のフォトダイオード間の例えば感度等の特性のばらつきを抑制することができる固体撮像装置を提供する。

【解決手段】固体撮像装置を、複数の光電変換部と、フローティングディフュージョン部と、複数の転送部と、第1トランジスタ群と、第2トランジスタ群とを備える構成にする。さらに、第1トランジスタ群は、第1のレイアウト構成で配置されたゲート及びソース/ドレインを有する。そして、第2トランジスタ群を、第1のレイアウト構成と対称的な第2レイアウト構成で配置されたゲート及びソース/ドレインを有する構成にする。

(もっと読む)

光電変換装置及び撮像システム

【課題】既存のCMOS形成製造方法を用いながら、撮像性能向上に寄与するPD形成用ウエル構造を実現する。

【解決手段】光を信号電荷に変換する光電変換領域を含む画素と、該画素が形成された画素領域外に、前記信号電荷を処理するための回路を含む周辺回路が同一基板上に配置された光電変換装置において、前記基板に形成された第一導電型の第1の半導体領域と前記信号電荷と同導電型である第二導電型の第2の半導体領域を含んで前記光電変換領域が形成され、第一導電型の第3の半導体領域を含んで前記周辺回路が形成されており、前記第1の半導体領域の不純物濃度は前記第3の半導体領域の不純物濃度よりも高い。

(もっと読む)

画素をバーストリセット動作と統合することにより改善された性能を有するCMOSイメージセンサ

【課題】小型画素及び高性能CMOSイメージセンサアレイで使用することができる実質

的な画素設計を提供すること。

【解決手段】本発明のリセットトランジスタは、電荷を検出するフローティング拡散領域

と、電荷を排出する接合領域と、リセット信号の制御を受けて、前記フローティング拡散

領域から前記接合領域への電荷転送を制御するゲートと、該ゲートの下部に統合された電

位井戸とを備えることを特徴とする。

(もっと読む)

撮像装置

【課題】1フレームの画像を撮像するための時間を長くすることなく、暗電流による画質劣化を低減する。

【解決手段】撮像装置は、互いに近接する第1及び第2の光電変換部PDA,PDBの組を複数有する撮像素子4と、前記各組の第1の光電変換部PDAを同時に一旦リセットしてから前記各組の第1及び第2の光電変換部PDA,PDBを露光した後に、前記各組の前記第1の光電変換部PDAをリセットすることなく前記各組の第2の光電変換部PDBを同時に一旦リセットした後、前記各組の第1及び第2の光電変換部PDA,PDBに蓄積された信号を読み出す制御を行う制御手段と、を備える。

(もっと読む)

固体撮像素子および電子機器

【課題】画質の低下を抑制する。

【解決手段】センサチップは、複数のPDが配置された半導体基板を有している。信号処理チップは、センサチップに積層され、センサチップを駆動するためのロジック回路が形成された半導体基板を有している。そして、センサチップの半導体基板と、信号処理チップの半導体基板との間に、信号の送受信を行う配線を有する配線層が配置されており、その配線層において配線が形成されていない領域に、遮光性を備えた遮光膜が配設される。本技術は、例えば、裏面照射型のCMOS型固体撮像素子に適用できる。

(もっと読む)

周辺回路を配置しチップ面積増大を抑制した撮像素子及び撮像装置

【課題】画素部の性能を損なわず、かつ周辺回路のチップ面積増大によるコストの増大を抑制する撮像素子を提供する。

【解決手段】撮像素子において、画素部101のうち、転送スイッチ203およびFD204およびリセットスイッチ207および増幅MOSアンプ205が第1半導体基板に形成され、列読み出し回路103または出力回路107または駆動回路の少なくとも一部が第1半導体基板以外の第2半導体基板に形成されている。

(もっと読む)

イメージセンサのピクセル縮小のためのコンタクト構造及びその製造方法

【課題】フィルファクターの低下なしで、ピクセル縮小が可能なイメージセンサ及びその製造方法を提供する。

【解決手段】イメージセンサのピクセルは、ピクセル内に互いに電気的に接続が必要なポリシリコン402と活性領域401を有するイメージセンサにおいて、前記ポリシリコン膜が、前記活性領域の上部に一部が重なるように拡張され、前記ポリシリコン膜が、前記活性領域と埋没コンタクト403されるようにする。

(もっと読む)

撮像素子及び撮像装置

【課題】CMOS型の撮像素子において、画素の受光面積を確保しつつ、画質の低下を抑制する。

【解決手段】光を電荷に変換する光電変換部と、変換された電荷をフローティングディフュージョン部に転送するための転送トランジスタと、フローティングディフュージョン部の電位に基づく信号を信号線に出力するためのソースフォロワアンプと、フローティングディフュージョン部の電位をリセットするためのリセットトランジスタとをひとつの単位構造とし、複数の単位構造が行方向と列方向の2次元状に配置された撮像素子であって、複数の単位構造を複数の組に分け、分けられた組ごとに転送トランジスタを制御する制御部を備える。

(もっと読む)

半導体装置、半導体装置の製造方法、固体撮像装置、固体撮像装置の製造方法、電子機器

【課題】MOSトランジスタのサイズを変えることなく、ノイズの低減が図られた半導体装置とその製造方法を提供することを目的とする。また、そのMOSトランジスタを備えることにより、ノイズの低減が図られた固体撮像装置とその製造方法を提供することを目的とする。

【解決手段】埋め込みチャネル型のMOSトランジスタにおいて、素子分離部24側に接する領域に、斜め方向からのイオン注入により形成した第1の不純物拡散領域14aと、ゲート電極26下の領域全面に形成した第2の不純物拡散領域14bとによりチャネル領域14を構成する。第1の不純物拡散領域14aの形成により、チャネル領域14の素子分離部24側で発生する不純物濃度の低下分を補填でき、実効ゲート幅の拡大が可能となる。

(もっと読む)

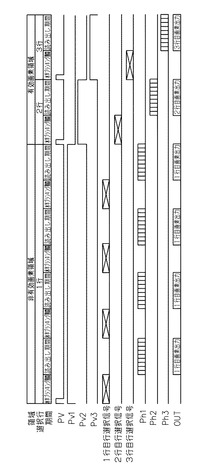

感知装置および感知方法

【課題】感度を向上させることができる感知装置と感知方法とを提供する。

【解決手段】第1および第2走査線と読み出し線と第1および第2感知ユニットを含む感知装置が提供される。第1感知ユニットが第1走査線と第2走査線と読み出し線とに連結されるとともに、第1エネルギーを感知するよう配置される。第1感知ユニットが第1走査線上で第1走査信号に応答して第1エネルギーに対応する第1読み出し信号を読み出し線へ出力する。第2感知ユニットが第2走査線と読み出し線と連結されるとともに、第2エネルギーを感知するよう配置される。第2感知ユニットが第2走査線上で第2走査信号に応答して第2エネルギーに対応する第2読み出し信号を読み出し線へ出力する。第2走査信号が第1走査信号と協同して働き、第1感知ユニットをリセットする。

(もっと読む)

固体撮像装置および固体撮像装置の製造方法

【課題】電荷の転送効率を向上させることができる固体撮像装置を提供すること。

【解決手段】固体撮像装置10は、第1の不純物層23、第2の不純物層24、第3の不純物層25、およびゲート電極28、を具備する。第1の不純物層23は、半導体基板11に一定の深さを有するように形成され、照射された光に応じて電荷を発生させる。第2の不純物層24は、第1の不純物層23の表面に、所定の方向に向かって深さが浅くなるように形成される。所定の方向は、第1の不純物層23から第3の不純物層25に向かう方向である。第3の不純物層35は、半導体基板11の表面において、第1の不純物層23および第2の不純物層24と離間した位置に形成され、第1の不純物層23で発生した電荷を電圧に変換する。

(もっと読む)

光電変換装置の製造方法

【課題】 光電変換素子に対するマイクロレンズの位置が高精度に制御された光電変換装置を提供する。

【解決手段】 半導体ウエハ1000の活性領域110を画定する分離領域120を形成する工程(S1)と、分離領域120によって画定された活性領域120に光電変換素子130を形成する工程(S4)と、光電変換素子130の上にマイクロレンズ600を形成する工程(S16)と、を有し、光電変換素子130を形成する工程(S4)におけるアライメント(A4)およびマイクロレンズ600を形成する工程(S16)におけるアライメント(A16)を、分離領域110を形成する工程(S1)で形成されたアライメントマーク(AM1)を基準にして行う。

(もっと読む)

光検出装置

【課題】光の検出範囲が狭くなることを抑制する。

【解決手段】入射する光の照度に応じて値が設定される第1の光データ信号及び第2の光データ信号を出力する光検出回路と、第1の光データ信号及び第2の光データ信号が入力され、第1の光データ信号及び第2の光データ信号を用いて演算処理を行うアナログ演算回路と、アナログ演算回路における演算処理として、第1の光データ信号及び第2の光データ信号の加算処理を行うか、第1の光データ信号及び第2の光データ信号の減算処理を行うかを切り替える切替回路と、を具備する。

(もっと読む)

半導体装置とその駆動方法

【課題】1フレーム期間以上のデータの保持が可能であり、少ない素子数で差分演算を行うことができるイメージセンサを提供する。

【解決手段】マトリクス状に配置された複数の画素にフォトセンサを設け、該画素は1フレーム期間以上にわたってデータ保持部に電荷を蓄積し、該データ保持部に蓄積された電荷によってフォトセンサの出力を変化させる。データ保持部の書き込みスイッチ素子としては、リーク電流の小さい(1×10−14Aより十分に小さい)トランジスタを用いる。リーク電流の小さいトランジスタとしては、酸化物半導体層にチャネルが形成されるトランジスタが挙げられる。

(もっと読む)

固体撮像装置

【課題】高輝度被写体の撮像時に、リセットトランジスタ及び増幅トランジスタが損傷せず、かつ、黒焼付き現象が発生しない固体撮像装置を提供する。

【解決手段】固体撮像装置は、半導体基板と、複数存在し、各々が単位画素を構成する第1電極と複数の第1電極上に形成された光電変換膜と光電変換膜上に形成された第2電極とを有する光電変換部と、複数の第1電極と電気的に接続され、半導体基板上に設けられた電荷蓄積領域と、電荷蓄積領域をドレイン領域とする、若しくは、電荷蓄積領域をドレイン領域と電気的に接続したリセットトランジスタとを備え、リセットトランジスタのソース領域606及びドレイン領域607の少なくともいずれかは、リセットトランジスタのゲート酸化膜605の下方に伸長しかつゲート酸化膜605に接しないパンチスルーパス608a、608bを有している。

(もっと読む)

固体撮像素子、固体撮像素子の製造方法、及び、電子機器

【課題】飽和電荷量の向上が可能な固体撮像素子を提供する。

【解決手段】半導体基体51の表面51A側に形成された第1フォトダイオードPD1と、裏面51B側に形成された第2フォトダイオードPD2を備える。そして、第2フォトダイオードPD2を構成する第1導電型半導体領域59と第2導電型半導体領域58との接続面の不純物濃度が、第2導電型半導体領域58の第1導電型半導体領域59と反対側の層との接続面の不純物濃度以上である固体撮像素子50を構成する。

(もっと読む)

放射線検出装置および放射線撮像システム

【課題】スイッチ素子であるTFTに裏面光の入射を抑え、光電変換素子に裏面からの光を効率よく照射可能な構成とする。

【解決手段】絶縁基板の第1面上に配置された第1の電極と、該第1の電極上に配置された第2の電極と、前記第1の電極と前記第2の電極との間に配置された半導体層と、により構成された電磁波を電気信号に変換する変換素子と、該変換素子に接続されたスイッチ素子と、を有する画素が複数設けられた電磁波検出装置であって、前記第1の電極は前記絶縁基板の前記第1面と対向する第2面側に配置された光源から発せられた光を透過する光透過性導電材料によって構成され、且つ、前記スイッチ素子は前記光源からの前記光が前記スイッチ素子へ入射することを防ぐ遮光部材を有することを特徴とする。

(もっと読む)

固体撮像装置、電子機器

【課題】固体撮像装置において、ゴーストなどの発生を抑制して、画像品質を向上させる。

【解決手段】入射光Hを受光する複数の画素PXが半導体基板101の上面に配列されているセンサ基板100と、前記センサ基板の上面に下面が対面しており、前記入射光が透過する透明基板300と、前記透明基板の上面と前記センサ基板の上面との間のいずれかの位置に設けられており、前記入射光が透過する回折格子601とを有し、前記回折格子は、前記半導体基板の上面にて前記複数の画素が配列された画素領域PAに前記入射光が入射し回折されることで生ずる反射回折光を回折するように形成する。

(もっと読む)

41 - 60 / 2,088

[ Back to top ]