Fターム[5B125CA06]の内容

リードオンリーメモリ (43,397) | 目的、効果 (6,321) | 小型化、高密度化、高集積化 (714)

Fターム[5B125CA06]の下位に属するFターム

共通化、兼用化 (140)

Fターム[5B125CA06]に分類される特許

1 - 20 / 574

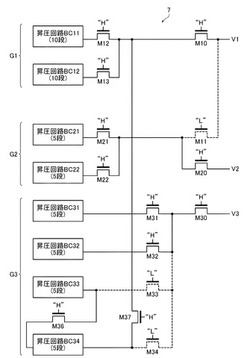

電圧生成回路

【課題】回路面積を低減させることのできる電圧生成回路を提供する。

【解決手段】一の実施の形態に係る電圧生成回路は、第1の電圧値の第1電圧を発生させる第1の昇圧回路と、第2の電圧値の第2電圧を発生させる複数の第2の昇圧回路を含む第2昇圧回路群とを有する。複数の第2の昇圧回路は、第1の状態から第2の状態に移行する際に互いに直列に接続され第1昇圧回路とともに第1電圧を発生可能に構成されている。

(もっと読む)

半導体記憶装置

【課題】微細化に対して有利な半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、複数のメモリセルが配置されるメモリセルアレイ11と、前記複数のメモリセルのデータをラッチし、前記メモリセルアレイのデータの入力または出力(I/O)ごとに分割して配置される複数のアドレス領域(IO<0>領域〜IO<7>領域)と、前記複数のアドレス領域に対応して配置され、それぞれが前記複数のアドレス領域と電気的に直列に接続される内部バス配線20と、前記内部バス配線のデータ転送を制御する制御回路15とを具備する。

(もっと読む)

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

【課題】フローティングゲートへの電荷の蓄積と消去を容易に行え、またフローティングゲートの電荷を消去する場合にメモリセルの閾値を容易に制御できる、不揮発性半導体メモリ素子を提供する。

【解決手段】フローティングゲートへの電荷の蓄積時に、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットエレクトロンを半導体基板中に発生させ、フローティングゲートに電荷を注入する。また、フローティングゲートの電荷の消去時には、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットホールを発生させ、該ホットホールにより蓄積された電荷を消去する。また、フローティングゲートの電荷の消去時には、メモリセルのコントロールゲートとソース間の閾値が所望の値になるように制御しながら、電荷を消去する。

(もっと読む)

多数の外部電力供給部を有する不揮発性半導体メモリ

【課題】メモリ動作を可能にするために、低いまたはより低い電圧入力をより高い電圧に変換することは、変換器効率を低下させ、チャージポンプ回路のサイズおよび複雑さを増加させる。

【解決手段】メモリデバイスはデータを記憶するためのフラッシュメモリなどのコアメモリを含む。メモリデバイスは、フラッシュメモリに電力を供給するのに使用される第1の電圧を受け取るために第1の電力入力部を含む。さらに、メモリデバイスは、第2の電圧を受け取るために第2の電力入力部を含む。第2の電圧を受け取り、1つまたは複数の内部電圧を引き出すように構成された電力管理回路をメモリデバイスは含む。電力管理回路は内部電圧をフラッシュメモリに供給または伝達する。電力管理回路(例えば電圧変換器回路)によって発生され、コアメモリに供給される様々な内部電圧は、コアメモリ中のセルに関する読出し/プログラム/消去などの動作を可能にする。

(もっと読む)

半導体記憶装置

【課題】 メモリアレイ上のワード線に印加される電界を低減し、チップ面積を低減可能な半導体記憶装置を提供する。

【解決手段】 フラッシュメモリ100は、メモリアレイ110と、メモリアレイ110の行方向の端部に配置され、アドレス信号に基づきメモリアレイ内の特定のメモリブロックを選択し、選択されたメモリブロックに選択信号を出力するワード線デコーダ120と、

メモリアレイ110Aと110Bの間に配置され、選択信号に基づきメモリセルに供給される動作電圧のスイッチングを行うスイッチ回路、および選択信号を昇圧する昇圧回路を含むワード線駆動回路130とを有する。ワード線デコーダ120は、選択信号を搬送する配線WR(i)を有し、配線WR(i)は、ワード線駆動回路130のスイッチ回路に接続される。

(もっと読む)

半導体記憶装置

【課題】ゲート面積に依存するトランジスタばらつきを抑制し、読み出し動作を高速化した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ロウ方向に延びるワード線WL、カラム方向に延びる複数のビット線BL0,BL1,BL2で構成されたビット線グループ、並びに、トランジスタからなりワード線及びビット線グループの交差部に設けられたメモリセル、を有するメモリセルアレイと、ビット線を介してメモリセルからデータを読む読み出し回路とを備え、メモリセルは、トランジスタのソース又はドレインを、ビット線グループに属する複数のビット線BL0,BL1,BL2のいずれとも接続しないか又はいずれか1本とだけ接続するかの異なる接続状態を有し、トランジスタのゲートとなるアクティブ領域AAは、ビット線グループの複数のビット線BL0,BL1,BL2の配置領域及び各ビット線間のスペースに連続的に形成されている

(もっと読む)

半導体記憶装置及びデータ読み出し方法

【課題】レイアウト面積の増大を抑制することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置1は、2つのメモリセルアレイ10U,10Dと、それら2つのメモリセルアレイ10U,10Dで共有されるセンスアンプ30と、メモリセルアレイ10U,10Dからのデータ読み出しを制御する制御回路50とを有している。メモリセルアレイ10Uは、m本のワード線WL0U〜WLmUと、n本のビット線BL0U〜BL15Uと、これらワード線WL0U〜WLmUとビット線BL0U〜BL15Uの交差点に設けられたメモリセルMCと、ビット線BL0U〜BL15Uとダミーワード線DWLUとの交差点に設けられたダミーセルDMCとを有している。制御回路50は、一方のメモリセルアレイからデータを読み出す場合に、他方のメモリセルアレイのダミーワード線を活性化してダミーセルによりセンスアンプ30のリファレンスレベルを生成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】周辺回路の面積を縮小する。

【解決手段】

複数のメモリブロックの各々には、基板に対し垂直な方向に延びるように複数のメモリストリングが配列される。各メモリストリングは、複数のメモリトランジスタ及びダミートランジスタを直列接続してなる。ドレイン側選択ゲート線及びソース側選択ゲート線は、メモリブロックが選択されるときには転送トランジスタが導通することにより電圧を制御回路から供給される一方、メモリブロックが非選択とされるときは転送トランジスタが非導通状態となることによりフローティング状態とされる。ダミーワード線は、メモリブロックが選択されるときには第1の転送トランジスタが導通することにより制御回路から電圧を供給される一方、メモリブロックが非選択とされるときは第1の転送トランジスタとは別の第2の転送トランジスタにより電圧を供給される。

(もっと読む)

不揮発性半導体記憶装置

【課題】容量素子が占有する回路面積の増大を抑制する。

【解決手段】メモリストリングは、複数の第1導電層、メモリゲート絶縁層、及び半導体層を有する。複数の第1導電層は、半導体基板に対して実質的に垂直方向に所定ピッチをもって配列され、メモリトランジスタのゲートとして機能する。半導体層は、複数の第1導電層と共にメモリゲート絶縁層を一方の側面で挟み、半導体基板に対して実質的に垂直方向に延び、メモリトランジスタのボディとして機能する。第1キャパシタは、複数の第2導電層を有する。複数の第2導電層は、半導体基板に対して実質的に垂直方向に所定ピッチをもって配列され、第1キャパシタの電極として機能する。制御回路は、複数の第1導電層に印加される電圧に応じて、複数の第2導電層の各々に印加する電圧を制御し、これにより第1キャパシタの容量を変化させる。

(もっと読む)

半導体記憶装置

【課題】信頼性を向上することが出来る半導体記憶装置を提供すること。

【解決手段】第1メモリセルMCと、第1ワード線WLと、第1ビット線BLに流れる第1電流を検知する第1センスアンプ12と、を具備し前記第1センスアンプ12は、第1供給部と、検出器と、前記検出器からの出力をカウントするカウンタと、を含み、前記カウンタは、第2供給部(22、31、33)と、第2蓄積部と、検知部とを具備する。

(もっと読む)

メモリ装置およびメモリ装置の制御方法

【課題】メモリセル31が劣化した場合にも、誤り訂正回路20の回路面積を増大させることなく誤り訂正を行うことができるメモリ装置2を提供する。

【解決手段】実施の形態のメモリ装置2は、メモリ部30と、制御部11と、補正部41と、誤り検出訂正部40とを具備する。メモリ部30は、データを記憶する複数のメモリセル31からなる。制御部11は、電荷量に対応した閾値電圧を読み出すためにメモリセル31にHB読出電圧HVと、補間読出電圧AVと、を印加する制御を行う。補正部41は読み出された、閾値電圧Vthから決定されたビットデータを反転する。誤り検出訂正部40は、補正部41で反転されたビットデータを含めた所定長のデータ列を、硬判定復号符号により復号処理を行う。

(もっと読む)

不揮発性半導体記憶装置

【課題】高集積化を図ることができる不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、セルの書き込みにおいて、制御装置は複数の第2の選択ゲートトランジスタに第1電位を与えた後、第1電位よりも低い第2電位を与える。複数のビット線のうち、書き込み不十分のセルに第3電位を与え、書き込み終了に間近のセルに第3電位より高い第4電位を与え、書き込みが終わったセルに第4電位より高い第5電位を与える。制御装置は、第2電位を与えた後、複数のワード線のうち選択されたワード線に書き込み電位を与え、第1電位は、第2の選択ゲートトランジスタをオンすることにより第3電位をNANDストリングに転送する電位であり、第2電位は、第3電位をNANDストリングに転送した後、前記第2の選択ゲートトランジスタをオフする電位である。

(もっと読む)

不揮発性半導体記憶装置

【課題】 不揮発性半導体記憶装置の信頼性を、より向上させる技術が望まれている。

【解決手段】 閾値レベルの相違によって少なくとも4つのデータ状態が定義され、複数のデータ状態の各々に、複数ビットで構成される値が割り当てられるメモルセルがメモリ部に複数配置される。コントローラが、メモリセルの各々が記憶する複数ビットのうち、少なくとも1つのビットを、「正常」及び「異常」のいずれかの状態を表すエラー訂正ビットとし、他のビットを、データを記憶するためのデータビットとする。複数のデータ状態を、閾値レベルの大きさの順番に並べたとき、連続する4つのデータ状態のうち、閾値レベルが最小及び最大のデータ状態のエラー訂正ビットに「正常」を割り当て、閾値レベルが中間の2つのデータ状態のエラー訂正ビットに「異常」を割り当てる。周期的にメモリセルのエラー訂正ビットのデータを読み出し、読み出された値が「異常」である場合には、当該メモリセルのエラー訂正ビットを「正常」に再設定する。

(もっと読む)

情報処理装置及び半導体記憶装置

【課題】製造コストの低減に対して有利な情報処理装置及び半導体記憶装置を提供する。

【解決手段】実施形態によれば、ホスト装置と、前記ホスト装置にバスを介して接続された半導体記憶装置とを備える情報処理装置であって、前記ホスト装置は、メインメモリを備え、前記半導体記憶装置は、第1の論物変換テーブル及びデータを格納する不揮発性半導体メモリと、前記第1の論物変換テーブルの一部である第2の論物変換テーブルを格納する記憶部と、前記第2の論物変換テーブルを参照し前記不揮発性半導体メモリにアクセスする制御部とを備え、前記第1の論物変換テーブルの少なくとも一部が前記メインメモリ上にコピーされ、前記第2の論物変換テーブルに前記制御部がアクセスする論理アドレス又は物理アドレスが登録されていない場合、前記メインメモリ上の第3の論物変換テーブルの一部が前記第2の論物変換テーブルにコピーされる。

(もっと読む)

不揮発性半導体記憶装置

【課題】正確に書き込み動作を行うことができる不揮発性半導体記憶装置を提供する。

【解決手段】

複数の素子分離絶縁膜は、半導体層中に形成され、第1方向を長手方向とする。複数の素子形成領域は、素子分離絶縁膜により分離して形成される。素子形成領域にはメモリストリングが形成される。複数の素子形成領域群が素子形成領域により構成される。メモリセルアレイは、第1方向と直交する第2方向において、前記素子形成領域群の間隔が前記素子形成領域群の中の前記素子形成領域の間隔より大きくされている。制御回路は、前記メモリセルアレイに対する書き込み動作を、前記素子形成領域群ごとに実行する。

(もっと読む)

不揮発性半導体記憶装置

【課題】誤読み出しを抑制し、かつ高速性の向上を図る。

【解決手段】不揮発性半導体記憶装置は、2値または多値で書き込み可能なメモリセルを有する第1および第2メモリブロックBLKと外部からのコマンドに応じてデータの書き込みおよび読み出しを行う制御回路8とを具備する。制御回路は、読み出し対象ブロックが第1メモリブロックである場合、第1フラグに応じて第1メモリブロックが2値であるか多値であるかを判定してその第1判定結果を記憶し、第1判定結果によって第1メモリブロックを2値または多値で読み出し、読み出し対象ブロックが第1メモリブロックから第2ブロックに変更された場合、第1判定結果を消去し、第2フラグに応じて第2メモリブロックが2値であるか多値であるかを判定してその第2判定結果を記憶し、第2判定結果によって第2メモリブロックを2値または多値で読み出す。

(もっと読む)

半導体記憶装置

【課題】 ビット線選択回路の小型化を図るとともにビット線の駆動時間を高速に行うことができる半導体記憶装置を提供する。

【解決手段】 フラッシュメモリ10は、セルユニットNUが行列状に複数配置されたメモリアレイ100と、セルユニットNUに接続されたビット線を選択するビット線選択回路200とを有する。ビット線選択回路200は、偶数ビット線GBL_e、奇数ビット線GBL_oをセンス回路に選択的に接続するための選択トランジスタSEL_e、SEL_o、BLSを含む第1の選択部210と、偶数ビット線GBL_eおよび奇数ビット線GBL_oに選択的にバイアス電圧を印加するためのバイアストランジスタYSEL_e、YSEL_oとを含む第2の選択部220とを有する。第2の選択部220のバイアストランジスタYSEL_e、YSEL_oは、記憶素子と共通のウエル内に形成される。

(もっと読む)

メモリストリングにダイオードを有する3次元アレイのメモリアーキテクチャ

【課題】信頼でき、非常に小型の3次元集積回路メモリ用の構造を低い製造コストで提供する。

【解決手段】3次元アレイは第1の端部と第2の端部を含む2つの端部を有し、第1の端部と第2の端部の一方はビット線BLに接続され、第1の端部と第2の端部の他方はソース線CSLに接続される不揮発性メモリセルのNANDストリングのスタック1412、1413、1414と、ビット線BL及びソース線SLの一方をメモリセルのストリング1412、1413、1414に接続させるダイオード1492を有する。

(もっと読む)

制御信号発生回路およびそれを用いた半導体装置

【課題】半導体装置の制御に好適な制御信号発生回路を提供する。

【解決手段】ジョンソンカウンタ31は、フリップフロップFF1〜FF4およびゲート回路41〜44を含み、順次入力されるスタート信号ST1〜ST4に応答してそれぞれ制御信号C1〜C4を「H」レベルにした後、順次入力されるストップ信号SP1〜SP4に応答してそれぞれ制御信号C1〜C4を「L」レベルにする。したがって、多数のフリップフロップを用いることなく、所望の時間間隔で制御信号C1〜C4を順次「H」レベルにし、順次「L」レベルにすることができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去動作の実行単位を小さくすると共に正確な読出動作を実現可能な不揮発性半導体記憶装置を提供する。

【解決手段】一態様に係る不揮発性半導体記憶装置は、複数のメモリストリング、複数のメモリブロック、複数のソース線、及び制御回路を有する。複数のメモリストリングは、積層された複数のメモリトランジスタを含む。複数のメモリブロックは、複数のメモリストリングを含む。複数のソース線は、複数のメモリストリングそれぞれに接続される。制御回路は、複数のソース線に供給する信号を制御する。複数のメモリストリングは、各々、半導体層、電荷蓄積層、及び導電層を有する。制御回路は、メモリトランジスタに対する動作の種類に基づいて、複数のソース線を電気的に共通接続するか否かを切り替える。

(もっと読む)

1 - 20 / 574

[ Back to top ]