Fターム[5C006AF82]の内容

Fターム[5C006AF82]の下位に属するFターム

階調電圧発生用D/A変換 (966)

Fターム[5C006AF82]に分類される特許

41 - 60 / 334

データ処理装置

【課題】容易にEMIノイズを大きく低減することのできるデータ処理装置を実現する。

【解決手段】データ処理装置(201)は、サンプリング回路(50、50a〜50l)によってデータバス(30)を構成する各データライン(30a〜30c)のデータ(D0、D1、D2)をサンプリングした後、次のデータ(D0、D1、D2)が各データライン(30a〜30c)に供給される前に、各データライン(30a〜30c)の2本以上どうしを互いに短絡させるスイッチ(6)を備えている。

(もっと読む)

半導体装置

【課題】画素部や信号線駆動回路が形成された基板と、ドライバICとの接続配線数を低減させる。

【解決手段】信号線駆動回路は第1乃至第3のトランジスタを有し、第1乃至第3のトランジスタは第1乃至第3の信号線と電気的に接続している。第1乃至第3の信号線は画素部へ延びている。第1乃至第3のトランジスタは共通して、ドライバICの第1端子と電気的に接続している。このような構成により、接続配線数を1/3に低減することができる。

(もっと読む)

液晶表示素子及びその駆動方法

【課題】ランプ信号を用いることなくDA変換を行う構造とすることでランプ信号の波形の変形による表示画像の不具合を解消する。

【解決手段】1H内において、表示する映像信号の画素値と一定周期のクロックを計数するカウンタのカウンタ値とを比較し、画素値とカウンタ値とが一致した時に、データ線VDjの電位がそれまでのaからbに変化する。蓄積ゲートGSは、ゲート線AGiの電圧が、電位aよりも低い電位cから電位よりも高い電位dに変化した時に、VDjから一定量の電荷を転送されて蓄積する。転送ゲートGTは、ゲート線TGiの電圧が、電位cよりも低い電位eから電位cよりも高い電位fに変化した時に、上記の蓄積電荷を保持容量CSに転送して保持させる。データ線VDjの電位がbに変化するまで、上記の蓄積と転送の動作を巡回的に繰り返し、その繰り返し回数に応じた電荷量を保持容量CSに保持する。

(もっと読む)

画像処理装置、画像処理方法、及び、プログラム

【課題】出力画像の色を精度良く補正して表示する。

【解決手段】画像処理装置100において、制御部105は白色色度座標を取得して三刺激値に変換する。制御部105は白色表示時に表示部108によるRGBの各光出力強度が同じになるようにRGBそれぞれに対応する補正係数を求めて色補正回路125に入力する。色補正回路125は白色表示時にディスプレイ132が所定の白色を出力するように、入力された補正係数を用いてRGBの各映像信号の強度を補正する。

(もっと読む)

表示装置及び携帯機器

【課題】表示装置において、信号線の数が少ない表示装置及びそれを備えた携帯機器を提供する。

【解決手段】表示装置の制御手段2は、記憶手段3に記憶されたLED電流データを読み出してバックライト駆動手段4を制御すると共に、入力情報10及び映像信号11に基づいてLCDパネル6を制御するものである。バックライト駆動手段4は、LED電流データに応じた電流をバックライト5に供給するものである。制御手段2は、バックライト駆動手段4に出力するLED電流データと、LCDパネル6に出力する画像データとを同一の信号線8を介して伝送し、信号線8を伝送される信号からLED電流データを選択する選択信号29とLCDパネル6中の駆動回路に出力する制御信号30とを同一の信号線で伝送する。

(もっと読む)

表示パネル駆動回路、表示装置、及び電子機器

【課題】表示パネルの画素の残留電荷を適切に放電させることができる表示パネル駆動回路を提供する。

【解決手段】表示パネル(液晶パネル21)を駆動する表示パネル駆動回路1は、各画素を駆動するアクティブ素子のソース線に対して表示階調に対応した駆動電圧を印加するか否かを切替えるソース線駆動回路22と、アクティブ素子のゲート線に対してアクティブ素子をオン/オフさせるゲート電圧を印加するゲート線駆動回路23と、電源オフの指令が入力された場合、駆動電圧と表示パネル(液晶パネル21)の共通電極25の電位とを基準電位に制御するとともに、各々のソース線に対して駆動電圧を印加し、且つ各々のゲート線に対してアクティブ素子をオンさせる制御をした後、全てのソース線に対して一斉に駆動電圧の印加を停止する制御をしてから電源オフする制御部3とを備える。

(もっと読む)

画像表示装置及びその制御方法

【課題】液晶表示装置において動きのある映像を表示する際の表示品質のさらなる改善を図る。

【解決手段】画像表示装置は、液晶パネルと、バックライトと、前記バックライトの発光を制御する制御部と、を備える。制御部は、入力される映像信号を解析して、映像の動きを検出し、検出された動きが等速度又は等加速度の動きである場合の発光時間は短く、検出された動きが等速度又は等加速度の動きでない場合の発光時間は長くなるように、前記バックライトの発光時間を設定する。さらに、制御部は、発光時間が短くなるほど発光強度が大きくなるように、設定された発光時間に応じて前記バックライトの発光強度を変更するとよい。

(もっと読む)

表示装置

【課題】1つの表示装置で、アナログ表示(動画像表示)とデジタル表示(静止画像表示)という2種類の表示モードに対応することを可能にすると共に、表示システムの大幅な低消費電力を図る。

【解決手段】 アナログ表示を行う第1の表示回路と、デジタル表示を行う第2の表示回路を備え、アナログ表示を停止するように切り換えるときには、外部から入力されるモード設定信号DHに基づき、ドレイン信号線61と第1の表示回路との接続を切ると共に、モード設定信号DHを遅延することにより生成される停止制御信号LAに応じて、不要な回路(DAコンバータ310、演算増幅器311、タイミングコントローラ305)への電源供給を停止する。

(もっと読む)

表示パネルドライバ及びそれを用いた表示装置

【課題】駆動電圧の極性切替(極性反転)が可能な表示パネルドライバの消費電力を低減する表示パネルドライバを提供する。

【解決手段】本発明による表示パネルドライバは、表示パネルの画素に接続された第1データ線及び第2データ線を駆動する出力段として、第1電源範囲で駆動する第1出力段24A及び第4出力段24Bを利用する第1モードと、第1電源範囲よりも広い第2電源範囲で駆動する第2出力段73A及び第3出力段73Bを利用する第2モードとを切替える第1スイッチ回路50と、第2モードの間に、正極性駆動電圧と負極性駆動電圧の出力先となるデータ線6を切替える第2スイッチ回路30とを備える。又、第1出力段24Aは、ウェルが他のNMOSトランジスタから分離され、バックゲートがソースに接続された第1プルダウン出力トランジスタMN18を備える。

(もっと読む)

表示装置及びプログラム

【課題】発進可能な状態であることを報知することについての製造コストを抑えた表示装置及びプログラムを提供する。

【解決手段】表示装置11は、電動バイク1の状態を示す計測値を所定の方法で表示する表示手段としての表示部114と、表示部114を制御する制御手段としての制御部111と、を備える。表示装置11の制御部111は、電動バイク1が発進可能な状態になった後に、前記電動バイク1が発進可能な状態であることを前記所定の方法とは異なる方法で表示部114に表示させる。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】高速動作に対応可能とし、消費電力を抑制可能とし、差動段を単一導電型に簡素化した構成においても、充電及び放電における出力電圧波形の対称性を実現する。

【解決手段】第1の差動対111、112と、第1のカレントミラー130と、第2のカレントミラー140と、第1の浮遊電流源回路150と、第2の浮遊電流源回路160を備えた差動入力段と、第1導電型の第1のトランジスタ101と、第2導電型の第2のトランジスタ102と、を備えた出力増幅段110と、第1及び第2の電流源121、123と、第3のトランジスタ103と、第4のトランジスタ105と、第3及び第4の電流源122、124と、第5のトランジスタ104と、第6のトランジスタ106とを備えた電流制御回路120とを含む。

(もっと読む)

駆動装置及び電子機器

【課題】液晶表示パネルにおける実装領域の面積比率を下げ、面積比率が下がることにより大きくなるノイズの影響を少なくした駆動装置を提供する。

【解決手段】複数の駆動回路をカスケード接続し、画像データ及び該画像データの取り込みタイミング信号をカスケード接続した駆動回路を介して伝播させる。

(もっと読む)

立体映像表示システム及び液晶表示装置

【課題】交流駆動周波数を高周波数化した安定した映像表示と、画素回路の特性の相違に起因する誤差による輝度異常の抑制と、必要最低限なデータ転送帯域で安定した立体映像表示動作とを行う。

【解決手段】反転回路101、DAC102及びソースドライバ103は、各組の2本の列信号線D1及びD2のそれぞれに、右目用映像信号及び左目用映像信号のうち一方の映像信号から得た正極性映像信号と負極性映像信号とを同時に供給することを1水平走査期間内で順次に行うと共に、1フレーム期間毎に正極性映像信号と負極性映像信号とを切り替え、かつ、1フレーム期間毎に2本の列信号線のそれぞれに正極性映像信号及び負極性映像信号を切り替えて供給する。各画素105は、2つの信号保持容量を有し、各々に映像信号電圧を保持した後1/2フレーム期間内で交互に読み出して画素電極に供給する。

(もっと読む)

表示装置

【課題】静止画像を低消費電力で表示することが可能な半導体装置を提供する。

【解決手段】静止画像を表示することのできる半導体表示装置を搭載した半導体装置において、画素部を形成する基板上にメモリ部を実装する。実装の方法は、画素部を形成する基板上にメモリ部を形成するか、またはメモリ部を備えたスティックドライバを用いる。そのようなメモリ部に格納された画像データを用いて静止画像を表示することにより、半導体表示装置の外部からは簡単な制御信号を入力するだけで静止画像を表示することが可能となり、低消費電力で静止画像を表示することのできる半導体表示装置および半導体表示装置を搭載した半導体装置が提供される。

(もっと読む)

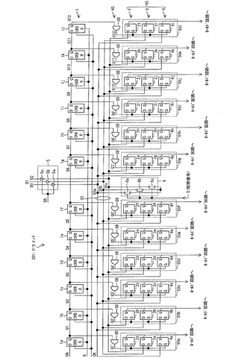

二段式デジタル/アナログ変換器及び液晶ディスプレイのソースドライバ

【課題】高解像度の液晶ディスプレイのソースドライバに用いられる新規なDAC構成を提供する。

【解決手段】二段式デジタル/アナログ変換器及び液晶ディスプレイのソースドライバである。ソースドライバは、二段式デジタル/アナログ変換器を含む。この二段式デジタル/アナログ変換器は、Mビットデジタル入力コードによってアナログ電圧を出力する。ソースドライバは、1ビットシリアル電荷再配分デジタル/アナログ変換器と電圧セレクタを含む。1ビットシリアル電荷再配分デジタル/アナログ変換器は、高参考(参照)電圧を受信できる高参考電圧入力ノードと、低参考電圧を受信できる低参考電圧入力ノードとを有する。電圧セレクタは、Mビットデジタル入力コードの少なくとも一部によって高参考電圧と低参考電圧とを所定の電圧に設定する。

(もっと読む)

液晶装置および液晶装置の制御方法

【課題】使用者に調整作業を行わせることなく液晶への直流成分の印加を抑え、フリッカーの発生を抑える。

【解決手段】スタートパルスDybをタイミングTで出力している状態で、画素が負極性電圧を保持している時の明るさと正極性電圧を保持している時の明るさの差が閾値以上の場合、スタートパルスDybをタイミングTよりも遅いタイミングで出力する。スタートパルスDybのタイミングを変更してから所定時間内において、画素が負極性電圧を保持している時の明るさと正極性電圧を保持している時の明るさの差が減少した場合、スタートパルスDybをタイミングTよりも早いタイミングで出力し、明るさの差が増加した場合、スタートパルスDybの出力タイミングをそのままとすることにより、画素が負極性電圧を保持している時の明るさと正極性電圧を保持している時の明るさの差を予め定められた差以下に減少させる。

(もっと読む)

液晶装置、液晶装置の駆動方法及び電子機器

【課題】フリッカー等の表示不具合の発生を抑制して表示品位の向上を図ることが可能な液晶装置、液晶装置の駆動方法及び電子機器を提供する。

【解決手段】素子基板10の液晶層の側に設けられた第1配向膜13と、対向基板20の液晶層の側に対向電極22に接して設けられた第2配向膜23と、画素電極12と第1配向膜13との間に設けられた、液晶層よりも膜厚が薄く、かつ、液晶層よりも高比抵抗の、SiO2からなる誘電体膜38と、を備え、対向電極22には、スイッチング素子40の寄生容量に起因するフリッカーを低減するように設定された対向電極電位が印加され、画素電極12には、対向電極電位を基準として高位の電圧を正極性、低位の電圧を負極性としたときに、正極性の電圧と負極性の電圧とが交互に印加され、正極性の電圧が印加される第1の期間の長さが負極性の電圧が印加される第2の期間の長さに比べて長く設定される。

(もっと読む)

液晶装置、液晶装置の駆動方法及び電子機器

【課題】フリッカー等の表示不具合の発生を抑制して表示品位の向上を図ることが可能な液晶装置、液晶装置の駆動方法及び電子機器を提供する。

【解決手段】素子基板10の液晶層の側に設けられた第1配向膜13と、対向基板20の液晶層の側に設けられた第2配向膜23と、を備え、第1配向膜13における第1プレチルト角が、第2配向膜23における第2プレチルト角に比べて小さく設定されており、対向電極22には、スイッチング素子40の寄生容量に起因するフリッカーを低減するように設定された対向電極電位が印加され、画素電極12には、対向電極電位を基準として高位の電圧を正極性、低位の電圧を負極性としたときに、正極性の電圧と負極性の電圧とが交互に印加され、正極性の電圧が印加される第1の期間の長さが負極性の電圧が印加される第2の期間の長さに比べて短く設定される。

(もっと読む)

液晶装置、電子機器、及び液晶装置の駆動方法

【課題】液晶装置において、消費電力を抑制しつつ長い書込期間を確保する。

【解決手段】液晶装置1を提供する。液晶装置1は、表示すべき階調に応じた大きさのデ

ータ信号を生成しデータ信号生成回路211と、プリチャージ信号Vpreを生成するプ

リチャージ信号生成回路20とを備え、プリチャージ期間Preではプリチャージ信号V

preをデータ線103及び105に供給し、データ期間Daではデータ信号をデータ線

103に供給する。ただし、データ信号生成回路211は、データ信号の極性を所定数の

ドット毎に反転する。また、液晶装置1は、データ線105へのプリチャージ信号Vpr

eの供給の開始からデータ線105の電圧が比較電圧に到達するまでの時間を計測し、計

測した時間に基づいて、データ期間Daにおいて、所定数のドットの各々に対応するデー

タ信号が均等な時間だけ生成されるようにデータ信号生成回路211を制御する。

(もっと読む)

表示装置

【課題】映像信号線駆動回路に入力する情報を抑制すること。

【解決手段】制御部と、少なくとも1つの画素回路と前記少なくとも1つの画素回路に接続される映像信号線を備えた表示パネルと、映像信号線駆動回路を有する表示装置において、前記制御部は、前記映像信号線が前記画素回路のうち1つに印加すべき階調電位の値と、前記階調電位に基づくプリチャージ電位の値との相違データを取得する相違取得回路を有し、前記映像信号線駆動回路は、前記階調電位の値および前記相違データに基づいてプリチャージ電位を演算する演算部と、前記演算部の演算結果に基づいて、前記プリチャージ電位と前記階調電位とを順に前記映像信号線に供給する映像信号線出力部と、を含むことを特徴とする。

(もっと読む)

41 - 60 / 334

[ Back to top ]