Fターム[5C006BC03]の内容

Fターム[5C006BC03]に分類される特許

61 - 80 / 1,927

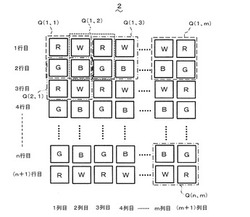

液晶表示装置

【課題】液晶表示装置において、サブピクセルに駆動信号を送る配線数を削減し、透過率を向上させる。

【解決手段】サブピクセルが行及び列方向に複数配列され、赤、緑、青、白の2行2列の4つのサブピクセルR、G、B、Wの混色によって1ピクセルを構成する液晶パネル2と、サブピクセルの駆動信号を生成する信号制御部を備える。信号制御部は、行及び列方向において1行及び1列ずつ重なり合って隣接する2行2列の4つのサブピクセル毎に、1ピクセルQ(1、1)、Q(1、2)・・Q(n、m)を構成し、それらのピクセルが画像情報の1ピクセルずつを再現するように駆動信号を生成する。行及び列方向のサブピクセル数が、各々行及び列方向において表示すべきピクセル数に1つ足した個数で足りることになり、配線数を大幅に低減することができる。また、透過率を下げる要因になる配線の本数を低減できることから液晶パネルの透過率の向上が容易になる。

(もっと読む)

タッチセンサ内蔵型表示装置とその駆動方法

【課題】表示パネルのピクセルに接続された信号配線からタッチセンサに印加されるノイズを最小化する。

【解決手段】ピクセルにデータ電圧を供給するデータラインと、ピクセルにスキャンパルスを供給するゲートライン、互いに交差されその交差部に相互容量が形成されたTxライン及びRxラインを含む表示パネルと、ディスプレイ期間の間、データラインにアナログビデオデータ電圧を供給しタッチセンサ駆動期間の間、データラインの電圧を特定直流電圧に同一に維持させるディスプレイデータ駆動回路と、ディスプレイ期間の間、アナログビデオデータ電圧に同期するスキャンパルスを前記ゲートラインに順次供給するディスプレイスキャン駆動回路と、タッチセンサ駆動期間の間、Txラインに駆動パルスを順次供給するタッチセンサ駆動回路と、タッチセンサ駆動期間の間Rxラインを経由し相互容量からタッチ信号を受信するタッチセンサ読み出し回路とを含む。

(もっと読む)

電気光学装置及び電子機器

【課題】アクティブマトリクス駆動方式の電気光学装置において、相展開数の増加による画像信号線の増加という条件下で、画像信号中の高周波のクロックノイズ等の発生を低減する。

【解決手段】液晶装置(200)は、一対の基板間に挟持された液晶層と、基板(1)にマトリクス状に設けられた画素電極(11)と、これをスイッチング制御するTFT(30)とを備える。さらにデータ線駆動回路(101)にクロック信号を供給する配線(CLX,CLX’)と、データ線駆動回路(101)及び配線(CLX,CLX’)を囲むように配設されたシールド線(80’)と、シールド線(80’)の外側に配設された画像信号線(VID1〜VID12)を備える。

(もっと読む)

表示装置

【課題】画素回路に含まれるトランジスタに生じるゲート・ソース間の寄生容量が異なる。

【解決手段】表示装置であって、それぞれ、トランジスタと、前記トランジスタに接続された画素電極と、該画素電極に対向して配置された基準電極と、を含み、マトリクス状に配置された複数の画素回路と、対応する前記複数の画素回路にそれぞれ接続される複数のデータ線と、対応する前記複数の画素回路にそれぞれ接続される複数のゲート線と、それぞれ、第1の順序または第2の順序で、順に2水平期間以上の水平期間にハイ電圧となるゲート信号を出力する、該ゲート信号が出力される水平期間に応じた数の複数のゲート回路と、前記各ゲート回路を制御し、前記複数のゲート線を走査するゲート信号制御回路と、を含み、前記ゲート信号制御回路は、隣接するゲート線においてゲート信号が出力される期間が重複しないように、前記各ゲート回路にゲート信号の出力を開始させる。

(もっと読む)

電気光学装置、電気光学装置の駆動方法及び電子機器

【課題】3D眼鏡を装着した視聴者に対しフリッカー等を抑えた3D映像を知覚させる。

【解決手段】1フレームを前半1フィールドfaおよび後半フィールドfbに分割するとともに、各フィールドをさらにサブフィールドsf1〜sf20に分割する。そして、サブフィールド毎に画素をオンまたはオフのいずれかに制御して階調表示を行う。奇数ブロックの前半フィールドfaで右目画像を正極性で形成し、後半フィールドfbで左目画像を負極性で形成する。一方、偶数ブロックでは、前半フィールドfaで右目画像を負極性で形成し、後半フィールドfbで左目画像を正極性で形成する。

(もっと読む)

半導体装置及び表示装置

【課題】 一導電型のTFTによって構成され、かつ出力信号の振幅を正常に得られる表示装置の駆動回路を提供する。

【解決手段】 TFT101、104にパルスが入力されてONし、ノードαの電位が上昇した後、VDD−VthNとなったところで浮遊状態となる。よってTFT105がONし、クロック信号がHiとなるのに伴って出力ノードの電位が上昇する。一方、TFT105のゲート電極の電位は、出力ノードの電位上昇に伴い、容量107の働きによってさらに上昇し、VDD+VthNより高くなる。よって出力ノードの電位は、TFT105のしきい値によって電圧降下することなくVDDまで上昇する。その後、次段出力がTFT102、103に入力されてONし、ノードαの電位は下降してTFT105がOFFする。同時にTFT106がONし、出力ノードの電位はLoとなる。

(もっと読む)

半導体装置、表示装置、液晶表示装置、表示モジュール及び電子機器

【課題】動作を不安定にすることなく、各トランジスタの特性劣化を抑制することが可能

な半導体装置を提供することを課題とする。

【解決手段】非選択期間において、トランジスタが一定時間毎にオンすることで、シフト

レジスタ回路の出力端子に電源電位を供給する。そしてシフトレジスタ回路の出力端子は

、該トランジスタを介して電源電位が供給される。該トランジスタは非選択期間において

常時オンしていないので、該トランジスタのしきい値電位のシフトは、抑制される。また

、シフトレジスタ回路の出力端子は、該トランジスタを介して一定期間毎に電源電位が供

給される。そのため、シフトレジスタ回路は、ノイズが出力端子に発生することを抑制で

きる。

(もっと読む)

液晶表示装置及びその駆動方法

【課題】動画像の画質を改善することができる液晶表示装置を提供する。

【解決手段】液晶パネル102を駆動する駆動部と、液晶パネル102を少なくとも3つ以上の領域に区分して、その区分された領域に対応して配置される複数のランプ101を有し、複数のランプ101のうち液晶パネル102の上/下端部領域に配置されたランプが互いに接続されているバックライトユニット110と、液晶パネル102の上/下端部領域に配置されたランプのオン/オフタイムを制御する第1ランプ駆動部112と、液晶パネル102の上/下端部を除いた領域に配置されたランプのオン/オフタイムを制御する第2ランプ駆動部114と、駆動部から供給された信号を用いて、第1及び第2ランプ駆動部112、114を制御するランプ駆動制御部116と、を備えている。

(もっと読む)

液晶表示装置

【課題】液晶パネル、駆動用基板、制御基板、制御基板と駆動用基板を接続する第1の配線部材、駆動用基板と液晶パネルとを接続する第2の配線部材間の接続不良に起因する部品破壊の発生を適切に防止すること。

【解決手段】制御基板12は、FFC15a、15b、16a、16b、18、19、ソース基板13a〜13d、ゲート基板14a、14b、ソース側SOF17a〜17h、ゲート側SOF20a〜20d、液晶パネル11の接続状態検出用の入出力端子27、28、31を有するとともに、FFC15a、15b、16a、16b、18、19、ソース基板13a〜13d、ゲート基板14a、14b、ソース側SOF17a〜17h、ゲート側SOF20a〜20d、液晶パネル11は、それぞれ接続状態検出用の配線を有し、それらの各部品が組み合わされた際に、各配線が、制御基板12の接続状態検出用の入出力端子27、28、31に接続される。

(もっと読む)

タッチパネル付き液晶表示装置

【課題】表示される画像の状態等に応じて、消費電力の低減を図るタッチパネル付き液晶表示装置を提供する。

【解決手段】ソースドライバ20は、タッチパネル50への接触が検知されず、かつ、入力画像信号による画像が静止画像である場合に、所定期間に亘ってソース配線14をハイインピーダンス状態にし、ゲートドライバ30は、所定期間に亘ってゲート配線13の駆動を停止する。所定期間は、所定期間は、ソース配線14にデータ電圧が印加された後にデータ電圧が印加されない状態が継続した場合に液晶の電圧の保持率があらかじめ決められている値になるまでの期間に応じて設定されたフレーム数に応じた期間であることが好ましい。

(もっと読む)

表示パネル及びそれを含む表示装置

【課題】隣接する二つの画素が一つのデータラインを共有する構造を有する表示パネルにおいて、ベーゼル幅を低減できる表示パネルを提供する。

【解決手段】表示パネルは複数の画素、データライン、一対のゲートライン、第1ゲート駆動回路及び第2ゲート駆動回路を含む。複数の画素は表示領域に配置され、複数の画素行と複数の画素列からなる。データラインは列方向に伸長し、二つの画素列ごとに配置される。一対のゲートラインは行方向に伸長し、一つの画素行ごとに各々、画素行の第1側部及び第2側部に配置される。第1ゲート駆動回路は表示領域の第1周辺領域に形成され、画素行の第1側部に配置された第1ゲートラインにゲート信号を提供する第1ステージを含む。第2ゲート駆動回路は第1周辺領域と向き合う表示領域の第2周辺領域に形成されて、画素行の第2側部に配置された第2ゲートラインにゲート信号を提供する第2ステージを含む。

(もっと読む)

液晶表示装置及び液晶表示装置の駆動方法

【課題】 電源がオフされた際の残像の発生を回避することができる液晶表示装置及び液晶表示装置の駆動方法を提供する。

【解決手段】 液晶表示装置は、第1基板と、第2基板と、液晶層LQと、複数の走査線GLと、複数の信号線SLと、複数の画素スイッチSWPと、複数の第1電極と、走査線駆動回路GDと、第2電極と、電圧供給配線W1と、制御機構と、第1切替え機構と、第2切替え機構と、出力タイミング切替え機構と、を備える。第1切替え機構及び第2切替え機構は、制御機構から与えられる制御信号を基に、導通状態及び非導通状態の何れかに切替え可能である。出力タイミング切替え機構は、上記制御信号を基に、画素スイッチSWPを導通状態に切替える第2走査信号を複数の走査線GLに同時に出力可能である。

(もっと読む)

液晶表示装置の駆動装置

【課題】TFTを遮光するためのマスクを設けなくても、強い光が照射されたときの液晶表示装置におけるコントラストの低下を防止することができる液晶表示装置の駆動装置を提供する。

【解決手段】コモン電極電位設定回路5は、制御部2から入力されるEnable信号がローレベルのときに、液晶表示装置7のコモン電極の電位を所定の電位VCOMに設定し、Enable信号がハイレベルのときに、コモン電極接続部6をハイインピーダンス状態にする。制御部2は、少なくとも、選択期間の終了時において、Enable信号をローレベルにし、選択期間の終了時の後、Enable信号をハイレベルにする。

(もっと読む)

液晶表示パネルの駆動装置および液晶表示装置

【課題】フィードスルー電圧にもとづいて各階調に応じた電圧の値を調整しなくても、フィードスルーの影響を低減することができるようにする。

【解決手段】複数のゲート配線と複数のソース配線とが交差するように配置され、ゲート配線にゲート電圧を順次印加するゲートドライバと、コモン電極にコモン電圧を供給するコモンドライバとを有する液晶表示パネルの駆動装置であって、コモンドライバは、ゲートドライバによるゲート電圧の印加が終了した時点ではコモン電極をフローティング状態にする。

(もっと読む)

電気光学装置の駆動回路、電気光学装置及び電子機器

【課題】画素への書込極性を指定する極性信号を用いないで、当該書込極性に対応した容

量線駆動を実現する。

【解決手段】容量線駆動回路150において、第2ラッチ回路152は、一垂直走査期間

で一の容量線に対応する走査線よりも先に選択される所定の走査線に対する走査信号が供

給されたとき、自身が保持する信号をラッチする。第1ラッチ回路151は、前記一垂直

走査期間で前記一の容量線に対応する走査線よりも後に選択される所定の走査線に対する

走査信号が供給されたとき、第1ラッチ回路151でラッチされた信号を論理反転した信

号をラッチする。信号出力回路154は、第1ラッチ回路151が保持する信号が第1論

理レベルのときは第1電位信号を、第2論理レベルのときは第2電位信号を前記一の容量

線に供給する。

(もっと読む)

表示装置及びその駆動方法

【課題】高速書き込みが可能なアクティブマトリクス型の表示装置及びその駆動方法を提供する。

【解決手段】マトリクス状に配置された複数の画素を有する表示装置100であって、画素209は、画素列ごとに配置されたデータ線201からのデータ電圧を保持する保持容量206と、導通状態となることによりデータ線201から保持容量206へのデータ電圧の書き込みを可能とするダイオード203と、ダイオード203の導通により書き込まれたデータ電圧に応じて発光する有機EL素子205とを備える。

(もっと読む)

半導体装置

【課題】簡素でかつ占有面積の小さな駆動回路を提供すること。

【解決手段】本発明のシフトレジスタ回路は、複数のレジスタ回路を有している。各レジスタ回路は、クロックドインバータ回路およびインバータ回路を有している。クロックドインバータ回路の出力信号がインバータ回路の入力信号となるよう両者が直列に接続されている。さらに、レジスタ回路は、インバータ回路の出力信号が伝達される信号線を有している。該信号線には接続されている素子が多く寄生容量が大きいため高負荷である。本発明のシフトレジスタ回路は、信号線の寄生容量が大きいために高負荷であることを用いている。

(もっと読む)

電気光学装置、電気光学装置の制御方法および電子機器

【課題】階調に応じて画素に印加される電圧を補正せずに焼き付きの発生を抑える。

【解決手段】スタートパルスDY1を契機とした書き込みでは正極性の電圧で書き込みを行い、スタートパルスDY2を契機とした書き込みでは負極性の電圧で書き込みを行い、表示パネルの特性が、液晶容量に印加される直流成分が負極性側に増えていく特性である場合、スタートパルスDYR1,DYR2を契機とした書き込みにおいて画素を最低階調の黒色にする電圧を書き込み、またスタートパルスDY1からスタートパルスDYR1までの期間は、スタートパルスDY2からスタートパルスDYR2までの期間より短くすることで、正極性電圧の保持期間を負極性電圧の保持期間より短くし、負極性の電圧で保持された電圧実効値が正極性の電圧で保持された電圧実効値より大きくなり、液晶容量へ印加される直流成分がキャンセルされるようにして、焼き付きの発生を抑える。

(もっと読む)

液晶駆動方法、液晶駆動装置、液晶装置、及び電子機器

【課題】同時選択駆動法でnライン反転駆動により液晶パネルを駆動する場合に、バイアス電位のずれがあっても画質の劣化を抑えることができる液晶駆動方法等を提供する。

【解決手段】S(Sは2以上の自然数)ライン同時選択駆動法により液晶パネルを駆動する液晶駆動方法は、連続するm(mは2以上の自然数)フィールド期間の第1のmフィールド期間群を、n(nは自然数)ライン毎に極性反転させるnライン反転駆動を行う第1の駆動ステップと、前記第1のmフィールド期間群に続く連続するmフィールド期間の第2のmフィールド期間群を、直前のmフィールド期間とは反対の極性となるように前記nライン反転駆動を行う第2の駆動ステップと、前記第2のmフィールド期間群に続く連続するmフィールド期間の第3のmフィールド期間群を、前記第2のmフィールド期間群から継続して前記nライン反転駆動を行う第3の駆動ステップとを含む。

(もっと読む)

アクティブマトリクス基板、電気光学装置及び電子機器

【課題】レイアウトの自由度を高め、基板上の熱源による表示品質の低下を防止できるアクティブマトリクス基板を提供する。

【解決手段】走査線22、データ線24及び画素26を含む画素回路と、半導体基板の一辺に沿って形成された複数のパッドを含む入力パッド部30と、高速シリアルインターフェース回路40と、高速シリアルインターフェース回路からの出力に基づいて階調データを生成するロジック回路50と、階調データに基づいて複数のデータ線を駆動するデータ線駆動回路60と、制御信号に基づいて走査線を駆動する走査線駆動回路70とを有し、半導体基板の一辺と画素回路との間で、該一辺側から順に、入力パッド部、高速シリアルインターフェース回路及びロジック回路が配置され、ロジック回路と画素回路との間に、データ線駆動回路及び走査線駆動回路の一方が配置される。

(もっと読む)

61 - 80 / 1,927

[ Back to top ]