Fターム[5C006BC24]の内容

Fターム[5C006BC24]に分類される特許

1 - 20 / 187

液晶表示装置

【課題】ジグザグパターンを採用する場合に、製品開発・製造における迅速化および低コスト化に貢献し且つ違和感の無い画像表示を実現する。

【解決手段】液晶セルと、ゲートドライバと、ソースドライバと、ゲートドライバおよびソースドライバによる出力を制御することにより画像表示を実現させる制御部とを備え、第1方向を向く画素列を構成する各画素が、所定画素数毎に、当該画素列を挟む両側のソースラインへ交互に接続する配線パターンを有する液晶表示装置であって、液晶セルにおけるソースラインの総数がソースドライバの出力ラインの総数よりも1本多く、液晶セルにおける最外側のソースラインは近隣のソースラインが接続するソースドライバの出力ラインに対して接続され、上記制御部は上記最も外側のソースラインおよび上記近隣のソースラインが接続する画素列を含む領域に黒表示を実行させる。

(もっと読む)

表示装置

【課題】端子設定により、一対の伝送線路の終端方法を切り替える。

【解決手段】各駆動回路には、本体側より、一対の伝送線路を介して、表示データが差動シリアル伝送方式で供給され、前記n個の駆動回路の中の1つの駆動回路は、マスタの駆動回路として動作し、前記n個の駆動回路の中の前記マスタの駆動回路以外の駆動回路はスレーブの駆動回路として動作し、前記各駆動回路は、SELC端子を有し、前記SELC端子に入力される電圧が第1電圧レベルの時に、前記マスタの駆動回路は、その内部で前記一対の伝送線路の間に抵抗値がRaの抵抗を接続して前記一対の伝送線路を終端し、前記スレーブの駆動回路は、その内部で前記一対の伝送線路の間に抵抗を接続しないで前記一対の伝送線路を開放し、前記SELC端子に入力される電圧が前記第1電圧レベルとは異なる第2電圧レベルの時に、前記n個の駆動回路の各々が、その内部で前記一対の伝送線路の間に抵抗値が(n×Ra)の抵抗を接続して前記一対の伝送線路を終端する。

(もっと読む)

液晶表示装置

【課題】横方向の幅が広い元の画像の画像データを分割し、その分割後の画像データを各ソースドライバに供給することで、各液晶表示パネル間で滑らかに連続しているような、幅の広い画像をユーザに視認させることができる液晶表示装置を提供する。

【解決手段】有効表示領域10aの左端から液晶表示パネル3a自体の左端までの距離等をαとし、1ピクセルの幅をβとし、α/βを切り上げた整数、または、α/βを切り下げた整数をnとする。そして、タイミングコントローラ1は、与えられた画像データを2つに分割し、行毎に各ソースドライバ5a,5bに供給する。各ソースドライバ5a,5bは、それぞれ、n+1番目のピクセルの画像データから順次取り込む。

(もっと読む)

表示ディスプレイ、及び表示ディスプレイの駆動方法、並びに表示装置

【課題】EMI低減を実現しつつ、データの書き込み速度を維持可能な表示ディスプレイ、表示駆動方法、及び表示装置を提供する。

【解決手段】本発明に係る表示ディスプレイは、表示駆動装置と、それに表示データ、クロック信号を転送するタイミングコントローラとを備える。表示駆動装置は、2系統の動作が独立して実行される第1のデータ書き込み方式と、片シフト動作が実行される第2及び第3のデータ書き込み方式のいずれかが選択可能に構成されている。データ書き込みは、複数の表示駆動装置にデータ書き込みタイミングをシフトさせることによって2方向にデータ書き込みを行う構成となっている。第1のデータ書き込み方式の左シフト動作と右シフト動作は、EMIを低減するように表示データの書き込みタイミングがずれている。

(もっと読む)

シフトレジスタ駆動方法並びにシフトレジスタ及びこれを備える液晶表示装置

【課題】大画面、高解像度のa−Si TFT LCDに適用可能にする。

【解決手段】複数のステージを含み、ステージの奇数番目及び偶数番目にそれぞれ第1及び第2クロック信号が入力されて、各ステージに対応するスキャンラインを駆動する駆動信号を出力するシフトレジスタの駆動方法において、第1電源電圧に相応する第1ハイレベルの第1又は第2クロック信号をステージに提供し、第1ハイレベルより大きな第2ハイレベルの第2電源電圧を生成してステージに提供し、第1又は第2クロック信号のデュティ期間に現ステージに接続されたスキャンラインをプルアップさせる駆動信号を生成し、直後ステージの駆動信号に応答して、現ステージの駆動信号をローレベルにダウンさせて現ステージに接続されたスキャンラインにローレベルにダウンされた駆動信号を提供し、現ステージの駆動信号をローレベルに所定時間維持することを含むシフトレジスタ駆動方法。

(もっと読む)

データドライバ

【課題】システムのパワー消費を増加させることなしにデータドライバのサイズとチップ面積とコストとを低減することができるデータドライバを提供する。

【解決手段】データドライバは、第1および第2画素データに基づいてそれぞれ正および負の画素電圧を提供する2個のデータ処理回路と、マルチプレクサユニットを含んでいるマルチプレクサ回路とを含んでいる。各マルチプレクサユニットは、それぞれ正および負の画素電圧を受け取る第1および第2入力端子と、データラインに連結された出力端子とを有している。第1スイッチング装置は、第1入力および出力端子間に直列に連結された第1および第2スイッチを有している。第1および第2スイッチ間のノードは、第3スイッチを介して選択的に接地されている。第2スイッチング装置は、第2入力および出力端子間に直列に連結された第4および第5スイッチを有している。

(もっと読む)

画像表示装置

【課題】画像表示装置において、テスト画像を表示させるための画素駆動信号の出力波形をテストパッドを介して取り出せるようにする。

【解決手段】画像表示装置の水平走査用(ソース駆動用)の画素駆動部4は、画素駆動信号を出力するソースドライバICチップ31、ソースドライバICチップ31から出力される画素駆動信号をディスプレイの画素に供給する出力ライン32、及びテストパッド33がフィルム34上に設けられたチップオンフィルム組立体である。テストパッド33−1、33−2、33−3、33−4は、出力ライン32−1、32−4、32−681、32−684に設けられている。出力ライン32−1〜32−3は、ディスプレイの画素に接続されず、出力ライン32−4〜32−684は、ディスプレイの第1〜第681列目の画素列の各画素に接続される。テスト画像として、ディスプレイの最端の画素列を発光させることによる画像を表示する。

(もっと読む)

表示装置

【課題】映像線駆動回路内に表示制御回路を内蔵することにより、部品点数を削減した表示装置を提供する。

【解決手段】各映像線駆動回路はバス接続され、前記複数の映像線駆動回路の中の1つの映像線駆動回路は、マスタの映像線駆動回路として動作し、前記複数の映像線駆動回路の中の前記マスタの映像線駆動回路以外の映像線駆動回路はスレーブの映像線駆動回路として動作し、前記各映像線駆動回路の前記表示制御回路は、前記表示制御回路の設定値を保持するレジスタを有し、前記表示装置の起動時に、前記レジスタに対して、外部メモリから前記表示制御回路の設定値を書き込むことが可能であり、前記表示装置の起動時に、前記レジスタに対して、前記外部メモリから前記表示制御回路の設定値を書き込む際に、前記マスタの映像線駆動回路から最終の前記スレーブの映像線駆動回路まで順番に前記外部メモリにアクセスし、前記レジスタに前記設定値を書き込む。

(もっと読む)

液晶表示装置

【課題】液晶パネル、駆動用基板、制御基板、制御基板と駆動用基板を接続する第1の配線部材、駆動用基板と液晶パネルとを接続する第2の配線部材間の接続不良に起因する部品破壊の発生を適切に防止すること。

【解決手段】制御基板12は、FFC15a、15b、16a、16b、18、19、ソース基板13a〜13d、ゲート基板14a、14b、ソース側SOF17a〜17h、ゲート側SOF20a〜20d、液晶パネル11の接続状態検出用の入出力端子27、28、31を有するとともに、FFC15a、15b、16a、16b、18、19、ソース基板13a〜13d、ゲート基板14a、14b、ソース側SOF17a〜17h、ゲート側SOF20a〜20d、液晶パネル11は、それぞれ接続状態検出用の配線を有し、それらの各部品が組み合わされた際に、各配線が、制御基板12の接続状態検出用の入出力端子27、28、31に接続される。

(もっと読む)

表示装置駆動回路及び表示装置駆動方法

【課題】EMI発生の抑制。

【解決手段】タイミング信号STBに基づいて、第1〜第3の出力タイミングにおいて出力するための第1〜第3の出力制御信号C1〜C3を生成するアンプ出力制御回路101と、第1の出力制御信号C1に基づいて、階調電圧を出力する第1のアンプ回路AC11〜AC1nと、第2の出力制御信号C2に基づいて、階調電圧を出力する第2のアンプ回路AC21〜AC2nと、第3の出力制御信号C3に基づいて、階調電圧を出力する第3のアンプ回路AC31〜AC3nと、を備える表示装置駆動回路。連続する第1及び第2の出力タイミングの時間間隔を第1の間隔TI1、連続する第2及び第3の出力タイミングの時間間隔TI2を第2の間隔、EMC規格におけるEMIの規制対象となる周波数の逆数を周期Tとすると、第1の間隔TI1と第2の間隔TI2との最大公約数が、周期Tの最小値よりも小さい。

(もっと読む)

駆動装置及び駆動装置を用いた電子機器

【課題】基板に実装された駆動装置から出力されるデマルチ制御信号の波形の鈍りを、基板に形成された配線上で、従来よりも軽減する。

【解決手段】第1の信号を出力する第1の端子と、第2の信号を出力する第2の端子と、第3の信号を出力する第3の端子と、を含み、前記第1の信号はアナログ信号であり、前記第2の信号及び前記第3の信号の各々は、第1のタイミング信号を元に生成され、第1の期間における前記第1の信号の値を抽出するために用いられる信号であることを特徴とする駆動装置を提供する。

(もっと読む)

液晶表示装置、走査信号駆動装置、液晶表示装置の駆動方法、走査信号駆動方法、およびテレビジョン受像機

【課題】極性反転時にデータ信号の波形に鈍りが生じていても、表示ムラなどを抑制した表示品位の高い表示を行うことが可能な液晶表示装置を提供する。

【解決手段】ゲートドライバが、データ信号の極性反転時点よりも前の時点で印加されるゲートオンパルスのうち、極性反転時点に最も近いゲートオンパルスの最後端が、該ゲートオンパルスが印加される水平期間の終了時点よりも前となっており、該ゲートオンパルスの最後端から、該ゲートオンパルスが印加される水平期間の終了時点までの時間を第1の期間とし、極性反転時点から、該極性反転時点以降に印加されるゲートオンパルスのうち、極性反転時点に最も近いゲートオンパルスの印加開始時点までの時間を第2の期間とすると、上記第2の期間が上記第1の期間よりも長くなるようにゲートオンパルスを印加する。

(もっと読む)

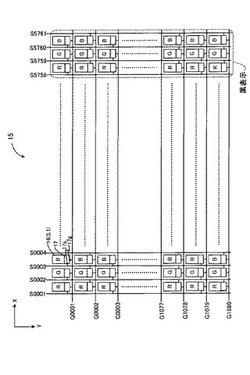

マトリクス表示装置およびその駆動方法

【課題】 マトリクス表示装置において、ゲートドライバへ出力する垂直クロックを生成するためのカウンタ回路を必要としない簡素な回路構成のタイミングコントローラを得る。

【解決手段】 複数のソースドライバ(6〜13)は、そこに入出力する単位スタートパルス(STHi)が前段のソースドライバと後段のソースドライバ間でカスケード接続され、タイミングコントローラ(14)から出力した水平スタートパルス(STH)が初段のソースドライバ(6)に入力し、垂直クロック(CLKV)のデューティ比は、縦続接続された複数の単位スタートパルスの内一つ(STH62)によって制御されていることを特徴とする。

(もっと読む)

液晶表示装置

【課題】ローカルディミングを行う液晶表示装置において、バックライトの点灯制御による電力削減に加えて液晶パネルの駆動に必要な電力を低減させ、これにより低消費電力化を図る。

【解決手段】液晶表示装置は、バックライト光源10により照明される液晶パネル20を有する。バックライト光源10は、複数の発光領域11a〜11lに分割され、液晶パネル20の表示に応じて発光輝度を制御するローカルディミングが可能となっている。例えば省エネモード等で液晶パネル20の一部の領域にのみ映像表示が行われる場合、その表示領域に対応した発光領域のバックライト光源10のみを点灯させて消費電力の低減化を図るとともに、その表示領域以外の領域では、液晶パネルのドライバの駆動を停止することにより液晶パネル自体の電力消費を低減させる。

(もっと読む)

表示パネル駆動装置

【目的】消費電力の増加及びコスト増を招くことなく、表示パネルの駆動を担う複数のドライバチップ各々を経由させて、デューティ比の安定したクロック信号を各ドライバチップに供給することが可能な表示パネル駆動装置を提供することを目的とする。

【構成】本発明においては、表示パネルの信号線各々に入力映像信号に基づく画素駆動電圧をクロック信号に応じたタイミングで印加する信号線ドライバを、夫々クロックラインによってカスケード接続された複数のドライバチップに分割して構築するにあたり、各ドライバチップに、以下の如きクロック送出部を設ける。クロック送出部は、クロックラインを介して供給されたクロック信号の周期を1/2に分周した分周クロック信号と、この分周クロック信号を所定の遅延時間だけ遅延させた遅延分周クロック信号との論理レベルが互いに同一である期間中は第1レベル、互いに異なる場合には第2レベルを有する整形クロック信号を次段のドライバチップに送出する。

(もっと読む)

液晶表示装置の駆動装置および液晶表示システム

【課題】低消費電力動作が可能な駆動装置および液晶表示システムを提供する。

【解決手段】本実施形態によれば、複数の走査線と、複数の信号線と、前記走査線と前記信号線との交点に配置される複数の液晶画素と、を備える液晶表示装置を駆動する液晶表示装置の駆動装置は、液晶表示装置の駆動装置は、第1の共通配線と、第2の共通配線と、複数のドライバモジュールと、を備える。前記ドライバモジュールのそれぞれは、比較回路と、第1のスイッチと、第2のスイッチと、を有する。

(もっと読む)

表示装置、信号線ドライバ、及び、データ転送方法

【課題】表示装置において、映像データ及び制御信号を供給するために必要な配線の数を減らし、走査線ドライバに供給される制御信号が映像データを供給するデータ伝送線に及ぼすノイズの影響を無くす。

【解決手段】液晶表示装置1が、タイミングコントローラ2と液晶表示パネル3と複数のデータドライバ4とゲートドライバ5とを備えている。タイミングコントローラ2は、複数のデータドライバ4のうちの特定ドライバ4L、4Rに制御データを供給する。特定ドライバ4L、4Rは、制御データに応答してゲートドライバ5を制御するゲートドライバ制御信号を生成し、ゲートドライバ制御信号をゲートドライバ5に供給する。

(もっと読む)

表示装置

【課題】電荷を蓄積することのできるセルの配列への電荷供給を制御するドライバ回路において、電荷のチャージシェアリング駆動時に発生するEMI(Electro Magnetic Interference)を低減する。

【解決手段】クロック信号(CLK1)により制御される先行導通手段(SW221)は、基準電位より高い電位である正極性を有する第1回路(211)の出力信号線と、基準電位より低い電位である負極性を有する第2回路(212)の出力信号線とを導通させる。所定時間経過後に、クロック信号(CLK2)により制御される後続導通手段(SW222)は、正極性を有する第3回路(213)の出力信号線と、負極性を有する第4回路(214)の出力信号線とを導通させる。第1出力信号線(DR0)、第2出力信号線(DG0)、第3出力信号線(DB0)及び第4出力信号線(DR1)は、この順序で、順次隣接している。

(もっと読む)

表示装置の駆動回路

【課題】カスケード信号の遅延時間とシステムクロックのクロック周期との関係によらず、データドライバ間のデータの連続性を保つことができる駆動回路を提供する。

【解決手段】駆動回路100のデータドライバNに内部カウンタ301を備え、内部カウンタ301は、初段のデータドライバ1が表示データの先頭信号を読み込む際にリセットされ、前段のデータドライバN−1からカスケード信号(CASCADE)が入力され、カウンタ値が第1の設定値に等しくなった場合に、内部カウンタ301がリセットされるとともに、自段のデータドライバNにおける表示データの読み込みが開始され、カウンタ値が(2)式で求められる第2の設定値に等しくなった場合に、カウンタ部300は、次段のデータドライバN+1にカスケード信号を入力するように構成した。

(もっと読む)

表示パネルを駆動するためのデータドライバ及びこれを備えるディスプレイ装置

【課題】表示パネルを駆動するためのデータドライバ及び該データドライバを備えるディスプレイ装置を提供する。

【解決手段】表示パネルと、マスタークロック信号、デジタルデータ及び駆動指示信号を提供するタイミングコントローラと、それぞれマスタークロック信号を受信し、デジタルデータを受信及び保存し、保存されたデジタルデータによる駆動信号を生成し、対応する駆動信号を表示パネルに提供する複数のデータドライバを備えるデータライン駆動部と、を備えることを特徴とするディスプレイ装置。

(もっと読む)

1 - 20 / 187

[ Back to top ]