Fターム[5C094DA09]の内容

要素組合せによる可変情報用表示装置 (81,180) | パネルの全体的構造 (7,880) | パネル上に駆動回路を有するもの (376)

Fターム[5C094DA09]に分類される特許

121 - 140 / 376

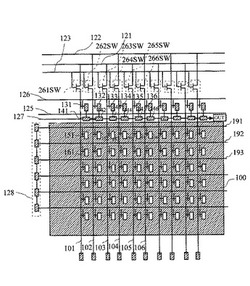

TFTアレイ・ビルトイン・セルフ検査装置と検査方法

【課題】本発明は、高額な検査装置を使用することなく、製品とした場合にも表示機能の低下を招かず、効率的に検査し得るアクティブマトリックス型基板と、該検査方法を提供することを目的とする。

【解決手段】

アクティブマトリックス型基板において、複数のデータ線の一方の端にデータ線毎に検査用の検査用基準画素を作成し、検査用基準画素の出力と各データ線に接続された画素をデータ線を通じて比較する比較器を各データ線毎に設置し、比較器の出力を保持する 保持器兼シフトレジスターを配置し、表示領域の全画素に検査用データを書き込み、検査用基準画素に検査用基準画素用検査データを書き込み、順次表示領域の各画素内のデータと検査用基準画素内のデータとを比較し、比較の結果をシフトレジスタ−に格納し、表示領域の画素に欠陥がある場合には、シフトレジスタ−内のデータをシフトアウトして欠陥の画素を特定する。

(もっと読む)

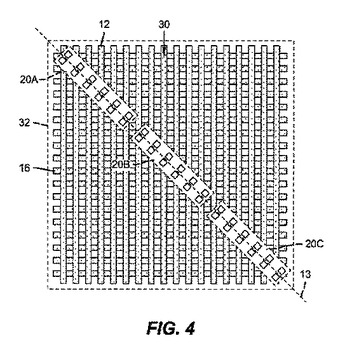

チップレットドライバーを用いるディスプレイデバイス

基板と、第1の方向において基板にわたって行内に形成される行電極のアレイを有する第1の層と、該第1の方向とは異なる第2の方向において前記基板にわたって列内に形成される列電極のアレイを有する第2の層であって、該行電極及び該列電極は重なり合ってピクセル位置を形成する、第1の層及び第2の層と、前記行電極と前記列電極との間に形成され、ピクセルの2次元アレイを形成するものであって、該ピクセルは前記ピクセル位置内に配置される、1つ又は複数の発光材料層と、前記基板上に配置されるものであって、該チップレットの数はピクセルの数よりも少なく、各チップレットは行電極のサブセット及び列電極のサブセットを排他的に制御し、それにより、前記ピクセルを制御して画像を表示する、複数のチップレットとを備える、ディスプレイデバイス。  (もっと読む)

(もっと読む)

ディスプレイデバイス内のチップレット間のピクセルの分割

ディスプレイデバイスが、基板と、基板上に形成される複数のピクセルであって、各ピクセルは2つ以上のサブピクセルを含み、該複数のピクセルは表示エリアを画定する、複数のピクセルと、表示エリア内の基板上に配置される複数のチップレットであって、各チップレットは少なくとも2つの隣接するピクセルのサブピクセルを制御する、複数のチップレットと、を備える。  (もっと読む)

(もっと読む)

表示装置及びその製造方法

【課題】静電気による薄膜トランジスタの破壊を防止することが可能な技術を提供することである。

【解決手段】

複数本のドレイン線と、前記ドレイン線と交差する複数本のゲート線と、複数の薄膜トランジスタを有し、前記ドレイン線及び前記ゲート線に駆動信号を供給する駆動部と、該駆動部に外部から制御信号を入力する電極端子とを備え、前記ドレイン線と前記ゲート線とに囲まれた領域を画素の領域とする表示装置の製造方法であって、前記駆動部の複数の薄膜トランジスタを形成する際に、前記画素の集合体である表示領域の外側領域に、前記複数の薄膜トランジスタを相互に接続し前記駆動信号の生成動作をさせる第1の配線と同一層の配線であり、かつ前記第1の配線とは異なる第2の配線を形成し、少なくとも一対の薄膜トランジスタを接続する工程と、前記薄膜トランジスタの形成後に、前記表示領域の外側領域において、前記第2の配線の切断する工程とを有する表示装置の製造方法である。

(もっと読む)

電気光学装置及び電子機器

【課題】電気光学装置に電気的に接続されるフレキシブル配線基板のOLB部における電気抵抗の増加を防止する。

【解決手段】電気光学装置(1)は、互いに対向して配置された一対の基板(10、20)と、一対の基板のうち一方の基板の複数の画素が配列された画素領域(10a)と、画素領域の周辺に位置する周辺領域と、周辺領域において、一方の基板の第1辺に沿って配置され、複数の画素を駆動する半導体素子(310)と、周辺領域において、第1辺に隣接すると共に第1辺よりも短い第2辺に沿って配列された複数の接続端子(102)とを備える。

(もっと読む)

電気光学装置および電子機器

【課題】電気光学装置の信頼性や歩留りを向上させる。

【解決手段】本発明に係る電気光学装置は、画素領域と、前記画素領域の外周に位置する周辺領域とを有する基板と、前記画素領域に配置された電気光学素子と、前記周辺領域に配置され、前記電気光学素子を駆動する第1および第2の駆動回路と、前記周辺領域に配置された外部端子と、前記外部端子と前記第1又は第2の駆動回路を接続する第1配線、又は前記第1の駆動回路と前記第2の駆動回路とを接続する第2配線であって、前記周辺領域に配置される引出配線(L1)とを有し、前記配線部が互いに電気的に接続され、異なる層に形成され、平面視において互いに重なる第1層配線部(L1a)および第2層配線部(L1b)を有する。かかる構成によれば、周辺領域に物理的衝撃が加わり基板の欠けや割れが生じても、いずれかの配線部により回路駆動が担保される。

(もっと読む)

表示装置

【課題】表示装置の作製のコストの低減を課題の一とする。

【解決手段】複数のインバータ回路及び複数のスイッチを有し、インバータ回路は、ゲート端子及び第1端子が高電源電位を供給する配線に接続された第1の薄膜トランジスタと、第1の薄膜トランジスタの第2端子が第1端子に接続され、第2端子が低電源電位を供給する配線に接続され、ゲート端子に入力信号が供給される第2のトランジスタと、を有し、第1の薄膜トランジスタ及び第2の薄膜トランジスタは同じ極性であり、第1の薄膜トランジスタ及び第2の薄膜トランジスタは、ゲート電極に接するゲート絶縁層と、ゲート絶縁層に接する微結晶半導体層と、微結晶半導体層に接する混合層と、混合層に接する非晶質半導体を含む層と、配線とを有し、混合層において、錐形状の微結晶半導体領域と、錐形状の微結晶半導体領域を充填する非晶質半導体領域とを有する表示装置である。

(もっと読む)

複数のスクリーンを有する電子装置

【課題】本発明の主な目的は、不同な表示パネルが不同な画像を同時に表示することができる複数のスクリーンを有する電子装置を提供することにある。

【解決手段】上記課題を解決するために本発明では、複数の表示モジュールと複数のフレキシブルプリント基板を含む複数のスクリーンを有する電子装置を提供する。前記複数のフレキシブルプリント基板は、複数の表示モジュールが互いに導電するように一体に連結させる。前記フレキシブルプリント基板により、複数の表示モジュールが環状に連結されているので、表示サイズを大きくすることができる。且つ、各表示モジュールが不同な画像を表示して、不同な画像を同時に表示するか、各々の表示モジュールが1つの画像の局部を表示して、1つの画像を構成して表示することができる。

(もっと読む)

電気光学装置及び電子機器

【課題】アクティブマトリクス駆動方式の液晶装置等の電気光学装置において、入力された画像信号中やこれに基づいて生成されるデータ信号中の高周波のクロックノイズの発生を低減する。

【解決手段】液晶装置(200)は、一対の基板間に挟持された液晶層と、基板(1)にマトリクス状に設けられた画素電極(11)と、これをスイッチング制御するTFT(30)とを備える。画像信号線(VID1〜VID6)をクロック信号線(CLX、CLX’)から電気的にシールドする定電位のシールド線(80、82)が基板上に配線されている。

(もっと読む)

表示装置

【課題】配線の電気抵抗を低減した表示装置を提供する。

【解決手段】基板101の上方に形成された薄膜トランジスタと、基板101の上方に形成され、基板101が有する表示部の辺に沿って設けられ、フラットケーブルおよび薄膜トランジスタに電気的に接続された配線111と、を有し、配線111は、薄膜トランジスタのソース電極109またはドレイン電極110と同じ層に形成された第1の配線と、第1の配線の上方に絶縁膜107を介して形成された第2の配線と、を有し、第1の配線は、第2の配線と並行に設けられ、絶縁膜107に開けられた複数のコンタクトホール108を介して第2の配線と電気的に接続されている。

(もっと読む)

電気光学装置、電気光学装置の製造方法、電子機器

【課題】不揮発性メモリと画素TFTとを同一基板上に形成でき、且つ両者を良好に動作させることが可能な電気光学装置を提供する。

【解決手段】画素TFTのゲート絶縁膜18を不揮発性メモリのトンネル絶縁膜(第1の絶縁膜)35と、トンネル絶縁膜35よりも膜厚の大きい第2の絶縁膜37によって構成する。また、フローティングゲート電極36のコントロールゲート電極60側の面を凹凸とし、該凹凸によってフローティングゲート電極36の表面積を拡げる。これにより、フローティングゲート電極36とコントロールゲート電極60との間の容量を、フローティングゲート電極36と半導体層33との間の容量よりも大きくする。

(もっと読む)

電気光学装置及びその製造方法並びに電子機器

【課題】液晶装置等の電気光学装置において、信頼性の高い蓄積容量を形成し、表示画像の高品位化を図る。

【解決手段】電気光学装置は、基板(10)上に、画素電極(9)と、下側電極(71)、誘電体膜(72)、及び上側電極(9)が下層側から順に積層されてなる蓄積容量(70)と、蓄積容量よりも第1層間絶縁膜(15)を介して下層側に配置された導電層(7、30a)とを備える。上側電極は、誘電体膜に面する第1電極層(9a)と、1電極層よりも上層側に形成され、第1電極層、誘電体膜及び第1層間絶縁膜に開孔された第1コンタクトホール(33)を介して導電層に電気的に接続された第2電極層(9b)とを有する。

(もっと読む)

電気光学装置及び電子機器

【課題】電気光学装置において、モニタ回路の小型化を図る。

【解決手段】電気光学装置は、論理回路部(700)の複数の第1トランジスタを模擬する複数の第1ダミートランジスタを含む第1モニタ回路部(271a、271b)と、サンプリング回路の複数の第2トランジスタを模擬する複数の第2ダミートランジスタ(272)を含む第2モニタ回路部とを有するモニタ回路(27)を備える。複数の第1トランジスタのチャネル幅に対する複数の第1ダミートランジスタのチャネル幅の比率又は複数の第1トランジスタの個数に対する第1ダミートランジスタの個数の比率と、複数の第2トランジスタのチャネル幅に対する複数の第2ダミートランジスタのチャネル幅の比率又は複数の第2トランジスタの個数に対する第2ダミートランジスタの個数の比率とが、互いに等しい。

(もっと読む)

信号伝送時のRC効果を軽減する表示パネル及び関連製作方法

【課題】従来の技術による諸問題を解決するため、信号伝送時のRC効果を軽減する表示パネル及び関連製作方法を提供する。

【解決手段】表示パネルは、表示領域を有する基板と、基板の表示領域に設けられ、信号を伝送する複数の導線と、複数の導線に電気的に接続され、パネル操作時に所要の駆動信号を提供する駆動集積回路と、複数の導線のうち1本及び駆動集積回路とそれぞれ電気的に接続する複数の接続導線とを含む。そのうち複数の接続導線は第一接続導線を有し、第一接続導線の第一区間と第二区間の厚さは実質的に異なる。

(もっと読む)

表示装置

【課題】製造歩留まりを改善するとともに、製造コストを低減させる表示装置を提供することを目的とする。

【解決手段】 表示部120と、表示部120に駆動信号を供給する駆動IC130が配置される駆動部200Aと、を備えた表示パネルを備え、駆動IC130は、メモリ150と、メモリ150に供給される信号が入力される入力端子131と、を備え、駆動部200Aは、入力端子131に電気的に接続された接続電極132と、接続電極132と接続配線140を介して電気的に接続された書き込み用端子151と、を備えている。

(もっと読む)

半導体装置およびその作製方法

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有するICチップをボンディング等により実装することが困難となり、製造コストが増大するという問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、駆動回路の少なくとも一部の回路を、上下をゲート電極で挟んだ酸化物半導体を用いた薄膜トランジスタで構成する。同一基板上に画素部及び駆動回路を設けることによって製造コストを低減する。

(もっと読む)

電気光学パネル、電気光学装置、および電子機器

【課題】電気光学用基板の信号線の構成を適正化することにより、高速シリアル転送を採

用した場合の信号特性の向上やノイズの低減を図ることのできる電気光学パネル、電気光

学装置、および電子機器を提供することにある。

【解決手段】電気光学装置の素子基板10上には、第1信号線11e〜11hと、この第

1信号線11e〜11hよりも広い幅寸法の第2信号線11a〜11dとが形成されてい

る。このため、幅寸法の広い第2信号線11a〜11dを高速シリアル転送に用い、幅寸

法の狭い第1信号線11e〜11hについては、第2信号線11a〜11dに比して転送

速度が遅いシリアル転送用の信号線、あるいはパラレル転送用の信号線として用いる。

(もっと読む)

表示基板及びこれを備える表示装置

【課題】表示基板及びこれを備える表示装置を提供すること。

【解決手段】表示基板は、画素、第1パッド部、及び第2パッド部を含む。画素は、表示領域に配置され、ゲート配線とデータ配線に接続されるスイッチング素子、及びスイッチング素子と電気的に接続される画素電極を含む。第1パッド部は、表示領域を取り囲む周辺領域に配置され、第1導電層で形成される第1導電パターンと、第1導電パターンとオーバーラップし第1導電層で形成される第2導電パターンと、第1及び第2導電パターンの間に配置される絶縁層とを有する第1パッドを含む。第2パッド部は、第1パッド部と隣接する周辺領域に配置され、第1パッドの第1導電パターンと接続する第3導電パターンを有する第2パッドを含む。パッド部に形成される静電気キャパシタを利用することにより、静電気による表示装置の損傷を防ぐことができる。

(もっと読む)

電気光学装置及び電子機器

【課題】液晶装置等の電気光学装置において、配線等を電気抵抗値の少ない素材で形成することによって、高品位な画像表示を可能としつつ、光リーク電流の発生を抑制する。

【解決手段】電気光学装置は、基板(10)と、相交差するデータ線(6)及び走査線(11)と、該交差に設けられた画素電極(9)と、(i)一の方向に沿ったチャネル長を有するチャネル領域(1a´)を有する半導体膜と、(ii)ゲート電極(3a)とを含むトランジスタ(30)と、ゲート電極上に配置された遮光部(11b)と、画素電極の下層側に形成された下部容量電極(72)とを備える。第1及び第2絶縁膜には、遮光部とゲート電極とを接続する第1部分と、他の方向に沿って延在し、半導体膜の脇で遮光部と走査線とを電気的に接続する第2部分とを有するコンタクトホール(801)が形成され、画素電極及び下部容量電極は、保持容量(70)を形成している。

(もっと読む)

マトリクス表示素子およびマトリクス表示装置

【課題】大きな曲率で曲げることができるマトリクス表示素子の実現。

【解決手段】並行に設けられた複数の第1帯状電極34を有する第1基板31と、並行に設けられた複数の第2帯状電極35を有する第2基板32とを対向して配置し、複数の第1帯状電極と複数の第2帯状電極の交差部に画素が形成されるマトリクス表示素子であって、第1基板31は、複数の第1帯状電極34を電気的に外部接続するための第1端子部36A,36Bを備え、第2基板32は、複数の第2帯状電極35を電気的に外部接続するための第2端子部37A,37Bを備え、第1端子部と第2端子部は、マトリクス表示素子の表示面の対向する所定の2辺に配置されており、対向する所定の2辺以外の辺には端子部が配置されない。

(もっと読む)

121 - 140 / 376

[ Back to top ]