Fターム[5C094DB04]の内容

要素組合せによる可変情報用表示装置 (81,180) | 電気的接続 (3,264) | 素子同士の接続 (1,011)

Fターム[5C094DB04]に分類される特許

201 - 220 / 1,011

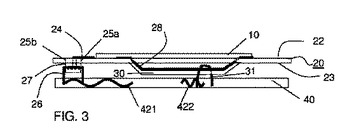

集合体、集合体用コンポーネントおよび集合体製造方法

柔軟な箔(20)上の電気物理トランスデューサ(10)の、担体(40)との集合体が提供される。前記柔軟な箔(20)は前記電気物理トランスデューサに接続された少なくとも第一の電気伝導性トラック(24)を設けられた第一の主表面(22)と、該第一の主表面の反対側にあり前記担体のほうに面する第二の主表面(23)とを有する。前記少なくとも第一の電気伝導性トラックと並行して少なくとも第一の切り込み(25a)が前記柔軟な箔を通って延在し、それにより前記少なくとも第一の電気伝導性トラックの一部を担持する前記柔軟な箔のストリップ形状部分を画定する。前記少なくとも第一の電気伝導性トラックは前記担体の電気伝導体(421)に電気的に接続され、前記柔軟な箔は、そのストリップ形状部分をもって前記担体に取り付けられる。  (もっと読む)

(もっと読む)

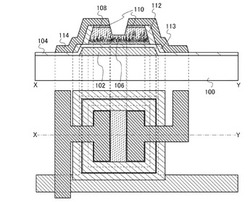

薄膜トランジスタとその作製方法

【課題】ドレイン電流のオン/オフ比が高く維持されつつ、光電流とオフ電流が十分に小さい薄膜トランジスタを提供することを課題とする。

【解決手段】ゲート電極層と、ゲート電極層を覆って設けられたゲート絶縁層と、ゲート電極層と全面が重畳して設けられた第1の半導体層と、第1の半導体層上に接して設けられ、前記第1の半導体層よりもキャリア移動度が低い第2の半導体層と、第2の半導体層に接して設けられた不純物半導体層と、少なくとも前記第1の半導体層の側壁を覆って設けられたサイドウォール絶縁層と、少なくとも前記不純物半導体層に接して設けられたソース電極及びドレイン電極層と、を有する薄膜トランジスタとする。第2の半導体層は、第1の半導体層上に離間して設けられていてもよい。

(もっと読む)

電気光学装置、電気光学装置の製造方法、電気光学装置用基板、電子機器

【課題】静電気によるTFT回路の動作不具合を回避するとともに歩留まりの向上を図ることのできる電気光学装置、電気光学装置の駆動方法、電気光学装置用基板、電子機器を提供する。

【解決手段】本発明の電気泳動表示装置100は、可撓性を有する素子基板30と対向基板31との間に電気泳動素子32を挟持してなり、表示部5に画素回路、非表示部6に周辺回路が形成され、素子基板30上に、表示部5に配置された画素回路と、非表示部6に配置された周辺回路と、画素回路の一部を構成するボトムゲート構造の選択トランジスタ上に層間絶縁層を介して形成される第1導電層77Aと、周辺回路の一部を構成するボトムゲート構造の第1トランジスタ上に層間絶縁層を介して形成される第2導電層77Bと、を含む回路層34を備え、第2導電層77Bが接地されている。

(もっと読む)

表示装置及び電子機器

【課題】画素電極電位に起因したオフリーク電流が上昇しにくい低消費電力の表示装置を提供すること。

【解決手段】表示装置は、対向配置された第1の基板及び第2の基板と、第1の基板と第2の基板との間に配置された表示素子と、第1の基板の表示素子側に形成された薄膜トランジスター24と、薄膜トランジスター24の表示素子側に、平面視で薄膜トランジスター24と重なるように形成された画素電極21と、薄膜トランジスター24と画素電極21との間の層に形成されたシールド電極26と、を備える。シールド電極26は、平面視で少なくとも薄膜トランジスター24の低濃度不純物領域に重なる位置に配置される。

(もっと読む)

表示装置

【課題】アクティブマトリクス型基板において、薄膜トランジスタと、その端子接続部を同時に作り込み、少ないマスク数で歩留まりの良い表示装置を提供する。

【解決手段】画素部および外部入力端子を有する表示装置であって、画素部は、ゲート電極と、半導体膜と、ゲート電極上に形成された絶縁膜、および絶縁膜上に半導体膜と電気的に接続された電極を有するTFTを有し、外部入力端子は、ゲート電極と同じ層に形成された第1の配線と、電極と同じ層に形成され、絶縁膜に形成されたコンタクトホールを介し第1の配線と接続された第2の配線と、第2の配線に接続され、第2の配線上に形成された透明導電膜と、第2の配線と透明導電膜が接続している位置で透明導電膜と電気的に接続するフレキシブルプリント配線板を有する表示装置。

(もっと読む)

表示装置、及び当該表示装置を具備する電子機器

【課題】消費電力が抑制された表示装置を提供する。

【解決手段】第1のトランジスタ、第2のトランジスタ、及び一対の電極を有する発光素子を含む画素が複数設けられた画素部を有し、前記第1のトランジスタは、ゲートが走査線に電気的に接続され、ソースまたはドレインの一方が信号線に電気的に接続され、ソースまたはドレインの他方が前記第2のトランジスタのゲートに電気的に接続され、前記第2のトランジスタは、ソースまたはドレインの一方が電源線に電気的に接続され、ソースまたはドレインの他方が前記一対の電極の一方に電気的に接続され、前記第1のトランジスタは、水素濃度が5×1019/cm3以下である酸化物半導体層を有する。そして、前記表示装置が静止画像を表示する期間の間に、前記画素部に含まれる全ての走査線に供給される信号の出力が停止される期間を有する。

(もっと読む)

半導体装置及び電子機器

【課題】半導体装置の駆動能力の向上を図ることを課題の一とする。

【解決手段】半導体装置は、第1のトランジスタと、第2のトランジスタとを有し、第1のトランジスタの第1の端子は、第1の配線と電気的に接続され、第1のトランジスタの第2の端子は、第2の配線と電気的に接続され、第2のトランジスタのゲートは、第3の配線と電気的に接続され、第2のトランジスタの第1の端子は、第3の配線と電気的に接続され、第2のトランジスタの第2の端子は、第1のトランジスタのゲートと電気的に接続され、第1のトランジスタ及び第2のトランジスタは、酸化物半導体によりチャネル領域が形成され、第1のトランジスタ及び第2のトランジスタのチャネル幅が1μmあたりのオフ電流が1aA以下である。

(もっと読む)

表示装置およびその駆動方法ならびに電子機器

【課題】高画質化を実現することが可能な表示装置およびその駆動方法ならびに電子機器を提供する

【解決手段】走査線駆動回路23が、映像信号電圧Vsigの書き込み時に、映像信号電圧Vsigの印加期間内に走査線WSLに対する選択パルスの印加を終了させる。また、信号線DTLの延在方向に沿った信号線駆動回路24から各画素11までの距離が大きくなるのに応じて、選択パルスの印加終了タイミングが遅くなることによって選択パルスの印加期間が長くなるように、印加期間の調整を行う。表示輝度の画素位置によるばらつきが低減もしくは回避され、画素位置に応じた画質劣化(垂直方向に沿ったいわゆるシェーディング現象の発生や、表示むらの発生)が低減もしくは回避される。

(もっと読む)

表示装置、表示装置の製造方法および電子機器

【課題】製造工程を簡略化することが可能な表示装置の製造方法を提供する。

【解決手段】表示装置1は次のようにして製造する。まず、基板10上に、ゲート電極層11、ゲート絶縁膜12および半導体層13を順に形成した後、領域10A,10Bに渡りソース・ドレイン電極層15を形成する。ソース・ドレイン電極層15が、電極層15aと上部金属層15bとを有することにより、その後の工程で、画素間絶縁膜17をパターニング形成する際、電極層15aが損傷を受けずに済む。画素間絶縁膜17の形成後、領域10Aにおいて、ソース・ドレイン電極層15のうち上部金属層15bを選択的に除去することにより、電極層15aの表面を露出させる。この露出した電極層15a上に有機層18およびカソード電極19を形成することで、領域10Aに、ソース・ドレイン電極層15(電極層15a)をアノード電極として用いた有機発光素子1aを形成する。

(もっと読む)

表示装置および電子機器

【課題】低コスト化を図りつつ高画質化を実現することが可能な表示装置を提供する。

【解決手段】各画素11に接続された2つの発光制御線DSL1,DSL2に対して制御パルスを印加し、各色に対応する3つのサブピクセル11R,11B,11Gの発光動作および消光動作をそれぞれ制御する。各画素11において、各サブピクセル11R,11B,11Gには、2つの発光制御線DSL1,DSL2のうちの一の発光制御線が割り当てられて接続されている。2つの発光制御線DSL1,DSL2のうちの少なくとも1つが、3つのサブピクセル11R,11Bのうちの一部である2つのサブピクセルに対して共通して接続されている。各サブピクセル11R,11B,11Gでの構造や電流密度を各色同士で共通化すると共に、使用する発光制御線の数を削減しつつ、色ごとの劣化速度の相違に起因した経時的な色ずれが抑制される。

(もっと読む)

素子基板、素子基板の製造方法、素子基板の製造装置及び表示装置

【課題】動作信頼性の高い素子基板、素子基板の製造方法、素子基板の製造装置及び表示装置を提供すること。

【解決手段】基板と、当該基板上に設けられ、互いのゲート幅が同一方向に揃うように形成された複数のトランジスタ素子とを備える。

(もっと読む)

電気光学装置及び電子機器

【課題】液晶装置等の電気光学装置において、例えば基板上の積層構造における最上層側の段差を低減し、高品位な画像を表示する。

【解決手段】電気光学装置は、基板上の画素領域に設けられ、所定の形状にパターニングされた透明電極(9)と、透明電極の下地となる絶縁膜(45)と、この絶縁膜上における画素領域のうち透明電極が形成された透明電極形成領域を除く透明電極非形成領域に設けられ、透明電極の上層側表面と絶縁膜の上層側表面との段差を低減するための段差低減膜(610)と、基板上の積層構造における透明電極及び段差低減膜と絶縁膜との間に基板上で平面的に見て絶縁膜に重なるように形成され、透明電極の屈折率と絶縁膜の屈折率との間の屈折率を有するエッチングストッパー膜(710)とを備える。

(もっと読む)

表示装置及びその製造方法

【課題】絶縁層による光透過率の低下を防止することができる表示装置及びその製造方法を提供する。

【解決手段】表示装置は、第1基板110上に位置する第1絶縁層116と、第1絶縁層116上に位置する下部電極118bと、下部電極118bの上面及び側面を囲むように形成された誘電体層120aと、誘電体層120a上に位置する上部電極122aと、を備える。第1絶縁層116は、誘電体層120aに対してエッチング選択比を有してもよい。第1絶縁層116は、シリコン酸化物を含み、誘電体層120aは、シリコン窒化物を含んでもよい。

(もっと読む)

平板表示装置及びその製造方法

【課題】薄膜トランジスタ及びMOS(Metal−Oxide−Semiconductor)構造のキャパシタを備える平板表示装置及びその製造方法を提供する。

【解決手段】第1領域の基板上に半導体で形成された活性層と、第2領域の基板上に半導体で形成された下部電極と、活性層及び下部電極を含む上部に形成された第1絶縁層と、活性層上の第1絶縁層上に第1導電層及び第2導電層で形成されたゲート電極と、下部電極上の第1絶縁層上に第1導電層で形成された上部電極と、ゲート電極及び上部電極を含む上部に形成され、活性層及び上部電極が露出するようにパターニングされた第2絶縁層と、露出した活性層に接続されるソース電極及びドレイン電極とを備える。

(もっと読む)

液晶ディスプレイ

【課題】ピクセル口径比を増大し、静電容量性クロストークが殆どないTFTアレイを提供する。

【解決手段】透明な第一基板上にゲート電極及びゲートアドレス線7を形成するステップと、前記ゲート電極を含む前記第一基板上にゲート絶縁層を形成するステップと、前記ゲート絶縁層上に半導体層を形成するステップと、前記半導体層上にドレーン電極及びソース電極とドレインアドレス線5、補助記憶コンデンサ電極12を形成するステップと、前記補助記憶コンデンサ電極12を含む前記第一基板上にフォトイメージ形成可能な有機絶縁層を設けるステップと、前記有機絶縁層にフォトイメージ工程を実施して前記補助記憶コンデンサ電極12の表面が露出するコンタクト・ホール36を形成するステップと、前記コンタクト・ホールを通じて前記補助憶補助コンデンサー電極12の上部と電気的に接続されるピクセル電極3を形成するステップ、を有するTFTアレイ。

(もっと読む)

カラーディスプレイ用TFTパネルおよびその製造方法

【課題】低温プロセスにおいて重複走査領域が発生する場合であっても、デバイス特性にばらつきの少ないTFTパネルを提供すること。

【解決手段】薄膜トランジスタが列状に配列され、かつ互いに平行な複数の制御領域が連続して並んだ基板と、前記基板上に配置された平坦化膜とを有するTFTパネルであって、前記制御領域には、最大結晶粒径が大きい半導体層からなるチャネルを有する薄膜トランジスタXが列状に配列された制御領域Xと、最大結晶粒径が小さい半導体層からなるチャネルを有する薄膜トランジスタYが列状に配列された制御領域Yと、が含まれ、前記制御領域X同士の中心間距離は、前記制御領域の短軸の3n[nは1以上の整数]倍である、カラーディスプレイ用TFTパネル。

(もっと読む)

表示装置

【課題】制約されたスペースで、検査用薄膜トランジスタを充分大きなサイズで形成し得る断線等検査回路を備える表示装置を提供する。

【解決手段】基板上に、複数画素に信号を供給する複数信号線と、前記信号線と接続する断線等検査回路とを備え、

前記断線等検査回路は、検査用薄膜トランジスタを複数段に配置し、

第1検査用配線IW1と下段の検査用薄膜トランジスタを介在させて接続される第2検査用配線IW2が、上段の検査用薄膜トランジスタの間を走行するように構成する。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】銅を含む層とチタニウムを含む層とをエッチングする時に、非過水系のエッチング液を使用して工程の安定性を向上させる。

【解決手段】本発明は、薄膜トランジスタ表示板に対する発明であって、より詳細には、銅(Cu)とチタニウム(Ti)とをそれぞれ含む二重層配線に形成される薄膜トランジスタ表示板に関し、構造的にはチタニウムを含む層が銅を含む層より幅が広くて、チタニウムと銅とを共にエッチングする段階と、別にエッチングする段階とを含めて製造することを特徴とする。また、ゲート絶縁膜に段差が形成されている。

(もっと読む)

平板表示装置及びその製造方法

【課題】表示パネルにおける光透過率を向上させることができる平板表示装置及びその製造方法を提供する。

【解決手段】平板表示装置は、第1基板上に形成され、ソース領域、ドレイン領域、及びチャネル領域を含む活性層と、活性層を含む第1基板上に形成されたゲート絶縁層と、チャネル領域上のゲート絶縁層上に形成されたゲート電極と、ゲート電極を含むゲート絶縁層上に形成された第1層間絶縁膜と、第1層間絶縁膜及びゲート絶縁層に形成されたコンタクトホールを介してソース領域及びドレイン領域の活性層に接続されたソース電極及びドレイン電極と、第1層間絶縁膜とソース電極及びドレイン電極との間に介在する第2層間絶縁膜と、ソース電極及びドレイン電極を含む第1層間絶縁膜上に形成された保護層と、保護層に形成されたビアホールを介してソース電極またはドレイン電極に接続された画素電極とを備える。

(もっと読む)

表示装置およびその駆動方法ならびに電子機器

【課題】素子を増やさずに、有機EL素子の発光、消光を制御することの可能な表示装置およびその駆動方法ならびに電子機器を提供する。

【解決手段】有機EL素子11と直列に接続された駆動トランジスタTr1として、デュアルゲート型のトランジスタが用いられている。駆動トランジスタTr1のバックゲートの電圧を所定の電圧に変更することにより、駆動トランジスタTr1がオフし、それに伴って、有機EL素子11が消光する。また、バックゲートの電圧が上記とは異なる所定の電圧となっている状態で、Vth補正、書き込みおよびμ補正が実行された後、書き込みトランジスタTr2をオフすることにより、有機EL素子11が所望の輝度で発光する。

(もっと読む)

201 - 220 / 1,011

[ Back to top ]