Fターム[5D044GL31]の内容

デジタル記録再生の信号処理 (102,243) | 変調復調 (1,349) | 変調方式の種類 (836) | パーシャルレスポンス (450)

Fターム[5D044GL31]の下位に属するFターム

ビタビ復号を用いるもの (298)

Fターム[5D044GL31]に分類される特許

101 - 120 / 152

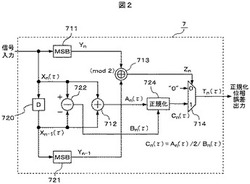

位相誤差検出回路、位相同期ループ回路および情報再生装置

【課題】位相誤差検出回路において、読み出し信号の振幅レベルが変動しても位相誤差を精度良く検出し、よって位相同期ループ回路の位相同期特性を安定させること。

【解決手段】位相誤差検出回路7は、入力信号の連続する2つのサンプリング位置n,(n−1)における信号レベルXn、Xn−1について、それらの和Anと差Bnの比Cn(=An/2/Bn)を演算する演算器を備える。そして、信号レベルXn、Xn−1の極性が変化するサンプリング位置における演算結果Cnを位相誤差信号Tnとして出力する。さらに、演算したAnの値を、入力信号のDC誤差信号Snとして出力する。

(もっと読む)

PRML検出器

【課題】アシンメトリな再生波形であっても、または、ノイズの多い環境であっても、正確な等化誤差を求め、かつ、FIRフィルタの係数を適応制御する際の仮判定値を正確に出力する。

【解決手段】記録媒体からの再生信号の波形を等化する波形等化器と、波形等化器が等化した波形に基づいて、前記再生信号の2値化データを生成する復号器とを備えたPRML検出器であって、復号器から出力された仮データ列に基づいて、等化する目標値を決定する目標値判定器と、等化器の加算器からの出力と、目標値判定器により決定された前記目標値とに基づいて、前記波形等化器の所定の係数を設定する。

(もっと読む)

評価値演算装置、記録再生装置、評価値演算方法、記録方法

【課題】最尤復号処理を行う記録再生システムにおいて記録条件設定のために好適な評価値を得ることができるようにする。

【解決手段】最尤復号処理で得られる記録系列のうち、例えばユークリッド距離が最小であるパスの存在するパスなどの特定のパスについての差メトリックから評価値を生成する際に、差メトリックの理想値との誤差をあらわす差メトリック誤差値(DM_MEP)を、マークエッジの時間軸上のエッジシフト方向に応じて演算方式を選択して算出する。これにより差メトリック誤差値(DM_MEP)を、理想値からの誤差を時間軸上のエッジシフト方向とともに表現するものとして得る。そして、得られた差メトリック誤差値を、合流点の状態毎に分類して統計することで評価値を得る。

(もっと読む)

同期装置、同期方法及び同期プログラム並びにデータ再生装置

【課題】本発明は、周波数誤差の引込範囲を広げて位相同期の能力を向上できるようにする。

【解決手段】本発明は、周波数誤差検出回路33において位相検出器54により補間信号pkにおける位相誤差Δτ(k)を検出し、差分算出器55により当該位相誤差Δτ(k)と1クロック前の位相誤差Δτ(k−1)との差分を基に周波数誤差Δf(k)及びその移動平均である平均周波数誤差Δfa(k)を算出し、位相同期部8において周波数収束ループ又は周波数初期値ループを形成して周波数誤差Δf(k)に基づく周波数補正値DF又は平均周波数誤差Δfa(k)に基づく平均周波数補正値DFAをLPF25の積分項に加算することにより、当該位相同期部8における周波数誤差Δf(k)を高速に且つ安定してほぼ0に収束させることができる。

(もっと読む)

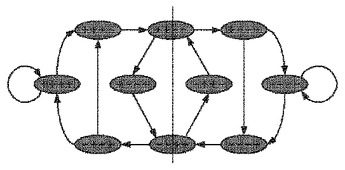

パーシャルレスポンス最尤復号化

ビタビ復号器のようなパーシャルレスポンス最尤復号器が,一連の組み合わされた状態を演算する。各々の組み合わされた状態は,状態の複数の相補完するセットから少なくとも二つの状態を表すことが出来るよう組み合わされている。各データシンボル及び各組み合わされた状態に対して,ビタビプロセッサ703は,組み合わされた状態への各パスに対するパスメトリックと準状態の表示とを決定する。ビタビプロセッサ703のパス選択プロセッサ709は,最尤性のあるパスメトリックに対応するパスに対して,選択されたパス及び選択された準状態の表示を選定する。準状態の表示は,組み合わされた状態が,データシンボルに対して,相補完し合う状態のセットのどれを表わしているかを示す表示である。ビタビ・アルゴリズムが,より少ない数の組み合わされた状態に適用され得るので,本発明は,複雑さの顕著な減少を可能にし,計算のより少ない負担を可能にする。  (もっと読む)

(もっと読む)

光ディスク装置および光ディスクの再生方法

【課題】PLL回路を安定動作させることによって、PRML回路の動作を安定させること。

【解決手段】光ディスクに光ビームを照射し、その反射光から検出したRF信号を、第1の等化手段(HD DVD用等価回路23)に供給する。第1の等化手段では光ディスクに記録された最小記録信号に相当する周波数帯域をブーストする。ブーストされたRF信号に基づいてクロック生成手段(PLL回路50)によりクロック信号を生成する。前記クロック生成手段によって生成されたクロック信号および等化係数に基づいて、RF信号を第2の等化手段(等価器41)によってパーシャルレスポンス波形信号に等化し、更に、クロック生成手段によって生成されたクロック信号に基づいて、パーシャルレスポンス波形信号を最尤復号して再生信号を出力する。

(もっと読む)

位相同期装置、方法、及び、光ディスク装置

【課題】高速引込みが可能なPLL回路を備えた位相同期装置を提供する。

【解決手段】PLL回路17が非同期状態になると、最大符号反転間隔計測器18は、PRML検出器16が出力する識別データ中の符号反転間隔の最大値を計測する。第1のチャネル周波数推定器19は、符号反転間隔の最大値に基づいて、チャネル周波数を推定し、推定チャネル周波数fdet_Tを出力する。PLL回路17は、中心周波数を、推定チャネル周波数fdet_Tに設定する。その後、sync間隔計測器20は、識別データからsync間隔を計測する。第2のチャネル周波数推定器21は、計測されたsync間隔に基づいてチャネル周波数を推定し、推定チャネル周波数fdet_Sを出力し、PLL回路17は、中心周波数を、推定チャネル周波数fdet_Sに設定する。

(もっと読む)

データ書込装置および記憶システム

【課題】 誤り訂正符号化の対象となるデータとパリティデータとを高速に記憶装置に書き込むつつ、ハンドシェイクなしで、データとパリティデータとを整列すること。

【解決手段】 LDPC符号化部304は、本体データに対しタイミング調整を行って書込回路334に出力するタイミング調整回路326と、入力信号系列に対しLDPC符号化を行ってパリティデータを生成して書込回路334に出力するパリティ生成回路328と、本体データとパリティデータを順次うけとって、ライトプリコン部305、ドライバ306などを介して、記憶装置に出力する書込回路334と、を含む。

(もっと読む)

信号処理装置および信号記憶システム

【課題】 DAEの回路規模が大きい。

【解決手段】 第1乗算器400〜418は、一時推定値x0〜x9を用いて信号u0〜u9をそれぞれ算出する。単位処理回路420〜430は、第1乗算器400〜418の乗算結果である信号u0〜u9を用いて信号v4〜v9をそれぞれ算出する。統合回路432および434は、単位処理回路420〜430から出力された信号v4〜v9を用いて対数尤度比λ4およびλ5をそれぞれ算出する。ここで、単位処理回路420〜430において、連続するλの算出に関する回路の一部を共用化することにより、DAE338の回路規模を削減する。例えば、λ4およびλ5の算出に関しては、4つの単位処理回路422、424、426および428の一部が共用される。

(もっと読む)

波形等化制御装置

【課題】 マーク波形とスペース波形とが非対称であっても、目標とする波形への波形全体の収束速度と安定性とを両立させる。

【解決手段】 波形等化制御装置として、フィルタを有し、タップ係数信号に従って前記フィルタのタップ係数の更新を行い、前記フィルタを用いて記録媒体から読み出された入力信号に対して波形等化を行う波形等化器と、マーク用適応ステップサイズ及びスペース用適応ステップサイズを求めて出力するステップサイズ学習部と、前記フィルタのタップ係数の更新量を、前記入力信号のマーク波形及びスペース波形のそれぞれのために、前記マーク用適応ステップサイズ及び前記スペース用適応ステップサイズのそれぞれを用いて求め、その結果を前記タップ係数信号として出力する係数更新量計算部とを備える。

(もっと読む)

光ディスク装置及び再生信号処理回路

【課題】複数の光スポットからの再生信号を使ってクロストークの影響を低減する光ディスク装置においては安定なクロックの生成を実現することが課題である。

【解決手段】各スポットからの再生信号の遅延調整器(20)をPLLループ(70)の外部に構成することによってループ遅延を短縮し、安定なフィード・バック制御動作を実現するクロック発生回路を用いる。

【効果】クロックの安定な生成が可能となり大容量光ディスクの再生動作を安定化した。

(もっと読む)

波形等化制御方法及び、光ディスク装置、波形等化回路

【課題】

光ディスク装置で適応等化処理を行う際に、誤差収束に要する再生データ量削減や、FIRフィルタ係数の収束を早急に行う光ディスク装置、波形等化回路を提供する。

【解決手段】

本発明における光ディスク装置、波形等化回路は、少なくとも、適応等化処理の開始、停止を制御する制御手段と、タップ係数値の変更が可能なFIRフィルタと、FIRフィルタ出力と等化目標値との誤差収束を判定する手段と、タップ係数値を一時的に保持する記憶手段と、FIRフィルタに対するタップ係数値の生成手段より光ディスク装置、波形等化回路を構成することで解決される。

(もっと読む)

情報信号再生装置、方法、及び、光ディスク再生装置

【課題】 高精度のアシンメトリの検出及び補正を実現し、最尤検出の検出性能を向上できる情報信号再生装置を提供する。

【解決手段】 オフセット補正器12は、誤差算出器16の出力に基づいて、A/D変換器11の出力に含まれる最短周期信号のDCレベルと最尤検出器15における複数の基準レベルのうちの中央の基準レベルとが一致するようにオフセット補正する。アシンメトリ補正器13は、オフセット補正器12の出力信号のアシンメトリ量を検出し、検出したアシンメトリ量に基づいて、非線形変換により、オフセット補正器12の出力信号を、アシンメトリが減少するように補正する。最尤検出器15は、アシンメトリ補正器13の出力信号を入力し、最尤検出によってチャネルビットデータ列に復号する。

(もっと読む)

タップ係数設計方法及び装置並びにディジタル信号の位相同期方法及び装置

【課題】PR等化基準を目指す信号処理系において、等化フィルタの性能の向上及び回路規模の減少を図る。

【解決手段】光ディスク再生装置1は、再生信号をデータレートよりも高い周波数でサンプリングするA/Dコンバータ3と、位相補間FIRフィルタ11を用いた位相同期処理を行うITR方式のディジタルPLL回路10とを備える。本発明に係るタップ係数設計方法では、位相補間FIRフィルタ11のタップ係数を設計する。本方法では、ディジタルPLL回路10の後段にデータレート周波数における適応等化型FIRフィルタを設け、適応等化型FIRフィルタの収束した最小平均二乗誤差の基準におけるFIRフィルタ・タップ係数を推定値として利用して、位相補間FIRフィルタ11のタップ係数の値を設計する。

(もっと読む)

自動等化器及び自動等化方法、並びに再生装置

【課題】 2値化手段として最尤復号器を用いた再生装置にあっても、自動等化の調整時間を短縮できる自動等化器を提供する。

【解決手段】 SAM値算出部77は、最尤復号器76により検出された2値化データのSAM値をリアルタイムに算出する。再生信号評価値算出部78は、SAM値算出部77により算出されたSAM値に基づいて再生信号の評価値を算出する。制御部79は、再生信号評価値算出部78により算出された再生信号の評価値に基づいて等化器75のパラメータを設定し、等化器75のパラメータを所定範囲で可変する。

(もっと読む)

光ディスク装置

【課題】 消費電力が問題となるPRML信号処理回路の省電力化を実現する。

【解決手段】 周波数検出器113はアナログ/デジタル変換器115から提供される再生信号の周波数と、前記変換用クロックの周波数との周波数誤差を検出する。位相比較器112はアナログ/デジタル変換器115から提供される再生信号の理想サンプリング位相と、前記変換用クロックの位相との位相誤差を検出する。ループフィルタ114は周波数誤差と位相誤差に基づいて、電圧制御発振器115の発振周波数を制御する。適応等化器118はアナログ/デジタル変換器115から提供される再生信号を予め定めたPRクラスの応答となるように波形等化する。ビタビ復号器110は波形等化信号を最尤列推定によりバイナリデータに復号する。クロック供給制御回路117は前記周波数誤差が指定誤差よりも大きい場合、少なくとも位相比較器112、適応等化器118及びビタビ復号器110へのクロックを停止する。

(もっと読む)

磁気サーボ位置復調器、磁気媒体で基準マークを判断する方法、基準マークを検出するための装置、および磁気媒体で基準マークを検出する方法

【課題】磁気データ記憶媒体で基準マークを検出するための装置および方法を提供する。

【解決手段】1つの変形例では、この装置は、パーシャルレスポンス/最大尤度(PRML)技術を利用して磁気データ記憶媒体から情報を抽出するように動作可能な磁気サーボ位置復調器を含む。PRMLチャネル内に格納された同期マークは次いで、デジタルフィルタを利用して検出される。検出された同期マークの各々について、同期マークのさらなる正確な位置が数学的予測モデルを利用して判断され得る。

(もっと読む)

波形等化装置、情報再生装置、波形等化方法、波形等化プログラムおよび記録媒体

【課題】 演算量を抑え、より広い領域の入力信号列に対して重み付け加算演算等の演算を行い、より適切な等化特性の適応化を行うことが可能な波形等化装置を提供する。

【解決手段】 本発明の波形等装置は、入力信号列を波形等化しつつ、その等化特性を適応化する波形等化装置であって、前記入力信号列に対して前記波形等化を行うことで等化後信号列を生成するFIRフィルタ4と、連続して流れる入力信号列から一定の間隔で検出して得られる入力信号列を用いた所定の演算を行い、この演算結果に基づいて前記FIRフィルタ4のタップ係数c(k)を適応化する等化適応化部12とを備えている。

(もっと読む)

波形等化制御回路および波形等化制御方法

【課題】 非対称性を持った再生信号に対して波形等化制御を行う際の、等化誤差演算、タップ係数値の更新を適切に行うことが可能な波形等化制御技術を提供する。

【解決手段】 波形等化制御回路において、タップ係数値の変更が可能なFIRフィルタ回路5と、この出力に対してビタビ復号処理を行うビタビ復号回路6と、この出力における複数の等化レベルに応じたタイミングを生成するターゲットデコーダ8と、各等化レベルに対するタイミングとそれに対応する等化レベル目標値を選択するターゲット選択回路11と、選択したタイミングに従い、選択した等化レベル目標値とFIRフィルタ回路5の出力値との間の誤差値を演算する誤差演算回路12と、求めた誤差値からタップ係数値を演算し、FIRフィルタ回路5へのタップ係数の更新を行う係数制御回路13とを備える。

(もっと読む)

PRML復号装置、PRML復号方法

【課題】PRML復号装置の内部構成を変更せずに、アシンメトリやレベル変動の問題を解決し、また適切な信号評価を同時に実現する。

【解決手段】

PRML検出における差動メトリックdMをパタンごとに分類して低域成分を補正する。そして補正された差動メトリックから検出されたビット値を修正することで、信号のアシンメトリなどの非線形成分を除去したビット検出がなされるようにし、また補正された差動メトリックを用いてビットエラーレートと相関のあるジッタ指標を算出する。

(もっと読む)

101 - 120 / 152

[ Back to top ]