Fターム[5E001AB03]の内容

セラミックコンデンサ (14,384) | 型 (2,709) | 積層型 (2,329)

Fターム[5E001AB03]に分類される特許

81 - 100 / 2,329

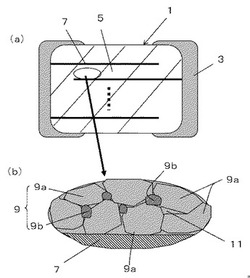

誘電体磁器およびコンデンサ

【課題】 比誘電率の温度変化率の小さい誘電体磁器とそれを用いたコンデンサを提供する。

【解決手段】 チタン酸バリウムを主成分とする主結晶粒子9aと酸化イッテルビウムの結晶粒子9bとを有するとともに、チタン100モルに対してマグネシウムをMgO換算で0.5〜3.0モル含有してなり、X線回折チャートにおいて、チタン酸バリウムの面指数(110)の回折強度に対する酸化イッテルビウムの面指数(222)の回折強度が0.5〜3.0%である。

(もっと読む)

コンデンサ

【課題】絶縁耐力を向上できるコンデンサを提供する。

【解決手段】コンデンサ1は、1対の内部電極7と、当該1対の内部電極7間に位置する誘電体5と、を有する。誘電体5は、粒径が130nm以下の複数の第1の無機粒子15と、粒径が160nm以上の複数の第2の無機粒子17と、を含む。第2の無機粒子17同士は、複数の第1の無機粒子15を互いに結合してなる三次元マトリクス構造を介して連結されている。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】チップの密閉性が向上し、信頼性に優れた積層セラミック電子部品を提供する。

【解決手段】積層セラミック電子部品は、誘電体層1を含むセラミック本体10と、セラミック本体10内で誘電体層1を介して対向配置される第1及び第2内部電極21,22と、第1内部電極21と電気的に連結された第1外部電極31、及び第2内部電極22と電気的に連結された第2外部電極32と、を含む。第1及び第2外部電極31,32は導電性金属及びガラスを含み、第1及び第2外部電極31,32のうちの少なくとも一つを厚さ方向に3等分する際、中央部領域の面積に対してガラスが占める面積は35から80%である。

(もっと読む)

積層型チップキャパシタ

【課題】本発明は、積層型チップキャパシタに関する。

【解決手段】積層型チップキャパシタは、積層方向に連続配置された複数の内部電極が1つのブロックを成し、そのブロックが繰り返し積層され、前記各内部電極のリード数の平均は全体外部電極数の1/2より少なく、積層方向に(上下に)隣接した相違な極性の内部電極のリードは積層方向からみると常に相互隣接するように配置され、同じ極性を有する内部電極は前記外部電極により全て電気的に連結されている。

(もっと読む)

積層セラミック電子部品

【課題】本発明は、アーク(arc)の発生を極力抑制することができる高圧用積層セラミック電子部品に関する。

【解決手段】本発明によると、誘電体層を含み、上記誘電体層の積層方向に互いに対向する第1及び第2主面、上記第1及び第2主面を連結し、互いに対向する長さ方向の第3、第4側面及び幅方向の第5、第6側面を有する、長さ1.79mm以下、幅1.09mm以下のセラミック本体と、上記セラミック本体内で、上記誘電体層を挟んで互いに対向するように配置される第1及び第2内部電極と、上記第1内部電極と電気的に連結された第1外部電極及び上記第2内部電極と電気的に連結された第2外部電極と、を含み、上記第1及び第2外部電極のうち少なくとも一つにおいて、上記セラミック本体の両端部から長さ方向に形成された最短長さをA、最長長さをBWと規定すると、0.5≦A/BW<1.0の関係を満たす積層セラミック電子部品が提供される。

(もっと読む)

積層セラミックキャパシタ

【課題】本発明は、積層セラミックキャパシタに関する。

【解決手段】本発明の一実施形態による積層セラミックキャパシタは、セラミック素体と、重なる領域を有し上記重なる領域が上記セラミック素体の一面に露出される引出部をそれぞれ有する第1及び第2の内部電極と、上記セラミック素体の一面に形成され上記引出部とそれぞれ連結される第1及び第2の外部電極と、上記セラミック素体のうち上記引出部の露出面に形成される絶縁層と、を含むことができる。

(もっと読む)

セラミックペーストおよびセラミックグリーンシート

【課題】ポリビニルアセタールを含み、塗膜強度の向上と粘度安定性とが両立した積層セラミックコンデンサ用セラミックペーストを提供する。

【解決手段】以下の式(I)に示す部分構造を分子内に3以上有する有機ホウ素化合物を含むペーストとする。式(I)において、mは0または1、nは1〜3の整数、R1およびR2は互いに独立して、水素原子または置換されていてもよいアルキル基である。R1およびR2は、互いに結合していてもよい。 (もっと読む)

(もっと読む)

電極用銅ペースト。

【課題】現状では、銀ペーストの変わる銅導電性ペーストが開発されているが、接着強度に問題がある。接着強度が強く、特に、フェライトコアーの外部電極として使用できる銅導電性ペーストの提供。

【解決手段】微細銅粉を主体とし、金属或はこれ等の酸化物、ガラスフリット、ビビクルで構成された銅導電性ペーストに、更に、多くの気孔率を有する炭化珪素及び多孔質セラミックス等を添加することで、微細銅粉との、結合を強め銅導電性ペーストとして素子との密着強度を向上させる。

(もっと読む)

積層セラミックキャパシタの回路基板実装構造

【課題】本発明は、積層セラミックキャパシタの回路基板実装構造に関する。

【解決手段】本発明の積層セラミックキャパシタの回路基板実装構造は、内部電極が形成された誘電体シートが積層され、前記内部電極に並列接続される外部端子電極が両端部に形成された積層セラミックキャパシタの回路基板実装構造であって、前記積層セラミックキャパシタの内部電極と回路基板が水平方向になるように配置され、前記外部端子電極と回路基板のランドとが導電材によって接合され、前記基板とキャパシタの下面との間の間隔Taと、積層セラミックキャパシタの下部側のカバー層の厚さTcとの合計より前記導電材の接合高さTsが低く形成されることによって振動音を著しく減少させることができる作用効果を発揮することができる。

(もっと読む)

積層セラミックキャパシタ

【課題】本発明は、積層セラミックキャパシタに関する。

【解決手段】本発明の一実施形態による積層セラミックキャパシタは、セラミック素体と、互いに重畳される領域がセラミック素体の一面に露出する引出部をそれぞれ有する第1及び第2内部電極121、122と、上記セラミック素体の一面から内部電極121、122が積層されるy方向の側面に延長されて形成され、上記引出部とそれぞれ連結される第1及び第2外部電極131、132と、上記セラミック素体の一面に形成される絶縁層140とを含む。

(もっと読む)

積層貫通コンデンサ

【課題】高周波帯域でのノイズの除去能力を向上した積層貫通コンデンサを提供すること。

【解決手段】積層貫通コンデンサ1は、誘電体層5を積層してなるコンデンサ素体2と、主電極部10a及び引き出し電極部10b,10cを有する信号用内部電極10と、主電極部10aと対向する主電極部20a及び引き出し電極部20b,20cを有する接地用内部電極20と、信号用内部電極10に接続される信号用端子電極3,3と、接地用内部電極20に接続される接地用端子電極4,4とを備えている。積層貫通コンデンサ1では、信号用内部電極10の主電極部10aが、積層方向に対向する接地用内部電極20の主電極部20aに向かって屈曲しており、また、接地用内部電極20の主電極部20aが、信号用内部電極10の主電極部10aと同じ方向に屈曲している。

(もっと読む)

誘電体磁器組成物およびセラミック電子部品

【課題】 誘電体層を薄層化した場合であっても、良好な特性を示す誘電体磁器組成物および電子部品を提供すること。

【解決手段】ペロブスカイト型化合物(ABO3)を含有し、化合物100モルに対して、各酸化物換算で、RA2O3(RAはDy、GdおよびTbから選ばれる1つ以上)を0.6〜2.5モル、RB2O3(RBはHoおよび/またはY)を0.2〜1.0モル、RC2O3(RCはYbおよび/またはLu)を0.1〜1.0モル含有し、Mg酸化物を、Mg換算で0.8〜2.0モル、Si化合物をSi換算で1.2〜3.0モル含有し、RA2O3の含有量(α)、RB2O3の含有量(β)およびRC2O3の含有量(γ)が、1.2≦α/β≦5.0、0.5≦β/γ≦10.0である誘電体磁器組成物。該誘電体磁器組成物は、誘電体層厚みが5.0μm以下の電子部品に適用することが好ましい。

(もっと読む)

積層セラミックコンデンサ用の導電ペーストおよびその製造方法

【課題】溶剤の選択幅が広い積層セラミックコンデンサ用の導電ペースト、およびその製造方法を提供する。

【解決手段】導電ペーストは、溶剤と、平均粒径が10〜200nmかつニッケルが50原子%以上かつ金属粒子とを含む。溶剤は水と極性溶媒との混合溶液であり、金属粒子の表面には、上記溶剤に金属粒子を分散させる分散剤が付着する。

(もっと読む)

電子部品の製造方法

【課題】電極の膜厚を所定厚みに容易に調整することができ、かつ外観形状も良好で安定した電気特性を得ることができる電子部品の製造方法を実現する。

【解決手段】導電性ペーストが、導電性粉末と、加熱により粘度が低下するバインダ樹脂と、溶剤とを含有する。部品素体1を第1の保持部材2に保持させ、溶剤が揮発しないような所定温度に加熱して高温状態とする(図4(a))。部品素体1の端部1aを平板6上のペースト層7に所定時間、接触させ、端部1aに導電性ペーストを塗布し、次いで、部品素体1をペースト層7から引き離し、端部1aに導電膜8aを形成する(図4(b)、図4(c))。その後、導電膜8aを乾燥させて外部電極9aを得る(図4(d))。部品素体1を反転させ、同様の方法で端部1bにも外部電極を形成する。

(もっと読む)

金属粉末、その製造方法、及びその金属粉末からなる内部電極を含む積層セラミックキャパシタ

【課題】本発明は、積層セラミックキャパシタの内部電極に用いられる材料と、誘電層に用いられる材料との収縮率差による様々な問題を解決する。

【解決手段】表面にグラフェン131が不規則に形成された金属粉末121を、積層セラミックキャパシタの内部電極の材料として用いて、グラフェン131が形成されていない金属粉末の表面でのみネッキングが起こるようにし、金属粉末のネッキングを遅延させ、内部電極の収縮を制御することにより、内部電極の厚さを減らし、短絡及びクラックなどを減少させる。

(もっと読む)

積層セラミックコンデンサ及びその製造方法

【課題】本発明は、誘電層内に形成された内部金属電極層を含み、前記内部金属電極層の間に導電層を含む積層セラミックコンデンサとその製造方法に関する。

【解決手段】本発明によると、10nm以下の非常に薄い導電層を内部金属電極層の間に形成することで、MLCC内部金属層の間の接触を防止してショート発生による製作損失を減らし、熱安定性を向上させることができる。従って、高機能で小型軽量の高容量積層セラミックコンデンサ(MLCC)を要求する市場の需要に対して優れた信頼性を有する。

(もっと読む)

積層コンデンサ及びコンデンサ内蔵配線基板

【課題】特性が異なる複数の領域からなる積層コンデンサを一体的に作製し、周波数特性の広帯域化を容易に実現可能な積層コンデンサを提供する。

【解決手段】本発明の積層コンデンサは、誘電体層20〜22と内部電極層30〜33とを交互に積層してなり、第1領域R1及び第2領域R2を含むコンデンサ本体部と、アレイ状に配置された全貫通型のビア導体40、41、50、51と、その両端部に接続される外部電極60、61、70、71を備えている。第1ビア導体群であるビア導体40、41は、第1領域R1及び第2領域R2の内部電極層30〜33と電気的に接続され、第2ビア導体群であるビア導体50、51は、第1領域R1の内部電極層30、31と電気的に接続され、かつ第2領域R2の内部電極層32、33と電気的に接続されない。ビア導体50、51は、第2領域R2におけるビア径が第1領域R1におけるビア径よりも小さくなるように形成される。

(もっと読む)

積層貫通コンデンサ

【課題】信号用内部電極の湾曲を抑制した積層貫通コンデンサを提供すること。

【解決手段】積層貫通コンデンサ1は、コンデンサ素体2と、信号用内部電極10と、主電極部20aを有する接地用内部電極20と、非形成領域5e,5f及び信号用内部電極10の両外縁10e,10f上に配置される信号用段差吸収層12と、非形成領域5c,5d及び主電極部20aの周縁22a上に配置される接地用段差吸収層22と、信号用端子電極3,3と、接地用端子電極4,4とを備えている。接地用内部電極20の主電極部20aは、一方の縁部21bの厚みが他方の縁部21aの厚みよりも薄く、主電極部20aの周縁22a上に配置される接地用段差吸収層22は、一方の縁部21b上の厚みが他方の縁部21a上の厚みよりも厚くなっている。

(もっと読む)

積層型コンデンサ

【課題】材料的な制約を受けることなく且つ汎用的な構造を含む場合にも適用可能であって、電歪振動を抑制することが可能な積層型コンデンサを提供すること。

【解決手段】誘電体セラミックスによって形成された素体及びその素体内部においてセラミックス層を挟んで重なりあうように配置された複数の内部電極4a,4bを有する積層体2と、を備え、複数の内部電極4a,4bを含むコンデンサ領域CAと、複数の内部電極4a,4bによって生じる電歪現象を低減させ音鳴きを抑制するための第一抑制領域EA及び第二抑制領域DAとが形成されており、第一抑制領域EAはコンデンサ領域CAに隣接し、第二抑制領域DAの厚みは複数の内部電極4a,4bの配置態様に応じて定められるものである。

(もっと読む)

積層セラミック電子部品の内部電極用導電性ペースト及びこれを利用した積層セラミック電子部品

【課題】本発明は積層セラミック電子部品の内部電極用導電性ペースト及びこれを利用した積層セラミック電子部品に関する。

【解決手段】内部電極用導電性ペーストに窒化シリコーン、窒化ホウ素、窒化アルミニウム及び窒化バナジウムからなる群から選択される1つ以上の窒化物を添加して内部電極の収縮開始温度を上昇させることで、上記内部電極用導電性ペーストを利用した積層セラミック電子部品の信頼性を向上させることができる。

(もっと読む)

81 - 100 / 2,329

[ Back to top ]