Fターム[5E001AB03]の内容

セラミックコンデンサ (14,384) | 型 (2,709) | 積層型 (2,329)

Fターム[5E001AB03]に分類される特許

121 - 140 / 2,329

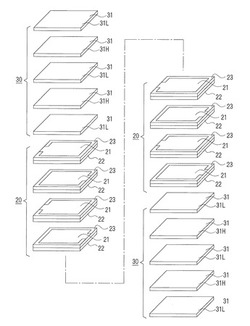

積層セラミックコンデンサ

【課題】耐湿性の良好な積層セラミックコンデンサを提供する。

【解決手段】内部電極21が形成された複数の第1のセラミック層22を積層してなる有効層20と、前記有効層20を挟むように内部電極が形成されていない複数の第2のセラミック層31を積層してなる一対の保護層30とを有する積層体10と、該積層体10の外面に形成され前記内部電極21と電気的に接続した外部電極40とを備えた積層セラミックコンデンサにおいて、前記第1のセラミック層21及び第2のセラミック層31はそれぞれSiO2が添加されたセラミック材料からなり、且つ、前記保護層は相対的に互いにSiO2濃度が異なる複数の第2のセラミック層31H,31Lを積層してなる。

(もっと読む)

内部電極用導電性ペースト組成物及びそれを含む積層セラミック電子部品

【課題】内部電極層用導電性ペースト組成物及びそれを含む積層セラミックコンデンサを提供する。

【解決手段】本発明による内部電極層用導電性ペースト組成物は、金属粉末と、上記金属粉末よりも平均粒径が小さく、融点が高い高融点金属酸化物粉末と、を含むことができる。本発明による内部電極用導電性ペースト組成物は、内部電極の焼成収縮温度を高め、内部電極の連結性を向上させることができる。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】本発明は、電極連結性を制御して容量を確保することができる積層セラミック電子部品及びその製造方法を提供する。

【解決手段】本発明による積層セラミック電子部品は、セラミック本体10と、この前記セラミック本体10の内部に形成され、中央部70及び前記この中央部70から縁に向かって薄くなるテーパ部50を有する内部電極30、31と、を含む。前記内部電極30、31の面積に対する前記テーパ部50の面積の比率は、35%以下であることを特徴とする。本発明によると、小型及び高容量の積層型セラミックキャパシタにおいても、電極連結性を制御することにより所望の容量を確保することができる。

(もっと読む)

積層セラミック電子部品の内部電極用導電性ペースト及びこれを含んで製造された積層セラミック電子部品

【課題】本発明は、積層セラミック電子部品の内部電極用導電性ペースト及びこれを含んで製造された積層セラミック電子部品に関する。

【解決手段】本発明は、導電性金属粉末100重量部と、有機バインダー0.6から2.4重量部と、を含むことを特徴とする。本発明による積層セラミック電子部品の内部電極用導電性ペーストを用いると、積層セラミック電子部品の内部ストレスを減少させて積層セラミック電子部品においてクラックの発生を抑制することができる。

(もっと読む)

積層セラミック電子部品

【課題】 セラミック素体に特別な加工を施さなくても、所望の膜厚分布を有する薄層の外部電極が得られる積層セラミック電子部品の外部電極構造を提供する。

【解決手段】 主要な表面5と、主要な裏面6と、2つの端面3,4と、2つの側面を有する略直方体のセラミック素体2の両端に、端面3,4を覆う端面部分と4つの側面に回り込んで形成された回り込み部分とを有する端子電極を備えた積層セラミック電子部品であって、端子電極は、端面部分及び回り込み部分に凹部1a、1bが形成されており、端面部分の凹部の幅は素体の幅の30%以上でありかつ深さは端面部分の厚さの10ないし50%であり、回り込み部分の凹部の幅は回り込み部分の長さの30%以上でありかつ深さは回り込み部分の厚さの10ないし40%であることを特徴とする積層セラミック電子部品。

(もっと読む)

積層セラミックコンデンサ

【課題】 外部電極における下地電極の厚みが薄い場合でも、湿中負荷試験における不良を少なくできる積層セラミックコンデンサを提供する。

【解決手段】 誘電体層5と内部電極層7とが交互に積層されたコンデンサ本体1と、該コンデンサ本体1の前記内部電極層7が露出した端面1aおよび該端面1aに隣接する側面1bに設けられた下地電極3および該下地電極3上に設けられた被覆電極とを含む外部電極とを具備する積層セラミックコンデンサにおいて、前記下地電極3は、銅を主成分とし、かつ亜鉛を含み、緻密度が96%以上であり、前記下地電極3の前記コンデンサ本体1の前記端面1a側における厚みが20μm以下である。

(もっと読む)

酸化物導電体を用いた酸化物導電体ペースト及びそれを用いた積層電子部品

【課題】

積層セラミックコンデンサの内部電極の導電材の収縮は通常異なるので、収縮量の差により内部電極が途切れ、クラックやはがれの原因になってしまう。

【解決手段】

酸化物導電ペーストの導電材料として誘電体と焼結温度が近い亜鉛を含む酸化物を用いることにより、被覆率の高い内部電極を持つ積層電子部品が得られた。さらに、Al、Ga、Si、Snのいずれかを含む亜鉛を主成分とした導電性酸化物を用いることにより、必要とする導電性、焼結温度、焼結挙動を制御することが可能になる。これにより、途切れの無い導電性の良い内部電極をもつ積層電子部品が得られた。

(もっと読む)

積層コンデンサ

【課題】めっき液の浸入を抑えて絶縁抵抗不良の発生を抑制できる貫通コンデンサを提供する。

【解決手段】貫通コンデンサ1では、信号用内部電極6の第1連結部13Aの幅が第1主電極部11A及び第1引出部12Aの幅よりも狭くなっている。これにより、素体2の端面にめっき層を形成する際、幅狭な第1連結部13Aによってめっき液が信号用内部電極6の第1主電極部11Aに到達することを抑制できる。また、貫通コンデンサ1では、第2連結部13Bの幅が第1連結部13Aの幅と略同等になっている。これにより、幅狭な第2連結部13Bによってめっき液が接地用内部電極の第2主電極部11Bに到達することを抑制できる。さらに、仮にめっき液が浸入した場合であっても、第1主電極部11Aへのめっき液の到達時間と第2主電極部11Bへのめっき液の到達時間とを揃えることが可能となる。

(もっと読む)

チップ型積層キャパシタ

【課題】本発明は、小型化及び高容量化を具現すると共に電源の印加時に内部電極間に生じる振動音を低減することができるチップ型積層キャパシタに関する。

【解決手段】本発明の一実施形態によるチップ型積層キャパシタは、グレインの平均粒径の10倍以上で3μm以下の厚さで形成される誘電体層を含むセラミック本体と、上記セラミック本体の長さ方向の両端部面に形成される第1及び第2の外部電極と、上記第1及び第2の外部電極から上記セラミック本体の長さ方向内側のL−W平面上に伸びて形成され相違する長さを有する第1及び第2のバンド部と、上記第1及び第2の外部電極から上記セラミック本体の長さ方向内側のL−T平面上に伸びて形成され相違する長さを有する第3及び第4のバンド部と、を含むことができる。

(もっと読む)

積層セラミックキャパシタ

【課題】本発明は、積層セラミックキャパシタに関する。

【解決手段】本発明の一実施形態による積層セラミックキャパシタは、複数の誘電体層が厚さ方向に積層された積層本体と、当該積層本体の内部に形成され上記誘電体層を介して対向して配置され一端が当該積層本体の対向する側面に交互に露出される第1及び第2の内部電極を含む内部電極層と、を含み、上記積層本体の長さ方向及び厚さ方向の断面から見るとき、上記積層本体の面積をCA1とし、上記第1及び第2の内部電極が厚さ方向に重なる第1の容量形成部以外の部分である第1のマージン部の面積をMA1とすると、CA1に対するMA1の比(MA1/CA1)が0.07〜0.20であることができる。

(もっと読む)

チップ型積層キャパシタ

【課題】本発明は、小型化及び高容量化を具現するとともに、音響ノイズを低減するチップ型積層キャパシタに関する。

【解決手段】本発明の一実施例によるチップ型積層キャパシタは、グレインの平均サイズの10倍以上であり、3μm以下の厚さに形成される誘電体層が積層されて形成されるセラミック本体と、上記セラミック本体の長さ方向の両端部に形成され、相違する極性を有する第1及び第2外部電極と、一端は上記第2外部電極が形成される上記セラミック本体の一端部面と第1マージンを形成し、他端は第1外部電極に引き出される第1内部電極と、一端は上記第1外部電極が形成される上記セラミック本体の他端部面と第2マージンを形成し、他端は第2外部電極に引き出される第2内部電極と、を含み、上記第1マージンと第2マージンとは、200μm以下の条件で相違する幅を有することができる。

(もっと読む)

積層型チップ素子及びその製造方法

【課題】本発明は、積層型チップ素子及びその製造方法に関する。

【解決手段】本発明は、導電性物質で形成される内部電極を有するシートが複数積層されてなる積層体と、前記積層体の両側に備えられる外部電極と、前記内部電極から延長され、前記内部電極を前記外部電極に電気的に連結させる接続電極と、を含む積層型チップ素子であって、前記接続電極は、前記内部電極から延長されるが、前記内部電極より薄い厚さで延長されるメッキ液浸透防止部と、前記メッキ液浸透防止部から延長されるが、前記外部電極に向かって厚さが次第に拡大される形に延長される接触補強部と、を含む積層型チップ素子及びその製造方法を開示する。

本発明によると、外部から内部電極へのメッキ液浸透を防止することができ、熱衝撃に対する耐久性を向上させることができ、内部電極と外部電極との間の接触性を高めることができる。

(もっと読む)

電子部品の製造方法

【課題】表層電極において接続信頼性の高い突起状導体を形成することができる電子部品の製造方法を提供すること。

【解決手段】セラミックコンデンサのカバー層部108は、各ビア導体131の周囲となる位置のセラミック絶縁層150間に複数の段差補正用絶縁層151を介在させた状態で形成される。フォトレジストフィルム180の露光時には、突起状導体を形成するための形成予定領域R1の外側領域R2を感光させるべく入射したレーザ202が、表層電極111に当たって向きを変え形成予定領域R1の反対側である外側領域R2に反射するように露光を行う。フォトレジストフィルム180を現像して、開口部を有するめっきレジストを形成し、開口部を介して露出する表層電極111に対してめっきを施すことにより突起状導体を形成する。

(もっと読む)

電子部品

【課題】中間層部の緻密化を図り、信頼性の高い電子部品を提供すること。

【解決手段】セラミックコンデンサ101は、複数のセラミック誘電体層105及び複数の内部電極層141,142を積層してなる電極積層部107と、電極積層部107の外面を覆うように設けられたカバー層部108と、電極積層部107の積層途中となる位置に設けられた中間層部109と、電極積層部107の積層方向に延びて複数の内部電極層141,142に接続された複数のコンデンサ内ビア導体131,132とを備える。中間層部109は、自身の厚さの1/10以下の粒径を持つ金属粒子154がセラミック粒子に対して1体積%以上30体積%以下の割合で混合された材料により形成されている。

(もっと読む)

電子部品及びその製造方法

【課題】拘束層材料と素子層材料の電子特性との相対的な関係を選択することにより、側電極の深さを全体的な電気の影響を最小限に抑える。

【解決手段】電子部品およびその製造方法は、まず、第二電子特性を有する拘束層を第一電子特性を有する素子層に形成する。前記電子部品の特性は、前記第一電子特性によって主に影響される。その後、両方の拘束層及び素子層を焼結温度で焼結する。第一電子特性と第二電子特性との関係を選択することにより、電子部品の特性が安定になる。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】本発明は、信頼性に優れた積層セラミック電子部品及びその製造方法に関する。

【解決手段】本発明による積層セラミック電子部品は、内部電極及び誘電体層を含み、上記内部電極の一部が露出する接続面を一つ以上有する本体部と、上記接続面に結合して上記内部電極と電気的に連結される外部電極と、上記接続面において露出する内部電極の少なくとも一部を遮蔽するように上記接続面に用意される保護層と、を含み、上記内部電極全体の幅に対して上記保護層によって遮蔽される内部電極の露出した幅の比率は、0.8から0.9倍を有する。本発明によると、内部電極が外部に露出する本体部の表面における外部電極との距離が相対的に近い領域に内部電極を遮蔽することができる保護層を用意することで、異物浸透による絶縁抵抗の劣化、信頼性の低下及び接触性の不良を防止することができる。

(もっと読む)

積層コンデンサ及び積層コンデンサの製造方法

【課題】焼付層の応力によるクラックの発生と、めっき液の浸入による絶縁不良の発生とを防止できる積層コンデンサ及び積層コンデンサの製造方法を提供する。

【解決手段】積層コンデンサ1では、内部電極6A,6Bから積層体2の端面に引き出される引出導体12A,12Bの全部を覆うように焼付層17A,17Bが形成されている。これにより、めっき層18A,18Bの形成の際にめっき液が内部電極6A,6B側に浸入することが防止され、絶縁不良の発生を防止できる。また、焼付層17A,17Bがダミー電極13C,13F,13G,13Hの一部を覆っているので、焼付層17A,17Bの面積を抑えることができる。したがって、焼付層17A,17Bに過剰な応力が生じることを抑制でき、焼付層17A,17Bの応力によるクラックの発生を防止できる。

(もっと読む)

カット刃、電子部品の製造方法、及び電子部品の製造装置

【課題】セラミックブロックを切断する際の切断方向を容易に制御することができるようにする。

【解決手段】カット刃1は、一方の刃部2aの表面粗さが他方の刃部2bの表面粗さよりも細かくなるように形成されており、一方の刃部2aの表面粗さは、他方の刃部2bの表面粗さの1.5倍以上が好ましい。また刃部2a、2bの表面粗さは、算術平均粗さに換算し0.2μm以下であるのが好ましい。前記切断されたときに、表面粗さの細かい方の刃部2aが、分割された一方のセラミックブロック3aに引っ張られるように、カット刃1を切断位置に配する。

(もっと読む)

強誘電体薄膜の製造方法

【課題】(100)面に優先的に結晶配向が制御された強誘電体薄膜をシード層やバッファ層を設けることなく、簡便に得ることが可能な、強誘電体薄膜の製造方法を提供する。

【解決手段】結晶面が(111)軸方向に配向した下部電極を有する基板の下部電極上に、強誘電体薄膜形成用組成物を塗布し、加熱して結晶化させることにより下部電極上に強誘電体薄膜を製造する方法の改良であり、強誘電体薄膜が(100)面に優先的に結晶配向が制御された配向制御層により構成され、配向制御層を結晶化後の層厚を35nm〜150nmの範囲内にすることにより形成することを特徴とする。

(もっと読む)

積層電子部品

【課題】静電容量の低下を抑制し、誘電体層と電極層との密着性を向上させてクラック等を防止できる積層電子部品を提供すること。

【解決手段】誘電体層(2)とNiが主成分である電極層(3)とが積層された素子本体を有する積層電子部品であって、素子本体は、Ni酸化物を主成分とする第1相(21)と、Ni以外の金属酸化物を主成分とする第2相(22)と、を有し、素子本体を誘電体層および電極層に対して垂直な切断面において、積層方向と垂直な方向では、第1相は電極層と接し、第2相は、電極層および/または第1相と接し、第1相の少なくとも一部は、電極層と第2相とに挟まれ、積層方向と垂直な方向において、第1相が電極層と接しかつ第2相と接している長さをLnioとし、積層方向と垂直な方向における電極層の長さをLniとすると、(ΣLnio)/2Lniが0.05〜12%である。

(もっと読む)

121 - 140 / 2,329

[ Back to top ]