Fターム[5E001AF02]の内容

セラミックコンデンサ (14,384) | 端子、リード (1,238) | 素子からの引出し部 (255)

Fターム[5E001AF02]に分類される特許

1 - 20 / 255

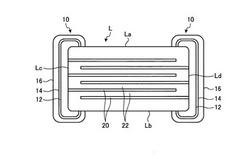

チップ型電子部品

【課題】はんだ喰われを防止しつつ、応力緩和が可能な端子電極を有するチップ型電子部品を提供すること。

【解決手段】チップ型電子部品Cは、セラミック素体Lと、セラミック素体Lの内部に配置され、かつ、セラミック素体Lの表面に一部が露出した内部電極20と、セラミック素体の表面に配置された端子電極10とを含み、端子電極10は、第1の導電性材料12a、12bを含むとともに、内部電極の露出した部分および内部電極が露出しているセラミック素体の表面を覆う第1の電極層12と、第1の電極層12よりもセラミック素体の表面から離れた位置に配置される導電性めっき層14と、はんだ成分を含む第2の導電性材料16aと樹脂16cとを含むとともに、導電性めっき層14よりもセラミック素体の表面から離れた位置に配置される第2の電極層16と、を含む。

(もっと読む)

電子部品

【課題】Niめっき層中に吸蔵された水素を低減し、IR特性が劣化しにくく、はんだ付け性に優れたSn層を有する外部端子電極をもつ電子部品を提供する

【解決手段】セラミック層と、内部電極と、前記内部電極と電気的に接続される外部電極層を有する電子部品において、前記外部電極層上に設けられるNiめっき層と、前記Niめっき層上に設けられるSnを主成分とするSn層と、を備え、前記Sn層は底部を有する開孔部を備えることを特徴とする電子部品。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】固着強度を高めて曲がりクラックを防止できる積層セラミック電子部品及びその製造方法を提供する。

【解決手段】本発明による積層セラミック電子部品は、複数の誘電体層が積層されたセラミック素体10と、セラミック素体10内で複数の誘電体層の少なくとも一面に形成され、セラミック素体10の一面から露出する第1及び第2内部電極21,22と、セラミック素体10の一面に形成され、第1及び第2内部電極21,22の露出部により第1及び第2内部電極21,22とそれぞれ電気的に接続される第1及び第2外部電極31,32とを含み、セラミック素体10の一面の広さに対する第1又は第2外部電極31,32の広さの比が10〜40%である。

(もっと読む)

4端子型セラミックコンデンサ

【課題】 実装面積をより小さくすることができ、かつ、耐振動性を向上させることが可能な4端子型セラミックコンデンサを提供する。

【解決手段】 4端子型セラミックコンデンサ1は、直方体状のセラミックコンデンサ部10と、対向する側面10a,10bに形成された一対の電極20,21と、一対の電極20,21それぞれに接続されたヘアピン状のリード線30,31とを備える。リード線30(31)は、側面10a(10b)の長手方向に伸びる一対の直線部30a,30b(31a,31b)と、該一対の直線部30a,30b(31a,31b)の端部同士を滑らかに接続する湾曲部30c(31c)とを含む。一方の直線部30a(31a)は電極20(21)に接続され、他方の直線部30b(31b)は電極20(21)と離間して設けられ、湾曲部30c(31c)は、平面視した場合に、側面10a(10b)に対して垂直な方向に伸びる。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】メッキ液の浸透が抑制されて信頼性に優れた積層セラミック電子部品及びその製造方法を提供する。

【解決手段】本発明の積層セラミック電子部品は、セラミック本体と、上記セラミック本体の内部に積層配置された内部電極と、上記セラミック本体上に形成された第1外部電極層、上記第1外部電極層上に形成された第2外部電極層、上記第2外部電極層上に形成された第3外部電極層を含む外部電極とを含む。

(もっと読む)

積層セラミック電子部品の製造方法

【課題】本発明は積層セラミック電子部品の製造方法に関する。

【解決手段】本発明はチップ状のセラミック素体を設ける段階と、上記セラミック素体の外側に第1外部電極を形成する段階と、上記第1外部電極上に導電性金属を含む第2外部電極を形成する段階と、上記第2外部電極上に金属を含む半田ペーストを塗布して金属コーティング膜を形成する段階とを含む積層セラミック電子部品の製造方法を提供する。

本発明による積層セラミック電子部品の製造方法は、外部電極上に銅(Cu)またはニッケル(Ni)メッキ層を形成することで、メッキ液浸透または銅(Cu)外部電極の浸出(leaching)不良を防ぎ、信頼性に優れた積層セラミック電子部品を具現することができる。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】本発明は外部電極のカバレッジ及び固着強度に優れた積層セラミック電子部品及びその製造方法に関する。

【解決手段】本発明はセラミック本体のカバー領域及び活性領域に外部電極と接続するダミー電極を形成することを特徴とし、本発明によると、外部電極のカバレッジ及び固着強度に優れた積層セラミック電子部品が得られる。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】本発明は、還元雰囲気の熱処理を要しない積層セラミック電子部品及びその製造方法に関する。

【解決手段】本発明は、内部電極及び外部電極の材料として導電性酸化物を使用し、外部電極上に弾性を有する導電層を形成することを特徴とする。本発明による積層セラミックキャパシタは、大気雰囲気下で焼成を行うことができるため、製造工程が単純になり、製造費用が節減されることができる。

(もっと読む)

チップ型電子部品及びチップ型電子部品の実装構造

【課題】端子電極における内部応力の低減と、はんだ食われの防止及び接触抵抗の低減とを両立できるチップ型電子部品及びこれを用いた実装構造を提供する。

【解決手段】積層コンデンサ1において端子電極3は、CuコートされたNi粉を含有する第1の樹脂電極層3aが、最外層であるSnめっき層3bの内側に隣接している。この第1の樹脂電極層3aに含まれるNi粉はCuによってコートされている。第1の樹脂電極層はCu粉を含有しても良い。最外層はSnコートされたNi粉を含有する第2の樹脂電極層としても良い。そして、端子電極はNiめっき層を有していない。

(もっと読む)

表面実装型受動素子部品、部品キャリアテープ、部品内蔵配線板

【課題】板厚み内部に位置させたとき部品端子からの導電路の配置密度を向上させること。

【解決手段】直方体状の素子部材と、素子部材の長手方向の一方向側の端部面である第1の端部面上に、および該第1の端部面に連なる素子部材の少なくとも上面上および下面上のそれぞれ一部に第1の端部面上と連なるように設けられた第1の端子電極と、素子部材の長手方向の他方向側の端部面である第2の端部面上に、および該第2の端部面に連なる素子部材の少なくとも上面上および下面上のそれぞれ一部に前記第2の端部面上と連なるように設けられた第2の端子電極と、を具備し、第1の端子電極および第2の端子電極が、いずれも、素子部材の上面上に設けられている面積の方が、素子部材の下面上に設けられている面積よりも広い。

(もっと読む)

コンデンサ及びその製造方法

【課題】ビア電極と表層電極との接続強度を高め、接続信頼性の高いコンデンサを提供する。

【解決手段】セラミックコンデンサ101のコンデンサ本体104は、コンデンサ主面102及びコンデンサ裏面103を有し、複数のセラミック誘電体層105及び複数の内部電極層141,142を積層してなる。複数のコンデンサ内ビア導体131,132は、コンデンサ本体の積層方向に貫通形成された貫通ビア130内に充填形成されており、各内部電極層141,142に接続されている。貫通ビア130は、コンデンサ主面102側の開口に向かうに従って拡径するように形成された拡径部135を有する。表層電極111,112は、コンデンサ主面102上において拡径したビア導体131,132の端面全体を覆うように設けられている。

(もっと読む)

外部電極用導電性ペースト、これを用いた積層セラミック電子部品及びその製造方法

【課題】本発明は、外部電極用導電性ペースト、これを用いた積層セラミック電子部品及びその製造方法に関する。

【解決手段】本発明は、導電性金属粉末と、a+b+c=100、20≦a≦60、20≦b≦60及び2≦c≦25を満足する式a(Cu、Ni)−bZr−c(Al、Sn)を含む伝導性非晶質金属粉末と、を含む外部電極用導電性ペースト、これを用いた積層セラミック電子部品及びその製造方法を提供する。本発明によると、内部電極と外部電極との連結性低下及びガラスの励起によるメッキ不良を解決することができる。

(もっと読む)

電子部品及び選択方法

【課題】回路設計において高い自由度を得つつ、鳴きを抑制することができる電子部品及び選択方法を提供することである。

【解決手段】積層体11は、複数のセラミック層17が積層されてなり、z軸方向の両端に位置する上面及び底面、互いに対向する端面、並びに、互いに対向している側面を有している。コンデンサ導体30,32は、セラミック層17と共に積層され、かつ、セラミック層17を介して互いに対向している。第1の外部電極及び第2の外部電極は、一方の端面及び一方の側面のそれぞれに設けられ、かつ、コンデンサ導体30と接続されている。第3の外部電極及び第4の外部電極は、他方の端面及び他方の側面のそれぞれに設けられ、かつ、コンデンサ導体32と接続されている。

(もっと読む)

積層セラミックキャパシタ

【課題】本発明は、積層セラミックキャパシタに関する。

【解決手段】本発明の積層セラミックキャパシタは、セラミック素体と、このセラミック素体の内部に形成され、セラミック素体の第1面に露出し、この第1面に露出した領域のうち一部が重畳される引出部を有する第1及び第2内部電極121,122と、セラミック素体の第1面に形成され、引出部とそれぞれ連結される外部電極131、132と、セラミック素体110の第1面、この第1面と連結された第3面及び第4面にそれぞれ形成される絶縁層141〜144とを含む。上記引出部は、セラミック素体の第3面又は第4面と所定の間隔をおいて形成することができる。

(もっと読む)

積層セラミック電子部品

【課題】本発明は、アーク(arc)の発生を極力抑制することができる高圧用積層セラミック電子部品に関する。

【解決手段】本発明によると、誘電体層を含み、上記誘電体層の積層方向に互いに対向する第1及び第2主面、上記第1及び第2主面を連結し、互いに対向する長さ方向の第3、第4側面及び幅方向の第5、第6側面を有する、長さ1.79mm以下、幅1.09mm以下のセラミック本体と、上記セラミック本体内で、上記誘電体層を挟んで互いに対向するように配置される第1及び第2内部電極と、上記第1内部電極と電気的に連結された第1外部電極及び上記第2内部電極と電気的に連結された第2外部電極と、を含み、上記第1及び第2外部電極のうち少なくとも一つにおいて、上記セラミック本体の両端部から長さ方向に形成された最短長さをA、最長長さをBWと規定すると、0.5≦A/BW<1.0の関係を満たす積層セラミック電子部品が提供される。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】チップの密閉性が向上し、信頼性に優れた積層セラミック電子部品を提供する。

【解決手段】積層セラミック電子部品は、誘電体層1を含むセラミック本体10と、セラミック本体10内で誘電体層1を介して対向配置される第1及び第2内部電極21,22と、第1内部電極21と電気的に連結された第1外部電極31、及び第2内部電極22と電気的に連結された第2外部電極32と、を含む。第1及び第2外部電極31,32は導電性金属及びガラスを含み、第1及び第2外部電極31,32のうちの少なくとも一つを厚さ方向に3等分する際、中央部領域の面積に対してガラスが占める面積は35から80%である。

(もっと読む)

積層セラミックキャパシタ

【課題】本発明は、積層セラミックキャパシタに関する。

【解決手段】本発明の一実施形態による積層セラミックキャパシタは、セラミック素体と、重なる領域を有し上記重なる領域が上記セラミック素体の一面に露出される引出部をそれぞれ有する第1及び第2の内部電極と、上記セラミック素体の一面に形成され上記引出部とそれぞれ連結される第1及び第2の外部電極と、上記セラミック素体のうち上記引出部の露出面に形成される絶縁層と、を含むことができる。

(もっと読む)

電子部品の製造方法

【課題】電極の膜厚を所定厚みに容易に調整することができ、かつ外観形状も良好で安定した電気特性を得ることができる電子部品の製造方法を実現する。

【解決手段】導電性ペーストが、導電性粉末と、加熱により粘度が低下するバインダ樹脂と、溶剤とを含有する。部品素体1を第1の保持部材2に保持させ、溶剤が揮発しないような所定温度に加熱して高温状態とする(図4(a))。部品素体1の端部1aを平板6上のペースト層7に所定時間、接触させ、端部1aに導電性ペーストを塗布し、次いで、部品素体1をペースト層7から引き離し、端部1aに導電膜8aを形成する(図4(b)、図4(c))。その後、導電膜8aを乾燥させて外部電極9aを得る(図4(d))。部品素体1を反転させ、同様の方法で端部1bにも外部電極を形成する。

(もっと読む)

積層コンデンサ及びコンデンサ内蔵配線基板

【課題】特性が異なる複数の領域からなる積層コンデンサを一体的に作製し、周波数特性の広帯域化を容易に実現可能な積層コンデンサを提供する。

【解決手段】本発明の積層コンデンサは、誘電体層20〜22と内部電極層30〜33とを交互に積層してなり、第1領域R1及び第2領域R2を含むコンデンサ本体部と、アレイ状に配置された全貫通型のビア導体40、41、50、51と、その両端部に接続される外部電極60、61、70、71を備えている。第1ビア導体群であるビア導体40、41は、第1領域R1及び第2領域R2の内部電極層30〜33と電気的に接続され、第2ビア導体群であるビア導体50、51は、第1領域R1の内部電極層30、31と電気的に接続され、かつ第2領域R2の内部電極層32、33と電気的に接続されない。ビア導体50、51は、第2領域R2におけるビア径が第1領域R1におけるビア径よりも小さくなるように形成される。

(もっと読む)

積層セラミック電子部品

【課題】 セラミック素体に特別な加工を施さなくても、所望の膜厚分布を有する薄層の外部電極が得られる積層セラミック電子部品の外部電極構造を提供する。

【解決手段】 主要な表面5と、主要な裏面6と、2つの端面3,4と、2つの側面を有する略直方体のセラミック素体2の両端に、端面3,4を覆う端面部分と4つの側面に回り込んで形成された回り込み部分とを有する端子電極を備えた積層セラミック電子部品であって、端子電極は、端面部分及び回り込み部分に凹部1a、1bが形成されており、端面部分の凹部の幅は素体の幅の30%以上でありかつ深さは端面部分の厚さの10ないし50%であり、回り込み部分の凹部の幅は回り込み部分の長さの30%以上でありかつ深さは回り込み部分の厚さの10ないし40%であることを特徴とする積層セラミック電子部品。

(もっと読む)

1 - 20 / 255

[ Back to top ]