Fターム[5E001AF06]の内容

セラミックコンデンサ (14,384) | 端子、リード (1,238) | 積層電極間の接続 (726)

Fターム[5E001AF06]に分類される特許

61 - 80 / 726

チタン酸バリウム粉末、チタン酸バリウム粉末の製造方法およびこれを用いたセラミック電子部品

【課題】固相法において粒子径を300nm以上で制御でき、均質な粒子形状、低欠陥高結晶、高分散性、低粒子内空孔であり、かつ極微細粒子を含まない狭粒度分布であるチタン酸バリウム粉末、チタン酸バリウム粉末の製造方法およびこれを用いたセラミック電子部品を提供する。

【解決手段】本発明に係るチタン酸バリウム粉末は、ペロブスカイト構造を有し、直方体形状または直方体類似形状を有し、BET法により測定された比表面積が3.2m2/g以下であることを特徴とする。本発明に係るチタン酸バリウム粉末は、高結晶性、高分散性、低欠陥性、狭粒度分布、低粒内空孔でありかつ均質な粒子形状を有する。

(もっと読む)

コンデンサ

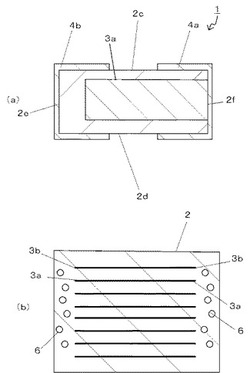

【課題】 層間剥離を抑制できるコンデンサを提供すること。

【解決手段】 複数の誘電体層5が積層された積層体2と、誘電体層5を介して対向するように誘電体層5間に設けられた第1内部電極3aおよび第2内部電極3bと、第1内部電極3aおよび第2内部電極3bにそれぞれ電気的に接続される第1外部電極4aおよび第2外部電極4bとを備え、第1外部電極4aおよび第2外部電極4bの配列方向に垂直な断面において、第1内部電極3aおよび第2内部電極3bと、積層体2の側面との間は、空孔6が多くなっていることから、誘電体層5における積層方向に垂直な方向の残留応力が低減される。従って、コンデンサ1が外部から衝撃を受けた場合であっても、誘電体層5と内部電極3との間の層間剥離の発生を抑制することができる。

(もっと読む)

誘電体セラミックスラリーおよび積層セラミック電子部品

【課題】セラミックスラリー中における、各種セラミック成分の分散性を向上させることができる誘電体セラミックスラリーを提供する。

【解決手段】ステップS1で、主成分であるBaTiO3粉末、第1副成分としてのSiO2ゾル、第2副成分としてのBaCO3粉末とMgCO3粉末などが準備される。ステップS2で、第2副成分のBaCO3粉末とMgCO3粉末などが混合され、解砕される。ステップS3で、混合して解砕した第2副成分粉末が、主成分のBaTiO3粉末と第1副成分のSiO2ゾルとに混合される。ステップS4で、主成分のBaTiO3粉末と第1副成分のSiO2ゾルと第2副成分とに、第1高分子からなるバインダおよび有機溶媒が添加されて湿式混合され、中間スラリーとされる。ステップS5で、中間スラリーに、第2高分子からなるバインダおよび有機溶媒が添加されて湿式混合される。第1高分子の分子量は、第2高分子の分子量より小さい。

(もっと読む)

積層コンデンサ

【課題】 めっき液の浸入を抑制しつつ、製品間における静電容量のばらつきの低減が図られた積層コンデンサを提供する。

【解決手段】

本発明に係る積層コンデンサ100は、内部電極層7が第1の内部電極20と第2の内部電極30とを含み、かつ、各内部電極20、30が、端面から遠い側に位置する同幅の活性電極部21、31と、活性電極部21、31より幅狭であり、端面に近い側に位置する同幅の引出電極部22、32とを含む。中間内部電極層8は第3の内部電極40を含み、かつ、第3の内部電極40は、第1の内部電極20の引出電極部22の一部22aおよび第2の内部電極30の引出電極部32の一部32aと重畳するようにX方向に延在し、かつ、各内部電極20、30の活性電極部21、31の幅w1よりも幅広の形状を有する。

(もっと読む)

電子部品

【課題】実装時に回路基板に対して傾くことを抑制できる電子部品を提供することである。

【解決手段】積層体12は、複数の絶縁体層が積層されて構成され、かつ、窪みG1,G2が形成された下面S6を有している。下面S6は、絶縁体層の外縁が連なることにより構成されている。コンデンサ電極18a,18bは、積層体12に内蔵されている内部導体であって、下面S6の窪みG1,G2において、絶縁体層間から露出している露出部26a,26bを有している。外部電極14a,14bは、直接めっきにより形成され、窪みG1,G2に設けられることにより、露出部26a,26bを覆っている。

(もっと読む)

積層セラミック電子部品およびその製造方法

【課題】内部電極の隣り合う露出端の間隔が広くても、複数の内部電極の露出端間を接続するように連続した、外部電極の少なくとも一部としてのめっき膜を形成することを可能にする。

【解決手段】複数のセラミック層95および複数の内部電極91〜93を備え、複数の内部電極の各一部が露出している、部品本体2として、複数の内部電極の隣り合う露出端間に位置するセラミック層95の端面に、内部電極に含まれる導電成分が拡散して形成された導電領域96〜98が存在しているものが作製される。セラミック層は、ガラス成分を10重量%以上含むガラスセラミックからなることが好ましい。外部電極3〜6を形成するため、内部電極の露出端および上記導電領域をめっき析出の核としてめっき成長させることによって、めっき膜を部品本体2上に直接形成する。

(もっと読む)

積層コンデンサ

【課題】ESLを高めることが可能な積層コンデンサを提供すること。

【解決手段】積層コンデンサ1は、素体1と、それぞれ複数の第一及び第二内部電極13,15と、第一及び第二端子電極3,5と、第一接続導体7と、第一貫通導体17と、を備えている。第一接続導体7には、複数の第一内部電極13が接続されている。第一貫通導体17は、複数の絶縁体層11の積層方向に沿って延びるように素体2内に配置され、一端が実装面に対向する主面2aに配置された第一電極部分3aに接続され且つ他端が第一端子電極3に接続されていない。複数の第一内部電極13は、第一貫通導体17が少なくとも一つの第一内部電極13と接続されることにより、第一貫通導体17及び第一接続導体7を通して第一端子電極3と電気的に接続されている。複数の第二内部電極15は、第二端子電極5と電気的に接続されている。

(もっと読む)

積層セラミックコンデンサ及び積層セラミックコンデンサの製造方法

【課題】内部電極層が位置ずれして積層されても、所定の静電容量を確保できる、寸法安定性に優れた積層セラミックコンデンサ及び積層セラミックコンデンサの製造方法を提供する。

【解決手段】この積層セラミックコンデンサは、静電容量形成部及び引出部を有する第1の内部電極層23及び第2の内部電極層23が、セラミック誘電体層21を介して交互に積層されたセラミック積層体20と、その両端面に形成された外部電極とを備え、第1の内部電極層23の静電容量形成部23aの幅は、第2の内部電極層25の静電容量形成部25aの幅よりも広く形成され、第1の内部電極層23の引出部23bは、その静電容量形成部23aよりも幅狭で、かつ、第2の内部電極層25の引出部25bの幅と等しくなるように形成されている。

(もっと読む)

積層セラミックキャパシタ及びその製造方法

【課題】本発明は積層セラミックキャパシタ及びその製造方法に関する。

【解決手段】本発明の一実施形態による積層セラミックキャパシタは、対向する第1側面及び第2側面、上記第1側面及び第2側面を連結する第3側面及び第4側面を有するセラミック本体と、上記セラミック本体の内部に形成され、上記第3側面または第4側面に一端が露出する複数個の内部電極と、上記第3側面または第4側面に形成され、上記内部電極と電気的に連結される外部電極とを含み、上記複数個の内部電極のうち最外郭に配置される内部電極の末端から上記第1側面または第2側面までの最短距離は中央部に配置される内部電極の末端から上記第1側面または第2側面までの最短距離より小さいか、同一に形成されることができる。

(もっと読む)

積層コンデンサ

【課題】ESLを高めることが可能な積層コンデンサを提供すること。

【解決手段】第一貫通導体17は、複数の絶縁体層11の積層方向に沿って延びるように素体2内に配置され、一端が第一端子電極3の第二電極部分3bに接続され且つ他端が素体2内に位置している。第二貫通導体19は、上記積層方向に沿って延びるように素体2内に配置され、一端が第二端子電極5の第二電極部分5bに接続され且つ他端が素体内2に位置している。第一内部電極13は、第一接続導体7のみに接続されている。第二内部電極15は、第二接続導体9のみに接続されている。第三内部電極14は、第一接続導体7及び第一貫通導体17に接続されている。第四内部電極16は、第二接続導体9及び第二貫通導体17に接続されている。第三及び第四内部電極14,16は、第一及び第二内部電極13,15よりも第一主面2a側に位置している。

(もっと読む)

積層セラミックキャパシタ及びその製造方法

【課題】機械的強度及び信頼性に優れた積層セラミックキャパシタ及びその製造方法を提供する。

【解決手段】積層セラミックキャパシタは、対向する第1の側面及び第2の側面と当該第1の側面及び第2の側面を連結する第3の側面3及び第4の側面4とを有する積層本体と、当該積層本体の内部に形成され上記第3の側面又は第4の側面から所定の間隔をおいて形成される内部電極121,122と、上記積層本体の上面及び下面の少なくとも一面に形成され上記第3の側面又は第4の側面と所定の間隔をおいて当該第3の側面又は第4の側面に沿って形成される溝部Vと、上記第3の側面及び第4の側面から上記積層本体の上面又は下面まで伸びて上記溝部を覆うように形成される外部電極131,132とを含むことができる。

(もっと読む)

3端子コンデンサおよびその実装構造

【課題】 従来の3端子コンデンサを非貫通で使用してバイパスコンデンサとしても、ESLの低減が十分でなく、さらなる低ESL化が求められている。

【解決手段】 3端子コンデンサ21には、誘電体22の厚さ方向に貫通する貫通ビア26が、グランド内部電極25に電気接触せず、貫通内部電極23に電気接触して、設けられている。この貫通ビア26は、上下の両端面が、入出力端子24a、24b間の誘電体22の表面に露出している。このため、貫通ビア26を電源プレーン層32に接続すると共に、入出力端子24a、24b間を電源プレーン層32で短絡して非貫通で使用することにより、電源ライン用配線パターン31a、31bとグランドプレーン層33との間には、電源プレーン層32から貫通ビア26を経由して容量を介しグランドプレーン層33に至るリターン経路が新たに形成される。

(もっと読む)

積層セラミックキャパシタ

【課題】本発明は積層セラミックキャパシタに関する。

【解決手段】本発明による積層セラミックキャパシタは、対向する第1側面及び第2側面、第1側面及び第2側面を連結する第3側面及び第4側面を有するセラミック本体と、セラミック本体の内部に形成され、第3側面または第4側面に一端が露出する複数個の内部電極と、第3側面または第4側面に形成され、内部電極と電気的に連結される外部電極と、内部電極と交互に積層され、セラミック粉末からなる誘電体層とを含み、セラミック粉末の粒径が130μm以下であることを特徴とする。これにより、セラミック粉末とチップ誘電率及び誘電体の厚さを調節することで、積層セラミックキャパシタで発生される音響ノイズ(acoustic noise)を減少させることができる効果がある。よって、積層セラミックキャパシタが用いられる電子製品の騷音も減少させることができる。

(もっと読む)

チップ部品およびその製造方法

【課題】大型でも、高性能で高品質で、実装状態で高い信頼性を確保することのできるチップ部品を提供する。

【解決手段】誘電体素子11と、該誘電体素子の内部に設けた内部電極11aと、該内部電極と電気的に接続した外部電極層15とを備え、誘電体素子11と外部電極層15の間に誘電体素子11の全面を覆うガラス層12を有し、外部電極層15は、金属成分を含む下地電極13と、樹脂電極14とからなり、樹脂電極14は、下地電極13を覆い、かつ誘電体素子11にガラス層12を介して接合する。ガラス層12は、結晶化ガラスからなることが好ましい。

(もっと読む)

セラミック電子部品の製造方法及びセラミック電子部品

【課題】直方体状のセラミック素体の端面に引き出された内部電極に電気的に接続されており、めっき膜からなる外部電極を備えるセラミック電子部品を好適に製造し得る方法を提供する。

【解決手段】複数の第1及び第2の内部電極11,12が内部に形成されたセラミック素体30を用意する。第1及び第2の内部電極露出率が102%〜153%となるようにセラミック素体30を加工する加工工程を行う。加工されたセラミック素体10の上にめっき膜を形成するめっき工程を行う。

(もっと読む)

積層型電子部品およびその製造方法

【課題】積層型電子部品に備える積層体の所定の面上であって、複数の内部電極の各端部が露出した箇所に、直接、電解めっきを施すことによって、複数の内部電極の各端部を互いに電気的に接続する外部電極を、良好な品質をもって形成できるようにする。

【解決手段】積層体5として、内部電極3a,3bが露出する端面6において、隣り合う内部電極3a,3bが互いに電気的に絶縁されているとともに、絶縁体層2の厚み方向に測定した、隣り合う内部電極3a,3b間の間隔sが10μm以下であり、かつ端面6に対する内部電極3a,3bの引っ込み長さdが1μm以下であるものを用意する。電解めっき工程において、複数の内部電極3a,3bの端部に析出した電解めっき析出物が相互に接続されるように当該電解めっき析出物を成長させる。

(もっと読む)

積層コンデンサ

【課題】広い周波数帯域においてESRを制御することができる積層コンデンサを提供すること。

【解決手段】積層コンデンサ1は、コンデンサ素体10と、第1の内部電極30に接続される第1の端子電極20と、第2の内部電極31に接続される第2の端子電極21と、第3の内部電極35に接続される第3の端子電極22と、第4の内部電極36に接続される第4の端子電極23とを備えている。コンデンサ素体10はその内部に、第1及び第2の内部電極30,31が誘電体層12bを介して隣接するように積層される第1のコンデンサ部32と、第3及び第4の内部電極35,36が誘電体層12cを介して隣接するように積層される第2のコンデンサ部37とを有し、第1及び第2の端子電極20,21は、第3及び第4の端子電極22,23よりも電気抵抗が高い高抵抗層20b,21bを有している。

(もっと読む)

電子部品及び基板モジュール

【課題】低ESL化を図ることができると共に、回路基板への実装の際にショートが発生することを抑制できる電子部品及び基板モジュールを提供することである。

【解決手段】積層体11は、コンデンサを形成している容量導体18,19及び内部導体32を内蔵している。外部電極12a,12bはそれぞれ、容量導体18,19に引き出し導体20,21を介して接続されている。内部導体32は、容量導体18,19に対向している。外部電極13,14は、引き出し導体22,23を介して容量導体18に接続されている。外部電極15,16は、引き出し導体24,25を介して容量導体19に接続されている。

(もっと読む)

セラミック電子部品、セラミック電子部品の実装構造、およびセラミック電子部品の製造方法

【課題】セラミック素体内部へ水分が浸入しにくく、かつ、外部からの熱的応力や機械的応力を緩和してセラミック素体へのクラックの発生を防止できるセラミック電子部品、セラミック電子部品の実装構造、およびセラミック電子部品の製造方法を提供する。

【解決手段】セラミック電子部品10は、リフロー工法によって、ランド42を有する実装基板40の上にはんだ実装される。ここで、セラミック電子部品10は、外部電極30,32の回り込み部30b、32bにおいて、下地層34の表面に露出したガラス粒子35が、めっき層36を貫通して外部電極30,32の外表面に露出しているが、ガラス粒子35は、はんだ濡れが悪く、リフローの際に、はんだ44内に空隙46が形成される。すなわち、外部電極30,32の外表面にガラス粒子35が露出した部分において、はんだ44内に空隙46が形成されている。

(もっと読む)

積層セラミック電子部品

【課題】耐湿性を向上させ得るとともに、セラミック素体に対する固着力を向上させ得る外部電極を備える、積層セラミックコンデンサのような積層セラミック電子部品を提供する。

【解決手段】セラミック素体2の内部に配置される内部電極3,4は、端面11,12に露出する露出端16,19を有する。内部電極と電気的に接続されるようにして、端面上に配置された外部電極5,6は、露出端16,19を覆うが、側面9,10には回り込まないようにして、端面上に配置された第1の導電部20,21と、第1の導電部を覆いながら、主面7,8および側面に回り込むようにして、端面上に配置された第2の導電部26,27とを含む。外部電極において、第1の導電部に隣接して、突起部22〜25が端面上に配置されることが、第2の導電部の形成時のセラミック素体の姿勢安定のために好ましい。

(もっと読む)

61 - 80 / 726

[ Back to top ]