Fターム[5E070CB17]の内容

通信用コイル・変成器 (13,001) | コイル−プリントコイル(基板に印刷するもの) (2,690) | 接続(例;スルーホール) (312)

Fターム[5E070CB17]に分類される特許

121 - 140 / 312

積層型電子部品の製造方法

【課題】 非磁性体シートの貫通孔内に磁性体ペーストを印刷により充填していたので、磁性体ペーストが非磁性体シートの表面よりも盛り上がって充填される。そのため、非磁性体シートの表面にコイル用導体パターンを印刷する際に、この盛り上がった磁性体によって非磁性体シートの表面に配置された印刷マスクが浮き上がり、コイル用導体パターンに滲みが発生しやすく、非磁性体シートの表面に微細なコイル用導体パターンが形成できなかった。

【解決手段】 所定パターンの貫通孔が形成された第1の材料からなるセラミックグリーンシートと、セラミックグリーンシートの貫通孔に合致する第2の材料からなる絶縁体を用意する。セラミックグリーンシート表面の表面にコイル用導体パターンが形成される。このコイル用導体パターンが形成されたセラミックグリーンシートと絶縁体が交互に積層される。

(もっと読む)

電流・電圧検出用プリント基板および電流・電圧検出器

【課題】 電流検出点と電圧検出点とを近づけることを可能にする電流・電圧検出用プリント基板、電流・電圧検出器を提供する。

【解決手段】 スルーホールとパターン配線によって形成された電流検出用のコイル状の配線10及び電圧検出用の略半リング状の配線30を同一基板上に形成する。両者の間には、複数のスルーホールによって形成された遮蔽部500が設けられる。この遮蔽部500によって、コイル状の配線10及び電圧検出用の略半リング状の配線30を同一基板上に形成しても、コイル状の配線10に対する電界の影響を低減させることができる。これによって、電流検出点と電圧検出点とを略同一点とすることが可能となる。

(もっと読む)

チップ型LC複合素子

【課題】本発明は、導体パターンが収縮してコイル部のインダクタンス値とコンデンサ部の静電容量値がばらつくのを抑制することができ、これにより、特性のばらつきの抑制が図れる信頼性の高いチップ型LC複合素子を提供することを目的とするものである。

【解決手段】本発明のチップ型LC複合素子は、保護部5を、絶縁体層8に導体パターン1a〜1cを埋設した絶縁樹脂層を積層することにより形成し、かつコイル部2とコンデンサ部3および外部電極部6は前記絶縁体層8に埋設された導体パターン1a〜1cを積層することにより形成し、さらに前記絶縁体層8は感光性樹脂を感光させて形成するとともに前記導体パターン1a〜1cはメッキにより析出された銅により形成し、かつ前記導体パターン1a〜1cと前記絶縁体層8は非焼成により形成したものである。

(もっと読む)

印刷回路基板コイル

本願は、リッツ線から形成されるコアを擬態する、多層印刷回路基板(PCB)用コイルに関する。PCBは、複数の交互する導体層と絶縁層とを含み、導体層は協働してコイルを形成するように相互連結される。各導体層は、要求されたコイル形状を追従し、かつ複数の個別の導体セグメントに分割されるトレースを含む。導体セグメントは、層を越えて電気的に接続され、規則的な繰り返しパターンで層の間をうねる複数の電流経路(すなわちフィラメント)を提供する。コイルは、各フィラメントがペア・コイルに近い状態で実質的に同量の時間を費やすように配置される。故に、各フィラメントは、実質的なコイルの自己または相互インダクタンスに等価になる。各導体層は、複数の関連するトレースおよび中間層コネクターを含むことができ、双方は、各フィラメントが、上方向/下方向だけでなく内方向/外方向も規則的な繰り返しパターンでうねるように相互接続される。 (もっと読む)

アイソレータ

【課題】安価なアイソレータを提供すること。

【解決手段】一次側基板33の主面に一次コイル31とこれに電気的に接続された一次側パッド32を設ける。二次側基板43の主面に二次コイル41とこれに電気的に接続された二次側パッド42を設ける。そして、一次コイル31と二次コイル41を、絶縁体51により相互に絶縁され、かつ上下に重なるように積層する。その際、一次側パッド32が二次側基板43および絶縁体51と重ならず、かつ二次側パッド42が一次側基板33および絶縁体51に重ならないようにする。

(もっと読む)

積層型電子部品の製造方法

【課題】フェライト等の基板材料の廃棄量を低減することが可能な積層型電子部品の製造方法を提供する。

【解決手段】セラミックウェハー11及び当該セラミックウェハー11の一方の主面に形成された回路層12を含む1次加工ウェハー10を複数用意し、複数の1次加工ウェハー10を同じ向きで順に貼り合わせてウェハー積層体15を形成する。次に、ウェハー積層体15におけるセラミックウェハー11の部分をスライスすることにより、回路層12を1枚ずつ分離し、これにより回路層12の上下がセラミック層13に挟まれた構造を有する2次加工ウェハー20を作製する。次に、2次加工ウェハー20の上下のフェライト層13を研磨してその厚みを調整する。最後に、2次加工ウェハー20をチップ単位で裁断して積層型電子部品を得る。

(もっと読む)

コモンモードチョークコイル及びその製造方法

【課題】一対の引き出し導体を同じ絶縁層上に形成しつつ、これらの間の耐圧が高められたコモンモードチョークコイルを提供する。

【解決手段】樹脂絶縁層15B上に形成された引き出し導体31,32を備え、樹脂絶縁層15Bには、引き出し導体31に覆われた第1の部分51と、引き出し導体32に覆われた第2の部分52との間の領域において、凹部53が形成されている。凹部53の内部には、上層の樹脂絶縁層15Cが埋め込まれている。これにより、引き出し導体31,32が形成された部分における樹脂絶縁層15Bが平坦ではなくなることから、樹脂絶縁層15Bの表面に沿った引き出し導体31,32間の距離が長くなる。このため、樹脂絶縁層15Bの表面に沿ったイオンの移動などによって生じる電流パスが形成されにくくなることから、引き出し導体31,32間の距離が近い場合であっても高い耐圧を得ることが可能となる。

(もっと読む)

積層型電子部品及び積層型電子部品の周波数特性の調整方法

【課題】通過周波数帯域の特性に影響を与えることなく減衰周波数帯域の特性を変えることを目的とする。

【解決手段】複数の絶縁基板(M1〜M8)が積層されてなる積層型電子部品10であって、外部電極106と、第1の導体パターン121が形成されている第1の絶縁基板M2と、前記外部電極106に接続され、前記第1の導体パターン121と一部が重なり、前記第1の導体パターン121と重ならない部分に切り欠き部を有する第2の導体パターン111が形成されている第2の絶縁基板M1と、前記第1の導体パターン121に接続されるインダクタ導体121tとを備える。

(もっと読む)

積層電子部品

【課題】 積層インダクタや、インダクタを内蔵する多層基板等の積層電子部品において、製造工数を低減しながら、直流抵抗値を低減し、Q値に優れた積層電子部品を得ることを目的とする。

【解決手段】 第1の絶縁体層を介して、第1の導体パターンと第2の導体パターンとを複数のビアホールで並列接続してなるコイルパターンを有する積層電子部品において、第2の導体パターンは略1ターンに形成した導体パターンであり、第1の導体パターンは、第2の導体パターンの両端部と積層方向に重なる導体パターンであって、略3/4ターン〜略1ターンに形成し、複数のコイルパターンを積層し、コイルパターンの第2の導体パターンと、他コイルパターンの第1の導体パターンとを第2の絶縁体層を介してビアホールで直列に接続して螺旋状に形成したコイルとした。

(もっと読む)

インダクタ素子及びその製造方法

【課題】本発明は、半導体基板に形成されたインダクタ素子及びその製造方法に関し、特に携帯情報通信機器や無線LAN(Local Area Network)等に用いられる高周波モジュールや電圧変換モジュールに適用され、小型化できると共に、抵抗損失の増加を抑制することのできるインダクタ素子及びその製造方法を提供することを課題とする。

【解決手段】半導体基板11に形成されたインダクタ素子20であって、半導体基板11を貫通すると共に、スパイラル形状とされ、導電性を有したインダクタ本体61と、インダクタ本体61の側面と半導体基板11との間に設けられた絶縁膜12とを設けた。

(もっと読む)

半導体装置

【課題】従来技術に比較して、漏洩磁束が抑えられた高い変換効率を実現するインダクタを集積化した半導体装置を提供する。

【解決手段】半導体集積回路1aを備えた基板1と、半導体集積回路1aを備えた基板1の上に形成された第1の絶縁層2と、第1の絶縁層2の上に形成された第1の導電層3と、第1の導電層3の上に形成された第2の絶縁層4と、第2の絶縁層4の上に形成された磁性体層5と、磁性体層5の上に形成された第3の絶縁層6と、第3の絶縁層6の上に形成された第2の導電層7とを有する半導体装置であって、第1の導電層3および第2の導電層7は各所定部で電気的に接続されて基板1の主面に平行に閉磁路を形成する巻線を構成し、該巻線と磁性体層5とがトロイダルコイルを形成し、該トロイダルコイルと半導体集積回路1aが電気的に接続されている。

(もっと読む)

コモンモードチョークコイル及びその製造方法

【課題】スパイラル導体間の寄生容量を低減しつつ、引き出し導体間の耐圧が高められたコモンモードチョークコイルを提供する。

【解決手段】積層されたスパイラル導体21,22と、端子電極14c,14dと、スパイラル導体21の内周端と端子電極14cとを接続する引き出し導体31と、スパイラル導体22の内周端と端子電極14dとを接続する引き出し導体32と、スパイラル導体21,22間に設けられた樹脂絶縁層15B〜15Dとを備える。引き出し導体31は樹脂絶縁層15Bと15Cとの間に形成されており、引き出し導体32は樹脂絶縁層15Cと15Dとの間に形成されている。このように、引き出し導体31,32が同一平面上ではなく、異なる平面上に位置することになるため、これらの間の耐圧を高めることが可能となる。

(もっと読む)

積層型トランス

【課題】 各コイルを構成するコイル用導体パターンが積層方向において絶縁体層を介して上下に重なっているので、絶縁体層を介して対向しているコイル用導体パターン間に線間容量が発生する。

【解決手段】 絶縁体層と、絶縁体層上に形成された複数組のコイル用導体パターンとを積層し、絶縁体層間のコイル用導体パターンを各組同士で接続してこれらの積層体内に、共通の巻軸を中心に螺旋状に巻かれた複数個のコイルが形成される。この複数組のコイル用導体パターンは、絶縁体層表面において共通の巻軸を原点に点対称に形成された第1のコイル用導体パターンと第2のコイル用導体パターンからなり、複数組のコイル用導体パターンと絶縁体層が積層された時、第1のコイル用導体パターン、第2のコイル用導体パターンのそれぞれは、絶縁体層の積層方向において、絶縁体層の上下に位置するコイル用導体パターンが互いに対向しない様にその位置をずらして形成される。

(もっと読む)

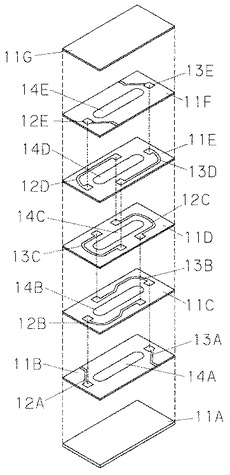

インダクタ内蔵型多層配線基板

【課題】多層配線基板上に形成するインダクタにおいて、コイル配線のライン・スペース等の要因を適正に規制することにより、パターン作成面積を極力小さくし、且つ所望のインダクタンスの値を得、共振周波数の高周波数化に対応可能なインダクタ内蔵型の多層配線基板を提供する。

【解決手段】多層基板の各層について複数回巻きの渦巻き状導体パターン(11〜14)を形成し、渦巻き状導体パターンの一端を上層の渦巻き状導体パターンの他端に層間接続し、渦巻き状導体パターンの他端を下層の導体パターンの一端に層間接続し、全体として螺旋状のコイル(10)を形成するインダクタ内蔵型多層配線基板において、各層における導体パターンのライン間スペース(距離A)と、導体パターン間の層間スペース(距離B)との比率をA>Bとしたことを特徴とする。

(もっと読む)

コモンモードチョークコイルアレイ

【課題】 電気的な特性が異なる複数のラインに適用できると共に、複数のライン間でクロストークの発生を抑制する。

【解決手段】 コモンモードチョークコイルアレイ1は、第1,第2のコモンモードチョークコイル3,17を厚さ方向に積み重ねて形成する。このとき、第1のコモンモードチョークコイル3の第1コイル6,7は、第2のコモンモードチョークコイル17の第2コイル20,21よりも線路の幅寸法T1を大きく形成する。また、積層体2の端面には、第1のコモンモードチョークコイル3の第1外部端子電極32,33,36,37の間に位置して、第2のコモンモードチョークコイル17の第2外部端子電極34,35,38,39を配置する。これにより、外部端子電極32〜39をUSBコネクタの端子の配置に合わせることができる。

(もっと読む)

インダクタ、配線基板、および半導体装置

【課題】 高周波帯域においても寄生抵抗が低く、入出力端子からインダクタを見たときの特性が対称的であり、小型なオンチップ型のインダクタを提供する。

【解決手段】 絶縁層を介した複数の層に亘って入力端子IN1、IN2から出力端子OUT1、OUT2まで螺旋状にそれぞれ延びた偶数個のインダクタ素子L1、L2を有している。インダクタ素子L1、L2は、相互の発生磁界が同じ向きとなるように配置されていると共に、入力端子から見たQ値を含むインダクタ特性と出力端子から見たものとが概ね同じになるように並列接続されている。

(もっと読む)

積層型バンドパスフィルタ

【課題】 集中定数タイプは、小型化に伴って、2つのコイルによってトランス構造を形成することが困難になり、その磁気的結合によって生じる相互インダクタンスも十分なものが得られない。

【解決手段】 絶縁体層と導体パターンを積層して積層体内に、第1コイルと第2コイルが入出力端子間に接続され、第1コイルと第2コイルの直列回路と並列に第1コンデンサが接続され、第1コイルの入力端子側とアース間に第2コンデンサが接続され、第1コイルと第2コイルの接続点とアース間に第3コイルが接続され、第2コイルの出力端子側とアース間に第3コンデンサが接続されたバンドパスフィルタが形成される。第1コイルと第2コイルは、第1コイル用導体パターンの一端と第2のコイル用導体パターンの一端を互いに接続し、第1のコイルと第2のコイルを構成するコイル用導体パターンの中間点とアース端子間に線状の導体パターンが形成されて第3コイルが形成される。

(もっと読む)

電子部品

【課題】サイズを変更することなく容量値を変化させることにより、共振周波数を幅広い範囲で設定できる電子部品を提供する。

【解決手段】積層体部分3は、複数の絶縁層38a,38b,38c,38dが積層されて構成される。複数の内部電極31a,31b,31c,31dは、複数の絶縁層38a,38b,38c,38dと共に積層される。複数の内部電極31a,31b,31c,31dは、積層順とは異なる順番で電気的に接続されて、コイルLを構成している。

(もっと読む)

電子部品およびその製造方法

【課題】導体膜と絶縁膜を積層した電子部品のビア部分の耐性を高め、信頼性を向上させる。

【解決手段】第一導体と、この表面を覆う絶縁体と、絶縁体を貫通するビアと、絶縁体の表面に配されビアを通じて第一導体と接続される第二導体とを備えた電子部品で、導電性を有しかつ第一導体と第二導体との間に介在されかつ少なくともビアの底面となる第一導体表面とビア内壁面とに亘って連続して延在してビア内において第一導体と絶縁体の界面を覆う導電性シールド膜を備えた。ビア内に充填されるように導体を配し、この導体表面とビア周囲の絶縁体表面とを覆う導電性シールド膜を設けても良い。シールド膜は、脱脂液を含む表面活性処理液、酸性薬液、アルカリ性薬液、溶剤、アルコール、めっき液及びエッチング液に対する耐性を有し、耐湿性、耐ガス透過性、耐腐食性を有する場合があり、例えばCr、Ni、Ti、Cu、W、Ag又はAlを主成分とする。

(もっと読む)

コモンモードチョークコイル

【課題】 1次コイルと2次コイルとの間でインダクタンス値の差を小さくすることができるコモンモードチョークコイルを提供する。

【解決手段】 コモンモードチョークコイル1は、第1,第2の磁性体基板2,3の間に積層体4を設けて構成する。また、積層体4は、第1の絶縁層5、1次コイル9、コイル間絶縁層10、2次コイル14、第2の絶縁層15等を積み重ねることによって形成する。そして、各コイル9,14は、入力側の外部電極8D,11Dの中点と出力側の外部電極6A,13Aの中点とを結ぶ対称線を軸として180°回転対称な構成とする。

(もっと読む)

121 - 140 / 312

[ Back to top ]