Fターム[5E070CB17]の内容

通信用コイル・変成器 (13,001) | コイル−プリントコイル(基板に印刷するもの) (2,690) | 接続(例;スルーホール) (312)

Fターム[5E070CB17]に分類される特許

41 - 60 / 312

高周波トランス、電子回路および電子機器

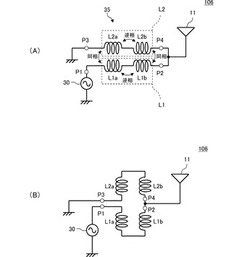

【課題】製造が容易で小型化しやすい、低損失でエネルギーを伝送できる高結合度トランスを構成する。

【解決手段】高結合度トランス35はアンテナ素子11と給電回路30との間に接続される。高結合度トランス35は、給電回路30に接続された第1インダクタンス素子L1と、第1インダクタンス素子L1に結合した第2インダクタンス素子L2とを備え、第1インダクタンス素子L1の第1端は給電回路30に、第2端はアンテナ素子11にそれぞれ接続されていて、第2インダクタンス素子L2の第1端はアンテナ素子11に、第2端はグランドにそれぞれ接続される。

(もっと読む)

フェライト積層電子部品の製造方法

【課題】内部導体の周囲のフェライトに残留する応力を低減して、良好な特性を備えたフェライト積層電子部品を効率よく製造することが可能なフェライト積層電子部品の製造方法を提供する。

【解決手段】Fe2O3粉末およびNiO粉末と、有機バインダーとを含む配合物を用いてグリーンシートを作製し、このグリーンシートを用いて、未焼成の内部導体を内蔵するグリーンシート積層体を形成した後、所定の条件で熱処理して、グリーンシート積層体の脱脂を行い、得られる脱脂後積層体を焼成することによりフェライト積層電子部品を製造するにあたって、Fe2O3粉末として、平均粒径が0.1〜0.5μm、比表面積が10m2/g以上のFe2O3粉末を用いる。

脱脂後積層体中の残留カーボン量が、重量基準で550〜1000ppmとなるような条件で脱脂を行う。

上記グリーンシートの作製に用いられる配合物として、仮焼工程を経ていない配合物を用いる。

(もっと読む)

電子部品

【課題】はんだ付け実装する際のセルフアライメント性の向上が図られた電子部品を提供する。

【解決手段】積層チップインダクタは、直方体形状の外形を有し、対向する両端面それぞれに、角部Cを挟んで隣り合う端面の一部と底面1cの一部とを連続的に覆う断面L字状の外部電極が設けられた積層チップインダクタであって、端面には、四角形状の外部電極の端面部2bと、角部Cの稜線方向(X方向)において外部電極の端面部2bを挟む位置に等幅の一対のギャップ部gとが設けられており、角部Cの稜線方向における端面の幅Wとギャップ部gの幅dとの比d/Wが0<d/W≦0.2である。

(もっと読む)

積層型コイル

【課題】 コイルパターンの径を大きくし、かつ積層体の外周面に絶縁膜を形成した積層型コイルにおいて、絶縁性をより確実にする。

【解決手段】 積層型コイル100は、矩形状の絶縁層1と、コイルパターン2とが、それぞれ複数、交互に積層され、一体化されてなる積層体3と、スルーホール4aと、コイルパターン2が、スルーホール4aを介して相互に接続されて、積層体3の内部に形成されたコイル5と、外部電極6a、6bと、積層体3の外周面に形成された絶縁膜7とを備え、スルーホール4aの少なくとも1つが、積層体3の表面に部分的に露出しているが、そのスルーホール4aは、絶縁層1の外周縁のうちの1辺に接しているが、その1辺以外の他の辺には接しないように形成した。

(もっと読む)

インダクタを含む積層型電子部品

【課題】スルーホール等の貫通接続導体を用いずに積層体内部に複数層に亘ってインダクタを形成することにより製造工程の簡略化と電気特性の向上を図る。

【解決手段】第一積層体と、表面配線層を備えかつ第一積層体に接合した第二積層体とを含む積層型電子部品で、第一積層体と第二積層体の配線層は互いに直交し、第一積層体は、第一配線層に配した第一インダクタ用導体と、第二配線層に配した第二インダクタ用導体とを有し、第二積層体は、第一インダクタ用導体と第二インダクタ用導体がコイル状のインダクタを形成するように第一積層体との接合面において第一インダクタ用導体の端部と第二インダクタ用導体の端部を電気的に接続する接続導体を有する。

(もっと読む)

コイル内蔵配線基板

【課題】 焼成時にフェライト層2の透磁率が低減することを抑制できるコイル内蔵配線基板を提供すること。

【解決手段】 複数のフェライト層2と、フェライト層2の表面および内部に形成された配線導体3と、複数のフェライト層2の層間および内部に、配線導体3と電気的に接続されたコイル導体4とを備えたコイル内蔵配線基板であって、コイル導体4は、コイル導体4の幅方向の断面の断面視で、フェライト層2の一部を囲むように形成されていることを特徴とするコイル内蔵配線基板である。コイル導体4の外周部のフェライト層2への応力を低減できるので、フェライト層2の透磁率の低下を低減できる。また、フェライト層2や絶縁層1のクラックやデラミネーションの発生を抑制できる。

(もっと読む)

フィルタ回路及び電子部品

【課題】コモンモードの信号に対する周波数特性の広帯域化を図ることができるとともに、有効なノーマルモードの信号が除去されることを低減できるフィルタ回路及び電子部品を提供することである。

【解決手段】グランド経路G1,G2はそれぞれ、外部電極14e(グランド)と信号経路Sig1,Sig2のそれぞれとを接続している。信号経路Sig1は、コイルL1を含んでいる。信号経路Sig2は、コイルL1とコモンモードチョークコイルL101を構成しているコイルL2を含んでいる。グランド経路G1は、コイルL3及びコイルL3に直列接続されているコンデンサC1を含んでいる。グランド経路G2は、コイルL3とコモンモードチョークコイルL102を構成しているコイルL4及びコイルL4に直列接続されているコンデンサC2を含んでいる。

(もっと読む)

コイル装置の製造方法

【課題】 高周波回路等に使用されるコイル装置製造方法に関して、L値を悪化させることなく、高周波性能の向上が可能なコイル装置の製造方法を提供する。

【解決手段】 第1絶縁層を形成する第1工程と、前記第1絶縁層上に、第1導電配線パターンを形成する第2工程と、前記第1導電配線パターン上に、パッドとして機能する第2導電配線パターンを形成する第3工程と、前記第1、第2導電配線パターンを含む第1絶縁層上に、感光性材料からなる第2絶縁層を形成する第4工程と、前記第2絶縁層における前記パッドと対応する位置に、ビアホールをフォトリソグラフィにより形成する第5工程と、前記第2絶縁層上に、第3導電配線パターンを形成するとともに、ビアホールの内部に導電材を充填してビアを形成する第6工程を実行する。これらの工程で形成した積層体を基材から剥離し、カット、脱脂、焼成を経て、外部電極を形成しチップ型コイル装置を得る。

(もっと読む)

薄型コモンモードフィルタおよびその製造方法

【課題】 コモンモードフィルタおよび製造方法において、素子の厚さを効果的に削減することにより、公知のコモンモードフィルタにある欠点を克服するとともに、製造コストを削減する。

【解決手段】 薄型コモンモードフィルタ10は、絶縁性の可撓性シート11と、第1の磁性材料層121と、第1のコイルリード層13と、コイル本体積層構造14と、第2のコイルリード層15と、第2の磁性材料層171とを備える。第1のコイルリード層13は、可撓性シート11の第1の面111上に形成されており、また第1の磁性材料層121は可撓性シート11における第1の面111の反対にある第2の面112上に形成されている。またコイル本体積層構造14、第2のコイルリード層15および第2の磁性材料層171は第1のコイルリード層13上に順次積層されている。

(もっと読む)

コイル部品

【課題】小型化を図りつつ、磁気結合を高めることができるコイル部品を提供する。

【解決手段】コモンモードフィルタ1では、基板10〜17を積層することにより第1コイル61及び第2コイル62が構成され、第1コイル61及び第2コイル62は、基板13と基板15との間に配置される第1接続部14a,14b及び第2接続部14cによって形成される空間Sに挿入されたコア71,72にバイファイラ巻きされている。これにより、コイル数を増やす場合には、基板において第1〜第4導体31〜34を長手方向に増加させればよいので、従来のように基板の積層数を増やす必要がない。そのため、基体2の寸法の増大を抑制することができる。また、第1コイル61及び第2コイル62は、コア71,72にバイファイラ巻きされているので、磁気結合を高めることができる。

(もっと読む)

チップ型コイル部品

【課題】コイルのインダクタンス値を極力低下させることなく、コイルの抵抗値を低減できるチップ型コイル部品を提供する。

【解決手段】磁性体層20は、積層体を構成している。内部電極26は、磁性体層20上に積層されると共に、それぞれが接続されることによりコイルLを形成しており、z軸方向から平面視したときに、互いに重なりあって、長方形状の軌道を形成している。補助内部電極30は、内部電極26が積層されている磁性体層20上に積層されている。補助内部電極30は、補助内部電極30が積層されている磁性体層20とは異なる磁性体層20上に積層されている内部電極26に対して並列接続されている。補助内部電極30は、長方形状の軌道の2つの辺以上に跨っている。

(もっと読む)

積層型電子部品

【課題】 DC−DCコンバータのICから出力される信号は、高電流、かつ高速の三角波が重畳されており、そのエネルギーの変化速度も数百MHzになるといわれ、このエネルギーによるノイズも発生し易くなっている。DC−DCコンバータのICに接続されるコイルやコンデンサを電子機器の配線基板上で接続した場合、配線基板の配線パターンによって、コイルとコンデンサの接続点に、それぞれ寄生インダクタンスが発生し、DC−DCコンバータの効率が悪化すると共に、ノイズが発生し易くなる。

【解決手段】 絶縁体層と導体パターンを積層し、絶縁体層間の導体パターンを螺旋状に接続してコイルが形成されたコイル部と、絶縁体層と導体パターンを積層してインピーダンス素子が形成されたインピーダンス部とが積層される。これらの積層体内には、入力端子と出力端子間に外部端子を介して直列に接続されたコイルとインピーダンス素子が形成される。

(もっと読む)

積層型インダクタ、及び積層型インダクタの製造方法

【課題】導体パターン同士の間の絶縁体層にクラックが生じることを防止し、信頼性を向上させることのできる積層型インダクタを提供する。

【解決手段】第一部分26の端面31の幅方向における連結端41A,41Bは、積層方向から見て第二部分27の側面27A,27Bと重なっていない。連結端41A,41Bが、応力集中領域WA,WB以外の位置に配置されている。すなわち、磁性体層A3〜A10または非磁性体層B1,B2と側面27A,27Bとの間には、応力が集中し易い第一部分26の連結端41A,41Bに代えて、積層体12の磁性体膜F1〜F10が配置される。従って、第二部分27の側面27A,27Bからの応力は、磁性体膜F1〜F10によって緩和される。

(もっと読む)

回路基板装置

【課題】電磁界の発生を抑制し、一方で小型化の要求に即した回路基板装置を提案する。

【解決手段】本発明の回路基板装置100において、第1配線層110は、第1インダクタ12と第2インダクタ14とを有する。誘電体層115は、第1インダクタ12および第2インダクタ14のそれぞれに電気的に接続する第1ビア70および第2ビア72を有する。第2配線層120は、第1ビア70および第2ビア72を電気的に接続するブリッジ線路30と、ブリッジ線路30の周囲に設けられて、第1配線層110における第1配線パターンおよび第2配線パターンの外縁を越えた位置に外縁をもつ導体パターン50とを有する。ブリッジ線路30は、コプレナー線路として機能し、電磁界の発生を抑制する。

(もっと読む)

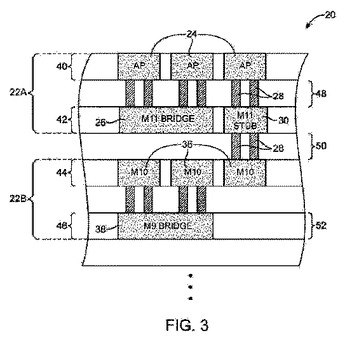

直列接続のインダクターを有する集積回路

集積回路インダクターは、直列に接続されている上部ループ形状のライン部分と下部ループ形状のライン部分とを有し得る。上部部分および下部部分は、45°曲がりを有し得、6角形または8角形のループを形成する。各ループ部分は、1つ以上のターンを有し得る。金属ルーティング層の介在する金属フリー領域が、容量性カップリングを低減させるために、2つの層の間に形成され得る。各ループ部分は、ビアによって並列にショートされた2つ以上の金属ラインのセットを有し得る。上部ループおよび下部ループは、容量性カップリングを低減させるために、横にオフセットされ、または入れ子にされ得る。  (もっと読む)

(もっと読む)

半導体装置

【課題】 2巻きの渦巻き状であって1箇所において立体的に交差する薄膜インダクタ素子を備え、該薄膜インダクタ素子の両端部側から見たときの特性がほぼ均等となるようにする。

【解決手段】 薄膜インダクタ素子13は、絶縁膜上に1箇所が欠けた環状に設けられた外側上層配線14と、絶縁膜上において外側上層配線14の内側に同一側の1箇所が欠けた環状に設けられた内側上層配線15と、絶縁膜下に外側上層配線14の一端部及び内側上層配線15の一端部に接続されて設けられた下層配線16とを有する。この場合、外側上層配線14の長さと内側上層配線15の長さは同じかほぼ同一で、その差が小さいので、薄膜インダクタ素子13の両端部側から見たときの特性をほぼ均等とすることができる。

(もっと読む)

デジタルCMOS工程において周波数合成器に用いられるソレノイドインダクタ

本発明のデジタルCMOS工程で周波数合成器に用いられるソレノイドインダクタは、所定の幅を有し、両側が垂直方向に積層され、ソレノイド構造を有する多数の配線金属と、両側に積層された多数の配線金属の相互間を連結する配線金属連結部とを備え、両側に積層された多数の配線金属のうち、所定数の下位層配線金属と、下位層配線金属の相互間を連結する配線金属連結部とがそれぞれ連結され重なる。本発明によると、デジタルCMOS工程で4〜5GHz以上の周波数帯域で動作する周波数合成器を具現するためにソレノイドインダクタを用いることで、RF CMOS工程でのみ具現可能な数GHz帯域の周波数合成器を具現することができる効果がある。  (もっと読む)

(もっと読む)

スパイラルコイルの配線構造および集積回路装置

【課題】 第1インダクターおよび第2インダクターを有する3ポートのスパイラルコイルにおける特性の対称性を確保し、かつ、3つのポートを、スパイラルコイルの中心を通る直線を基準として同じ側に配置すること。

【解決手段】 第1ポートと第3ポートとの間に設けられる第1インダクターと、第2ポートと前記第3ポートとの間に設けられる第2インダクターとを含むスパイラルコイルの配線構造であって、スパイラルコイルの中心を通る直線を基準として、前記第1ポートおよび第2ポートは同じ側に配置され、第1ポートから引き出される第1配線と、第2ポートから引き出される第2配線とが、スパイラルコイルの中心を通る直線を基準として、第1ポートおよび第2ポートの側において交差することによって第1交差部が設けられる。

(もっと読む)

変圧器電力合成器

【課題】複数の入力ポートと少なくとも1つの出力ポートとを備え、高い変圧器結合効率及び高い電力合成効率を達成するオンチップ変圧器電力合成器を提供する。

【解決手段】変圧器電力合成器は、複数の一次巻線導体と複数の二次巻線導体とを含む。一次巻線導体は、入力ポートにそれぞれ電気的に接続される。加えて、各一次巻線導体は対応する入力ポートのプラス端子とマイナス端子との間に電気的に接続されている。二次巻線導体は、一次巻線導体にそれぞれ磁気的に結合される。二次巻線導体は、出力ポートのプラス端子とマイナス端子との間に直列接続及び並列接続を含むトポロジー構造を持つように構成される。

(もっと読む)

インダクタ及びインダクタの製造方法

【課題】 コイル構造体を小型化でき、インダクタンスを容易に変更することのできるインダクタを提供することを課題とする。

【解決手段】 各々が絶縁材で包囲されて互いに絶縁され、表面と裏面との間を貫通して延在する多数の微細な柱状導電体2を含むコア基板4を準備する。コア基板4の表面と裏面に絶縁層6,8を形成する。絶縁層6,8を貫通する少なくとも2つの接続導電体6a,8aを形成する。接続導電体6a,8a同士を電気的に接続する配線10,12を絶縁層6,8上に形成する。配線10,12と、接続導電体6a,8aと、柱状導電体2とが接続されて立体的にコイルが形成される。

(もっと読む)

41 - 60 / 312

[ Back to top ]