Fターム[5E082BC33]の内容

固定コンデンサ及びコンデンサ製造装置 (37,594) | 目的、効果 (2,673) | 機械的強度 (420) | 応力(熱膨張など)の緩和 (176)

Fターム[5E082BC33]に分類される特許

1 - 20 / 176

積層セラミックコンデンサ及びその製造方法

電子部品

【課題】積層体に大きなクラックが発生することを抑制できる電子部品を提供することである。

【解決手段】積層体11は、複数のセラミック層が積層されてなり、上面S1及び底面S2、並びに、互いに対向している2つの端面S3,S4を有している。コンデンサ導体層30,31は、セラミック層上に設けられており、コンデンサを構成している。外部電極12a,12bは、端面S3,S4を覆っていると共に、上面S1及び底面S2に折り返されている。ダミー導体層40,41は、コンデンサ導体30,31が設けられているセラミック層よりも底面S2の近くに位置しているセラミック層上に設けられており、z軸方向から平面視したときに、外部電極12a,12bにおける底面S2に折り返されている部分の先端Tb,Tdと重なっている。ダミー導体層40,41の厚みは、コンデンサ導体層30,31の厚みよりも大きい。

(もっと読む)

チップ型電子部品及びチップ型電子部品の実装構造

【課題】端子電極における内部応力の低減と、はんだ食われの防止及び接触抵抗の低減とを両立できるチップ型電子部品及びこれを用いた実装構造を提供する。

【解決手段】積層コンデンサ1において端子電極3は、CuコートされたNi粉を含有する第1の樹脂電極層3aが、最外層であるSnめっき層3bの内側に隣接している。この第1の樹脂電極層3aに含まれるNi粉はCuによってコートされている。第1の樹脂電極層はCu粉を含有しても良い。最外層はSnコートされたNi粉を含有する第2の樹脂電極層としても良い。そして、端子電極はNiめっき層を有していない。

(もっと読む)

チップ型電子部品及びチップ型電子部品の製造方法

【課題】チップ型電子部品が外部から受ける応力を緩和して、チップ型電子部品に発生するクラックを抑制すること。

【解決手段】チップ型電子部品10は、誘電体を含むセラミック素体11と、セラミック素体11の内部に配置され、かつ、セラミック素体11の表面に一部が露出する内部電極17、18と、セラミック素体11の表面に配置された端子電極20、30と、を含む。端子電極20、30は、第1の導電性材料と第1の樹脂とを含み、かつセラミック素体11の内部電極17、18が露出する端面13、14に配置される第1の樹脂層21、31と、第2の樹脂を含むとともに、第1の樹脂層21、31の少なくとも一部と接触し、かつ第1の樹脂層21、31よりもヤング率が低い第2の樹脂層22、32と、を含む。

(もっと読む)

コンデンサおよびその製造方法

【課題】折り曲げ加工されるリード端子の曲げ応力の緩和とともに、リード端子とコンデンサ素子側との接続強度の劣化防止を図る。

【解決手段】 コンデンサ素子(4)を封止する外装部材(6)と、前記コンデンサ素子に接続されかつ前記外装部材または該外装部材に併置されたベース部材(30)から引き出され、折り曲げ加工されたリード端子(10A、10B)とを備え、前記リード端子は、偏平部(23)と、該偏平部の折り曲げ方向の面部に形成された第1の凹部(ノッチ24)と、前記折り曲げ方向と反対方向の面部に形成された第2の凹部(ノッチ26)とを備え、これら第1の凹部と第2の凹部とが前記外装部材の端子引出し面部(18)から異なった位置に設定され、第1の凹部を支点(起点)にしてリード端子(10A、10B)が折り曲げられる。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】本発明は、電極連結性を制御して容量を確保することができる積層セラミック電子部品及びその製造方法を提供する。

【解決手段】本発明による積層セラミック電子部品は、セラミック本体10と、この前記セラミック本体10の内部に形成され、中央部70及び前記この中央部70から縁に向かって薄くなるテーパ部50を有する内部電極30、31と、を含む。前記内部電極30、31の面積に対する前記テーパ部50の面積の比率は、35%以下であることを特徴とする。本発明によると、小型及び高容量の積層型セラミックキャパシタにおいても、電極連結性を制御することにより所望の容量を確保することができる。

(もっと読む)

電子部品及びその製造方法

【課題】拘束層材料と素子層材料の電子特性との相対的な関係を選択することにより、側電極の深さを全体的な電気の影響を最小限に抑える。

【解決手段】電子部品およびその製造方法は、まず、第二電子特性を有する拘束層を第一電子特性を有する素子層に形成する。前記電子部品の特性は、前記第一電子特性によって主に影響される。その後、両方の拘束層及び素子層を焼結温度で焼結する。第一電子特性と第二電子特性との関係を選択することにより、電子部品の特性が安定になる。

(もっと読む)

電子部品

【課題】中間層部の緻密化を図り、信頼性の高い電子部品を提供すること。

【解決手段】セラミックコンデンサ101は、複数のセラミック誘電体層105及び複数の内部電極層141,142を積層してなる電極積層部107と、電極積層部107の外面を覆うように設けられたカバー層部108と、電極積層部107の積層途中となる位置に設けられた中間層部109と、電極積層部107の積層方向に延びて複数の内部電極層141,142に接続された複数のコンデンサ内ビア導体131,132とを備える。中間層部109は、自身の厚さの1/10以下の粒径を持つ金属粒子154がセラミック粒子に対して1体積%以上30体積%以下の割合で混合された材料により形成されている。

(もっと読む)

積層コンデンサ及び積層コンデンサの製造方法

【課題】焼付層の応力によるクラックの発生と、めっき液の浸入による絶縁不良の発生とを防止できる積層コンデンサ及び積層コンデンサの製造方法を提供する。

【解決手段】積層コンデンサ1では、内部電極6A,6Bから積層体2の端面に引き出される引出導体12A,12Bの全部を覆うように焼付層17A,17Bが形成されている。これにより、めっき層18A,18Bの形成の際にめっき液が内部電極6A,6B側に浸入することが防止され、絶縁不良の発生を防止できる。また、焼付層17A,17Bがダミー電極13C,13F,13G,13Hの一部を覆っているので、焼付層17A,17Bの面積を抑えることができる。したがって、焼付層17A,17Bに過剰な応力が生じることを抑制でき、焼付層17A,17Bの応力によるクラックの発生を防止できる。

(もっと読む)

チップ状電子部品

【課題】 信頼性の低下を抑制し且つ小型化に適したチップ状電子部品を提供する。

【解決手段】内部電極11が埋設されたセラミックからなる部品本体10と該部品本体10の外面に形成された外部電極20とを備えたチップ状電子部品1において、前記外部電極20は、部品本体の外面に形成された第1の電極層21と、第1の電極層21の外面に物理的蒸着法又は化学的蒸着法で形成されてなり且つ部品本体10内への水素の拡散を防止する保護層22と、保護層22の外面に電解メッキで形成された1層以上の第2の電極層23,24とを備えたことを特徴とする。

(もっと読む)

積層セラミックコンデンサ

【課題】強度および耐湿性が向上し、熱衝撃によるクラックの発生を効果的に防止することができる積層セラミックコンデンサを提供する。

【解決手段】積層セラミックコンデンサは、セラミック誘電体層2と内部電極3とが交互に積み重ねられた積層体ブロック4と、積層体ブロック4の上下に積み重ねられた一対のカバー層5と、積層体ブロック4の両側面に形成されたセラミック体6と、内部電極3と電気的に接続する一対の外部電極とを有し、セラミック体6を構成するセラミック誘電体粒子の平均粒子径が、積層体ブロック4に含まれるセラミック誘電体層2を構成するセラミック誘電体粒子の平均粒子径よりも小さくなるように構成されている。

(もっと読む)

積層コンデンサの実装構造

【課題】積層コンデンサの電歪現象に起因して発生する音鳴きを抑制すること。

【解決手段】積層コンデンサ10は、回路基板2の基板面2Pと直交する方向に第1内部電極と第2内部電極とが誘電体層を介して積層される素体11と、第1内部電極と第2内部電極とが積層される方向と直交する方向に存在する素体11の第1側面11Aで第1内部電極と接続される第1側面側第1端子電極21Aと、第1側面11Aで第2内部電極と接続される第1側面側第2端子電極22Aと、を含む。積層コンデンサ10は、第1側面11A側で回路基板2に取り付けられ、第1側面11Aと対向する第2側面11B側は回路基板2に取り付けられない。

(もっと読む)

積層セラミックコンデンサ

【課題】積層体においてクラック等の内部破壊が生じにくく大容量且つ小型化に適した積層セラミックコンデンサを提供する。

【解決手段】複数の誘電体層120と複数の内部電極層110とを交互に積層した積層体10と該積層体10の外面に形成され前記内部電極層110に電気的に接続した外部電極20とを備えた積層セラミックコンデンサ1において、積層体10の外層側部分における隣り合う内部電極層111,112間に形成される電界強度が積層体10の中央部分における隣り合う内部電極層110間に形成される電界強度よりも小さいことを特徴とする。

(もっと読む)

コンデンサ

【課題】 層間剥離を抑制できるコンデンサを提供すること。

【解決手段】 複数の誘電体層5が積層された積層体2と、誘電体層5を介して対向するように誘電体層5間に設けられた第1内部電極3aおよび第2内部電極3bと、第1内部電極3aおよび第2内部電極3bにそれぞれ電気的に接続される第1外部電極4aおよび第2外部電極4bとを備え、第1外部電極4aおよび第2外部電極4bの配列方向に垂直な断面において、第1内部電極3aおよび第2内部電極3bと、積層体2の側面との間は、空孔6が多くなっていることから、誘電体層5における積層方向に垂直な方向の残留応力が低減される。従って、コンデンサ1が外部から衝撃を受けた場合であっても、誘電体層5と内部電極3との間の層間剥離の発生を抑制することができる。

(もっと読む)

積層セラミックキャパシタ及びその製造方法

【課題】信頼性に優れた高容量積層セラミックキャパシタ及びその製造方法を提供する。

【解決手段】本発明の一実施形態による積層セラミックキャパシタは、対向する第1及び第2側面、上記第1及び第2側面を連結する第3及び第4側面を有する積層本体と、上記積層本体の内部に形成され、上記第1側面及び第2側面に末端が露出する複数個の内部電極と、上記複数個の内部電極の末端を覆うように上記第1及び第2側面に形成される第1及び第2サイド部と、上記第3及び第4側面に形成され、上記内部電極と電気的に連結される外部電極とを含み、上記複数個の内部電極の末端を連結する仮想線と上記第1サイド部または第2サイド部の成す角度が90゜(π/2)以下になるように形成されている。

(もっと読む)

セラミック電子部品

【課題】特に薄型のセラミック電子部品において、実装時において加わる応力により生じ得るクラックを抑制する。

【解決手段】第1および第2の外部電極23,24は、セラミック素体22の実装面側に向く主面28上において、所定のギャップ領域を隔てて互いに対向するように配置されている。外部電極23,24は、下地層35とこれを被覆するCuめっき層36とを含む。下地層35のギャップ領域側の端部位置におけるCuめっき層36の厚みをt、下地層35のギャップ領域側の端部からCuめっき層36のギャップ領域側の端部までの距離をdとしたとき、0.1≦t/d≦0.5とされる。このように、Cuめっき層36を伸ばすことにより、外部電極23,24の、主面28上での先端部分への応力の集中を分散することが可能となり、実装時に生じ得るクラックを抑制することができる。

(もっと読む)

積層型セラミック電子部品

【課題】誘電体磁器組成物に含まれる成分の含有量にかかわらず、比誘電率および容量温度特性等の誘電特性を向上できる積層型セラミック電子部品を提供する。

【解決手段】誘電体層2と内部電極層とが積層された素子本体を有する積層型セラミック電子部品であって、誘電体層は、一般式ABO3(AはBa、CaおよびSrから選ばれる1つ以上、BはTi、ZrおよびHfから選ばれる1つ以上)で表され、ペロブスカイト型構造を有する化合物と、Mgの酸化物と、ScおよびYを含む希土類元素の酸化物と、Siを含む酸化物と、を含む誘電体磁器組成物から構成される。該誘電体磁器組成物は、誘電体粒子20と粒界22とを有しており、粒界におけるMgの含有割合をD(Mg)、Siの含有割合をD(Si)とすると、D(Mg)がMgO換算で0.2〜1.8重量%、D(Si)がSiO2換算で0.4〜8.0重量%である。

(もっと読む)

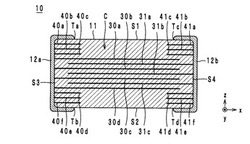

積層セラミック電子部品及びその製造方法

【課題】誘電体層の厚さを均一化させることにより耐電圧特性を向上させ、熱衝撃によるクラックを抑制して信頼性を向上するとともに、静電容量の大容量化を具現した積層セラミック電子部品とその製造方法を提供する。

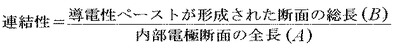

【解決手段】平均厚さが1μm以下である複数の誘電体層1が積層されたセラミック本体と、上記誘電体層1に形成され、下記数式で表される連結性が90%以上である内部電極層2とを含み、上記誘電体層1に対する上記内部電極層2の厚さ比率が0.8〜1.3である。 (もっと読む)

(もっと読む)

フィルムコンデンサの製造方法

【課題】多数のフィルムコンデンサを、十分に低い製造コストで、より効率的に製造可能な方法を提供する。

【解決手段】加圧装置38に取り付けられて、圧縮変形させられたコンデンサ素子12の互いに対向する一対の端面にメタリコン電極29をそれぞれ形成した後、コンデンサ素子12を加圧装置38に取り付けたままで、コンデンサ素子12に対して熱エージング処理を施した後、コンデンサ素子12を加圧装置38から取り外した状態で、コンデンサ素子12に対して更に熱エージング処理を施すことにより、コンデンサ素子12の圧縮変形状態を固定するようにした。

(もっと読む)

セラミック電子部品

【課題】機械的耐久性に優れているセラミック電子部品を提供する。

【解決手段】セラミック電子部品1は、複数の第1の補強層17aをさらに備えている。複数の第1の補強層17aは、第1の外層部10Bにおいて、長さ方向L及び幅方向Wに沿って延びるように形成されており、厚み方向Tに沿って積層されている。セラミック素体10の複数の第1の補強層17aが設けられている領域10Fにおける第1の補強層17aが占める体積割合は、有効部10Aにおける第1及び第2の内部電極11,12が占める体積割合よりも大きい。

(もっと読む)

1 - 20 / 176

[ Back to top ]