Fターム[5E336GG11]の内容

プリント板への電気部品等の実装構造 (16,219) | 目的又は効果 (2,617) | 電気的なもの (296)

Fターム[5E336GG11]の下位に属するFターム

絶縁性 (40)

Fターム[5E336GG11]に分類される特許

201 - 220 / 256

配線構造を有するメモリモジュール

【課題】配線の長さを最小化し、配線間のインピーダンスの不一致を解決するためのメモリモジュールを提供する。

【解決手段】本発明のメモリモジュールは、印刷回路基板と、前記印刷回路基板の第1面上に配置される第1列のメモリ素子と、前記印刷回路基板の第2面上に配置される第2列のメモリ素子と、多数のビアとを備え、前記第1列のメモリ素子は、前記印刷回路基板の基準軸に対して前記第2列の位置対をなすメモリ素子に各々オーバーラップされるように配置され、前記それぞれのビアは、前記第1列の第1メモリ素子の入出力端子を前記第2列の第2メモリ素子の入出力端子に連結させる経路の一部となり、前記第2列の第2メモリ素子は、前記第1メモリ素子に対応して位置対をなす第2列の第3メモリ素子に隣接することを特徴とする。

(もっと読む)

大電流用両面プリント基板

【課題】一方の導電パターンに過大電流が集中して、異常発熱を起こすことのない大電流用両面プリント基板を提供する。

【解決手段】絶縁材からなる絶縁基板2と、前記絶縁基板2の表裏両面に形成された導電パターン3と、リード部品(図示せず)のリード5を挿入するためのスルーホール4とを備え、前記絶縁基板2へ前記リード部品を実装し半田ディップした後、前記リード部品側から前記スルーホール4に追加の追い半田7を充填するもので、リード部品のリード5に流れる大電流を、前記絶縁基板2の表裏両面に形成した導電パターン3に案分してバランスよく分流でき、一方の導電パターン3に過大電流が集中し、異常発熱による発火、発煙という不安全な現象を回避し、安全性、信頼性の高い大電流用プリント基板を提供することができる。

(もっと読む)

配線基板

【課題】 発熱部品が倒れるということをあらかじめ想定しておき、発熱部品が倒れた場合であっても、その発熱部品が非発熱部品に接触したり近接し過ぎたりして部品性能などが損なわれるという事態を起こらなくする。

【解決手段】 発熱部品であるサーミスタ2と非発熱部品である円柱状の電解コンデンサ4とを備える配線基板Aにおいて、電解コンデンサ4に、発熱部品受止め部材6の環部61を嵌着してその突出片部62をサーミスタ2に対向させておく。サーミスタ2が電解コンデンサ4側に倒れ込んだときに、突出片部62がサーミスタ2を受け止めて電解コンデンサ4に接触しないようにする。

(もっと読む)

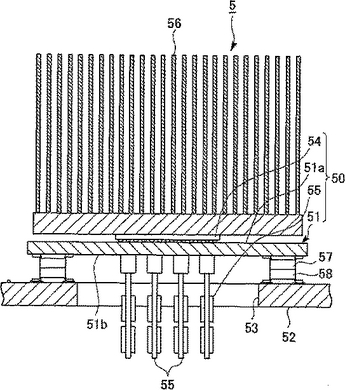

板金配線の実装構造

【課題】 実装部品の板金配線への接続を容易に行い、且つ、大電流が流れる板金配線で問題となる、出力リップル電圧に発生するペデスタル電圧現象を解決することのできる板金配線の実装構造を提供する。

【解決手段】 電解コンデンサ6,7,8は、絶縁板40を介してバスバー20,21に実装されており、そのリード端子6a,7a,8aはバスバー20,21に直接半田付け接続されている。リード端子6a,7a,8aが絶縁板40側から各リード挿通孔45,46へそれぞれ挿通され、その反対面(リード挿通孔46周辺部)からバスバー20,21に半田42により半田付けされている。これにより、導電ライン(線路)を極力太く短くできるため、出力リップル電圧におけるペデスタル電圧の発生を抑制することができる。

(もっと読む)

キャパシタ層形成材及びそのキャパシタ層形成材の製造方法並びにそのキャパシタ層形成材を用いて得られる内蔵キャパシタ層を備えたプリント配線板

【課題】製造コストメリットに優れたゾル−ゲル法を用いた誘電膜であって、従来に無い高い電気容量を備え且つ長寿命のキャパシタ回路を製造出来るキャパシタ層形成材を提供する。

【解決手段】上部電極形成に用いる第1導電層2と下部電極形成に用いる第2導電層3との間に誘電層4を備えるキャパシタ層形成材1において、当該誘電層4は、ゾル−ゲル法で形成した酸化物誘電膜であり、当該誘電層の厚さ方向及び平面方向に成長した粗大化結晶組織であり、且つ、粒径(長径)が50nm〜300nmの酸化物結晶組織を含むことを特徴としたキャパシタ層形成材を採用する。そして、このキャパシタ層形成材を効率よく得るための製造方法を提供する。

(もっと読む)

配線方法

【課題】 信頼性を向上させる配線方法を提供することにある。

【解決手段】 導通パターン14,16,18と、開口46を有し、導通パターン14,16,18が、開口46を掛け渡すように形成された基板44と、を有する第1の配線基板42を用意する。第1の配線基板42の導通パターン14,16,18と、第2の配線基板に形成された電極28と、を開口46内で電気的に接続する。及び、第1の配線基板42を複数のセクションに分離する。第1の配線基板42の分離は、導通パターン14,16,18の少なくとも一部を開口46内で切断することを含む。

(もっと読む)

配線構造及び部品実装構造

【課題】 電極構造を多層化することにより腐食等による信頼性の低下を抑えるとともに、各層間の接続抵抗(コンタクト抵抗)を抑える。

【解決手段】 接続端子部Tは、2層以上の導体層(第1導体層2及び第2導体層3)が積層された構造を有し、積層された積層構造部分の面積が拡大されている。例えば、積層構造部分の面積を、接続端子部T上に接続されるバンプBの接触面積の2倍以上とする。接続端子部Tが所定のピッチpで配列される場合、積層構造部分の面積を、ピッチpを1辺とする正方形の面積よりも大とする。あるいは、積層構造部分を長方形とする。

(もっと読む)

基板実装方法及び実装構造

少なくとも2枚の基板を絶縁部材を介して貼り合わせることにより貼合せ基板を形成し、前記貼合せ基板にスルーホールを形成し、前記貼合せ基板の一方の面に第1の電子部品を搭載し、前記貼合せ基板の他方の面に第2の電子部品を搭載し、前記第1の電子部品と前記第2の電子部品とを、前記スルーホールを介して電気的に接続する。  (もっと読む)

(もっと読む)

ランド構造,インダクタ部品取付構造及び無線通信機の電源回路

【課題】 インダクタ部品を所望の角度で実装することができるようにして、電子部品同士の磁気的相互干渉を回避すると共に回路の高密度化と小型化とを図ることができるランド構造,インダクタ部品取付構造及び無線通信機の電源回路を提供する。

【解決手段】 第1の配線パターン30が接続された第1のランド3−1と、第2の配線パターン40が接続された第2のランド4−1とを備えるランド構造において、インダクタ部品2の外部電極21,22を第1及び第2のランド3−1,4−1に接続して、インダクタ部品取付構造を構成する。第1及び第2のランド3−1,4−1は円弧状をなして対向し、インダクタ部品2は、対象電子部品との磁気結合を最小にする角度で、第1及び第2のランド3−1,4−1に取り付けられている。好ましくは、レジスト5を第1及び第2のランド3−1,4−1に設ける。

(もっと読む)

半導体素子の実装方法及び実装構造、装置

【課題】特殊な基板や半導体素子の使用を不要とし、基板厚みにかかわらず適用可能で、放熱性、高周波接地特性に優れ、不具合、破損等での交換が容易な半導体素子の実装方法及び実装構造を提供する。

【解決手段】凸部を有する金属シャーシ2と、当該凸部に対応する位置の表裏を貫通する開口部7と上面の配線パターンを有し、前記凸形状が嵌入され金属シャーシ2に配置された基板3と、前記金属シャーシ2の凸部の上面に放熱用電極5が搭載され、リード線4が前記配線パターンと接続された基板表面実装型のプラスチック樹脂モールドパッケージの半導体素子1とで構成される。

(もっと読む)

ノイズ低減機能を備えた回路基板

【課題】

デジタル回路ブロックとアナログ回路ブロックとが同一平面上に混在して実装された回路基板において、各回路ブロック間に混入するノイズを低減できるようにする。

【解決手段】

回路基板1の中央にアナログ回路ブロック10が形成され、そのアナログ回路ブロック10の両側にデジタル回路ブロック4A,4Bが形成されている。アナログ回路ブロック10と各デジタル回路ブロック4A,4Bの間に複数の電解コンデンサ15を接続する共通のグランドパターン16が形成される。電解コンデンサ15は極性を一方向に揃えるようにグランドパターン16に接続され、回路基板1に形成されたアナログ回路ブロック10と各デジタル回路ブロック4A,4Bとの間を遮るように立設され、これら電解コンデンサ15群によってデジタル回路ブロック4A,4Bから放射される高周波ノイズをシールドし、アナログ回路ブロック10への混入を抑制する。

(もっと読む)

通信モジュール

【課題】 モジュールのマイクロ化の効果を達成し、製造コストと組み立ての難度を低減する通信モジュールを提供する。

【解決手段】 第一表面と少なくとも凹部を有する支持体、前記凹部の中に位置される第一電子部品、および前記第一表面に位置され、且つ、前記第一電子部品と電気的接続される接続パットを含む。

(もっと読む)

接続要素を有する高周波チップパッケージ

無線周波チップパッケージは、接続要素、例えばチップ(72、84)を有する回路基板(52)又は可撓性回路テープを、底部平面要素(20)、例えば大きな熱伝導プレート(22)及びプレート平面から上方へ突き出るリード(40、42)を含むリードフレームと一緒にアセンブルすることによって形成される。アセンブリステップは、接続要素(52)の底部側にあるチップ(72)の裏面(78)を熱導体(22)と近接させ、接続要素上の導電性トレース(60)をリードと連結する。結果のアセンブリは封止され、リードの底端(45)に端子が露出されて残される。封止されたアセンブリは、回路基板(102)へ表面実装されてよい。リード(40、42)は、接続要素(52)と回路基板(102)との間にロバストな電気接続を提供する。  (もっと読む)

(もっと読む)

回路基板

【課題】 配線基板に搭載されたノイズ除去部品からの放熱を効率良く行えるようにすることでノイズ除去部品によるノイズ除去を適正に行えるようにした回路基板を提供する。

【解決手段】 シグナルトレース2に搭載された積層コンデンサMC等(ノイズ除去部品)が熱を持った場合でも、該積層コンデンサMC等の放熱導体部RCに導通する内部電極から直接的に放熱導体部RC及びこれに接続されたシールド部品80,90に伝えて効率的な放熱を行うことができ、これにより積層コンデンサMC等の部品特性が熱によって変化することを防止して安定したノイズ除去効果を得ることができる。

(もっと読む)

高周波回路、高周波モジュールおよび通信装置

【課題】 基板に電極パターンを形成し素子を実装してなる高周波回路において、基板内に発生し得る不要波を抑圧して信号の漏洩・損失を抑えて特性劣化を生じないようにした高周波回路、それを備えた高周波モジュールおよび通信装置を構成する。

【解決手段】 基板1の上下面に、その基板1の厚さ方向の中央面に対して面対称の電極パターン12a,12bを備え、その電極パターン12a,12bの面対称の位置に、対をなす上面実装素子5aおよび下面実装素子5bをそれぞれ実装する。この上面実装素子5aと下面実装素子5bのそれぞれの実装用端子位置は互いに面対称の関係にある。この構造により、表面波や平行平板モードの波などの不要波の励振が抑制され、信号の漏洩・損失・特性劣化が抑えられる。

(もっと読む)

3端子積層コンデンサ及び実装構造

【課題】

ESLを低減して、広い周波数帯域で良好なデカップリングを実現する。

【解決手段】

積層体12の短手方向端面全体を覆うように、積層体12の側面に長手方向に沿ってGND電極14が設けられ、信号電極16,18は、積層体12の長手方向端面であって、前記GND電極14に挟まれるようにコ字状に形成される。GND電極14に接続されるGND側導体パターン20は、誘電体シート22の短手方向の端からは露出し、長手方向の端からは露出しないように形成され、短手側の端14Aが、GND電極14に接合する。前記信号電極16,18に接続される信号側導体パターン24は、誘電体シート26の長手方向の端からは中央部が露出し、短手方向の端からは露出しないように形成され、長手側の端16A,18Aが信号電極16,18にそれぞれ接合する。

(もっと読む)

電子部品の実装構造及び実装方法

プリント基板と、このプリント基板上に搭載された複数の電子部品と、前記電子部品の間で折り曲げられ積層された前記プリント基板の折り重ね部分と、前記折り重ね部分の両面に形成されたスルーホールと、前記スルーホールを介して前記電子部品間を接続し、前記電子部品と前記スルーホールとを接続する配線と、を備えている。  (もっと読む)

(もっと読む)

プリント配線板

【課題】IC/LSIの動作安定、ノイズ抑制、実装面積等において最適なバイパスコンデンサの構成決定の手法を提供する。

【解決手段】各電源端子に対し、バイパスコンデンサをC1,C2,C3の3つを配置し、C1は用意できる最大の容量値のものに決定し、又、IC/LSIの電源端子から見たIC/LSIの内部のインピーダンス特性において極小点となる共振周波数と、IC/LSIの電源端子から見た、概略バイパスコンデンサの定数とバイパスコンデンサの自己インダクタンスと電源ピンからバイパスコンデンサまでの配線によって概略決まるプリント配線板上の給電回路のインピーダンス特性における共振周波数を一致させるようにC2,C3容量値を確定することで、試行錯誤的な給電回路の最適化作業の負荷を低減させる。

(もっと読む)

半導体素子のシールド構造及びシールド方法

【課題】 半導体素子のフリップチップ実装において、シールドのための部品点数を増加させることなく確実な電磁的シールドを実現でき、該半導体素子の直下にGNDパターンを形成しなければならないという制限をなくすことができ、回路設計の自由度を拡大することができるとともに、プリント基板の高密度化を図ることができるようにする。

【解決手段】 プリント基板20の部品面20Aにアンダーフィルを介して半導体素子10をフリップチップ実装する場合のシールド構造であって、半導体素子10の接着面10A外側に電極部11,11…を設け、プリント基板20の部品面20Aと半導体素子10の接着面10Aとの間に、樹脂接着剤に磁性体を含有した第1アンダーフィル31を介在させるとともに、半導体素子10の電極部11,11…を樹脂接着剤である第2アンダーフィル32により絶縁してある。

(もっと読む)

電子装置

【課題】 断線を低減することができる電子装置を提供すること。

【解決手段】 回路基板10は、図1(a)に示すように基板側電極11、回路素子20を実装する段差である実装部12などを備える。この実装部12は、回路基板10の表面と回路素子20の表面との段差を低減させるためのものであり、回路素子20の外形に応じた形状であり、回路基板10と回路素子20との間に略隙間がないように回路素子20を挿入できる程度の大きさを有する。そして、図1(b)に示すように実装部12に回路素子20が挿入された状態において、図1(c)に示すようにスキージ板80及びスキージ82を用いて、導電性ペースト30がスクリーン印刷される。従って、図1(d)に示すように回路基板10の表面と回路素子20の表面とが略同一平面となる状態で導電性ペースト30が設けられる。

(もっと読む)

201 - 220 / 256

[ Back to top ]