Fターム[5E336GG11]の内容

プリント板への電気部品等の実装構造 (16,219) | 目的又は効果 (2,617) | 電気的なもの (296)

Fターム[5E336GG11]の下位に属するFターム

絶縁性 (40)

Fターム[5E336GG11]に分類される特許

101 - 120 / 256

電子部品装置

【課題】 高周波回路用プリント配線板に表面実装する電子部品の線路インピーダンスの整合性を保ち、良好な高周波特性を維持するとともに表面実装型チップ部品の実装工程におけるチップ立ちやチップ回転ズレ等が発生しない電子部品装置を得る。

【解決手段】 第1ストリップ線路に接続された第1ランドパターンと、対応する第1対向ランドパターンと、第1ランドパターンと連続して接続された第2ランドパターンと、対応する第2対向ランドパターンと、この第2対向ランドパターンに連続して接続された第3ランドパターンと、対応する第3対向ランドパターンと、第3ランドパターンに接続された第2ストリップ線路を有し、第1ランドパターンと第2ランドパターンとの加算面積が、第2対向ランドパターンと第3ランドパターンとの加算面積に等しくした。

(もっと読む)

プリント配線板構造、電子部品の実装方法および電子機器

【課題】接続信頼性を低下させることなく、高密度実装、高密度配線を可能にしたプリント配線板構造を提供する。

【解決手段】プリント配線板11の両部品実装面11A,11Bにおいて、サブストレート相互(12a−13a)は一部が重なり、半導体チップ相互(12b−13b)は重ならない位置関係(S)で、第1の部品実装面11Aに第1の半導体パッケージ12を実装し、第2の部品実装面11Bに第2の半導体パッケージ13を実装している。

(もっと読む)

プリント配線板の電源ノイズフィルタ構造

【課題】電源供給系に重畳される高周波ノイズに対する抑制効果の向上が図れるバイパス用コンデンサの実装構造を備えたプリント配線板の電源ノイズフィルタ構造を得ること。

【解決手段】電源配線を、電源配線2aと電源配線2bとに2分割し、その分割端側の配線上面に、コンデンサ実装用電源パッド5a,5bをそれぞれ設け、その分割端間を2端子チップコンデンサであるバイパス用コンデンサ4の電極部4aで接続する。電源配線2a側から電源配線2b側へ向かう高周波ノイズは、全てバイパス用コンデンサ4の電極部4aを流れるので、電極部4bを通ってGND層3へバイパスする性能が向上する。そして、分割端間を電源配線の迂回パターン8によって接続し、バイパス用コンデンサ4の剥離などによる電源配線2a,2b間の不動通を回避する。電源配線の迂回パターン8の高周波インピーダンスはバイパス用コンデンサ4の電極部4aよりも大きくしてある。

(もっと読む)

回路基板及び電子機器

【課題】マイクロストリップラインと他の信号ラインとが交差する構成において、当該交差部分におけるインピーダンス整合を好適に行うことができる回路基板及び電子機器を提供すること。

【解決手段】第1の層50aは、第1の信号線50cと、基準電位に電気的に接続された基準電位部50dとが形成されている。第2の層50bは、第1の信号線50cに対向して配設されると共に、基準電位に電気的に接続された基準電位部50eと、基準電位部50eを挟んで電気的に離れて配置される第2の信号線50gと、が形成されている。第2の層50bには、基準電位部50eに導電性の導電性部材50fが実装され、この導電性部材50fが、基準電位部50eを挟んで電気的に離れて配置された第2の信号線50gを電気的に接続する。

(もっと読む)

遅延回路および遅延時間調整方法

【課題】実装基板や半導体パッケージなどの配線基板の各配線の信号伝播の遅延時間を容易に調整および変更することができ、なおかつ配線基板の小型化および高密度実装にも対応可能な遅延回路および遅延時間調整方法を実現する。

【解決手段】遅延回路1は、遅延時間の設定を指示するインタフェース11と、任意の遅延時間にプログラム可能な遅延素子12と、を備え、遅延素子12の遅延時間が、インタフェース11から指示により設定される。

(もっと読む)

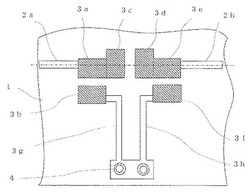

プリント配線板の電源ノイズフィルタ構造

【課題】電源供給系に重畳される高周波ノイズに対する抑制効果の向上が図れるバイパス用コンデンサの実装構造を備えたプリント配線板の電源ノイズフィルタ構造を得ること。

【解決手段】電源配線を、電源配線2aと電源配線2bとに2分割し、その分割端側の配線上面に、コンデンサ実装用電源パッド5a,5bをそれぞれ設け、その分割端間を2端子チップコンデンサであるバイパス用コンデンサ4の一方の電極部4aで接続する。電源配線2a側から電源配線2b側に向かう高周波ノイズは、全てバイパス用コンデンサ4の電極部4aを流れるので、他方の電極部4bを通ってGND層3へバイパスする性能が向上し、高周波ノイズに対する抑制効果の向上が図れる。

(もっと読む)

はんだのない電子機器組立体およびその製造方法

本発明は、電子機器組立体400およびその製造方法800、900、1000、1200、1400、1500、1600、1700を提供する。組立体400は、はんだを使用しない。部品406、またはI/Oリード412を有する部品パッケージ402、802、804、806は、800で、平面基板808上に配置される。組立体は、1000で、成形またはドリリングされて基板808を貫通し部品のリード412まで至るバイア420、1002と共に、電気的絶縁材料908を用いて、900で、包み込まれる。次いで組立体は、1200でメッキされ、包み込みおよびドリリングの工程が1500で繰り返されて、所望の層422、1502、1702が構築される。組立体は、1800で結合されうる。結合された組立体の中に、ピン2202a、2202b、および2202c、メザニン相互接続デバイス2204、ヒートスプレッダ2402、ならびにヒートスプレッダとヒートシンクの組合せ2602を含む品目が、挿入されうる。エッジカードコネクタ2802は、結合された組立体に取り付けられうる。  (もっと読む)

(もっと読む)

電子機器

【課題】本体の大型化を抑えるとともに、回路基板に搭載された集積回路に静電気が印加されることを防止し、信頼性を高めた電子機器を提供する。

【解決手段】集積回路11を搭載した回路基板10上にコンデンサ13を搭載し、このコンデンサ13は、一方の端子を当該回路基板10上に形成されているグランドパターン12に接続し、且つ、他方の端子を当該回路基板10上に形成されている回路パターンに接続することなく、当該回路基板10上方に延ばした状態で搭載している。静電気が発生した場合、回路基板10に搭載されている他の電子部品よりも高い位置にある当該回路基板10上方に延ばしてある端子に印加され、グランドパターン12と接続している一方の端子に流れ、グランドパターン12に放電される。したがって、静電気が集積回路11に印加することを抑えられる。

(もっと読む)

回路基板及び回路基板の製造方法

【課題】効率よく製造することができる回路基板及び回路基板の製造方法を提供することを目的とする。

【解決手段】回路基板1は、金属基材2及び前記金属基材2上に設けられたプリント基板3からなる基板本体4と、前記基板本体4上に実装した実装部品5と、前記基板本体4に穿設した貫通穴7に圧入されたスタッド部材6とを備え、前記スタッド部材6により装置本体に固定する。前記基板本体4は、前記貫通穴7の前記プリント基板3側周縁にグランドパターン10を設け、前記スタッド部材6は、半田15を印刷した前記グランドパターン10側から前記貫通穴7に圧入され、前記金属基材2と前記グランドパターン10とを電気的に接続する。

(もっと読む)

プレスフィット端子と基板との接続構造

【課題】端子挿入力を下げても、端子保持力を向上させることができ、信頼性の高い電気的接続を実現できるプレスフィット端子と基板との接続構造を提供する。

【解決手段】本接続構造は、プレスフィット端子3の表面には第1のメッキ層4が被覆され、基板1のスルーホール2の内壁には第2のメッキ層7が被覆され、基板1の内部には熱伝導性を備えたコア層5を有し、コア層5の端部は、第2のメッキ層7又はその近傍まで延びて形成され、第1のメッキ層4と第2のメッキ層7との間を拡散接合させることにより、プレスフィット端子3を基板1のスルーホール2内に保持させる。

(もっと読む)

小型電子機器における電子部品モジュール搭載構造

【課題】薄型化のために回路基板の穴に通すカメラモジュールを搭載する部材として、支持強度を確保するとともに、導電性も確保する。

【解決手段】小型電子機器におけるカメラモジュール搭載構造であって、回路基板2に形成された穴21にカメラモジュール3を通し、このカメラモジュール3を金属ケース1に搭載する。具体的には、カメラモジュール3は、そのカメラ30の側方に突出する第1基板31を備え、この第1基板31のカメラ30の側方突出部に第2基板4が搭載されている。また、金属ケース1のカメラモジュール搭載部11には、第1基板31の側方突出部に対応する凹段部12が形成されている。そして、第2基板4には、DSP5が搭載されるとともに、回路基板2に接続するフレキシブル基板6が搭載されている。

(もっと読む)

部品内蔵実装基板

【課題】高速・高密度電子機器で特に信号品質の確保が必要なCPU−メモリ間のアドレス線において、小型化と高周波特性確保の両立が実現できる部品内蔵実装基板を提供する。

【解決手段】絶縁基板100の表面上に、CPU101と、チップ部品としての並列終端抵抗105と、メモリ102とが搭載されている。絶縁基板100の内部には、CPU101の直下に第1のデカップリングキャパシタ106aが内蔵され、メモリ102の直下に第2のデカップリングキャパシタ106bが内蔵されている。並列終端抵抗105の直下には、膜部品としての直列終端抵抗103b及び信号品質補償用キャパシタ104bがその面を絶縁基板100の表面に平行にして内蔵されており、両者間に第3のデカップリングキャパシタ106cが内蔵されている。

(もっと読む)

電子部品収容基板及びその製造方法

【課題】導電材と収容された電子部品との接続強度を向上させ、収容された電子部品上に他の電子部品を実装可能とする電子部品収容基板及びその製造方法を提供する。

【解決手段】電子部品収容基板40において、基板10をその厚み方向に貫いた孔部27に電子部品60を収容した電子部品収容基板において、電子部品に、互いの端部側に対向する一対の電極部62a,62bを設け、基板の両面にそれぞれ配線層31,32を設け、孔部を、連通部20を介し、一面側と他面側とに開口し、連通部の断面積より大なる断面積となる第1の凹状段部22と第2の凹状段部23とで形成し、第1の凹状段部及び前記第2の凹状段部の各内面側に配線層に電気的に接続するための導電層を形成し、各導電層と各電極部とを、配線層の表面に連続する略平坦な面を有する導電部材30でそれぞれ電気的に接続した構成とする。

(もっと読む)

回路基板

【課題】回路基板の一方の面に配設されたコネクタと他方の面に配設されたコネクタとを繋ぐ伝送路長を短くし、伝送路信号品質を向上させる。

【解決手段】表面41に配設されたコネクタ51と、コネクタ51に対向する裏面42の箇所に配設されたコネクタ52と、コネクタ51を表面41に半田付けするためのコネクタ実装用パターン53と、コネクタ52を半田付けするためのコネクタ実装用パターンと54を備え、コネクタ実装用パターン53,54の端部に、スルーホール55を形成し、コネクタ実装用パターン53,54を電気的に接続する。

(もっと読む)

回路基板と回路基板固定方法および電子機器

【課題】長期的に安定した電気的接続を容易かつ安価に実現する。

【解決手段】回路基板10では、取付孔11の周囲に位置する接地パターン12の接続領域12aに導電性ペーストを用いて導電膜13を形成する。筐体20には、回路基板10の取付孔11と対向する位置にネジ孔21を螺刻しておく。回路基板10は、ネジ31の座面と導電膜13が対向するように筐体20の所定位置に載置して、回路基板10側からネジ孔21にネジ31を螺入して回路基板10を筐体20に固定する。このとき、回路基板10の接地パターン12と筐体20は、導電膜13とネジ31を介して電気的に導通状態となる。接地パターン12の接続領域12aは導電膜13で覆われているので、回路基板10と筐体20は、長期にわたって安定した導通状態を確保できる。

(もっと読む)

コンデンサの実装方法及びプリント基板

【課題】プリント基板に配置可能な最小ビア間隔よりも短い端子間隔をもつコンデンサを搭載する場合であっても、従来よりも低抵抗、低インダクタンスを実現し、コンデンサの性能を十分に発揮することが可能なコンデンサの実装方法及びプリント基板を提供する。

【解決手段】本発明は、プリント基板の最小ビア間隔よりも短い端子間隔を持つコンデンサの実装方法であって、前記コンデンサの端子箇所のプリント基板を削り、電源ライン又は接地ラインを表面に露出させ、前記コンデンサの端子を、前記露出された電源ライン又は接地ラインに直接ハンダ付けするように構成した。

(もっと読む)

成端のばらつきが低減され、性能が改善されたモジュラコネクタ

電気通信コネクタ500であって、コネクタハウジング501と、コネクタハウジング501内の複数のコネクタコンタクトと、コネクタコンタクトの成端端部を受け取るための第1のめっきスルーホールを有する基板503であって、第1のめっきスルーホールが基板503上の一領域内に構成された基板503と、基板503内の第2のめっきスルーホール内に配置される複数の成端コンタクト504とを含み、第2のめっきスルーホールが基板503上の該一領域を横断する、電気通信コネクタ500が提供される。  (もっと読む)

(もっと読む)

プリント配線基板

【課題】プリント配線基板のインピーダンス特性を向上させる。

【解決手段】プリント配線基板51のL1層には、L1層とはことなる層に設けられた電源パターンを介して、メモリ61−1、メモリ61−2、およびメモリコントローラ62に電力を供給する電力供給部63が配置されている。プリント配線基板51上において、電力供給部63をメモリ61−1、メモリ61−2、およびメモリコントローラ62に囲まれる位置に配置することで、電力供給部63からメモリ61−1、メモリ61−2、またはメモリコントローラ62までの電力を供給するための配線の長さをより短くすることができ、インダクタンス成分をより小さくすることができる。これにより、プリント配線基板51における電源とグランドとの間のインピーダンスの増加を抑制することができる。本発明は、プリント配線基板に適用することができる。

(もっと読む)

電子部品実装装置

【課題】装置全体の面積、高さを増加させること無く、より放熱効果を向上させるができる電子部品実装装置を提供する。

【解決手段】本発明に係る電子部品実装装置100は、プリント基板20と当該プリント基板20に実装される電子部品1,2とを備えている。プリント基板20は複層構造であり、内層には、ベタパターンを有するベタパターン層4が配設されている。また、ベタパターンの少なくとも一部が露出されるように、ベタパターン層より上層に形成されている層が開口されている。そして、当該露出しているベタパターン上に電子部品1が実装されている。

(もっと読む)

半導体装置の製造方法、並びに半導体装置

【課題】積層セラミックコンデンサを含む電子部品の配線基板への実装後に、積層セラミックコンデンサの容量の微小調整から大幅な調整までが可能となる半導体装置の製造方法を提供する。

【解決手段】積層体11と端部電極12、13とからなる積層セラミックコンデンサ10を配線基板14の実装面に実装し、その実装面をモールド樹脂15で樹脂封止した後、モールド樹脂15の上部からレーザ光を照射し、モールド樹脂15の一部および積層体11の一部を除去して加工孔16を形成し、積層体11に含まれる複数枚の金属板のうちの一部を切断する。

(もっと読む)

101 - 120 / 256

[ Back to top ]