Fターム[5E346GG17]の内容

多層プリント配線板の製造 (97,916) | 製造・加工・処理手段 (12,987) | 製造工程・製造装置 (12,564) | メッキ工程 (1,540)

Fターム[5E346GG17]に分類される特許

161 - 180 / 1,540

多層プリント配線板、及び、多層プリント配線板の製造方法

【課題】 パッドとソルダーレジスト層との密着性を確保しつつ、パッドと半田バンプとの間の電気抵抗が増大することを防止することができる多層プリント配線板を提供する。

【解決手段】 第1層間樹脂絶縁層と、上記第1層間樹脂絶縁層上に形成されて、電子部品を搭載するためのパッドと、上記第1層間樹脂絶縁層と上記パッドとの上に形成され、上記パッドに到達する開口部を有するソルダーレジスト層と、上記開口部の底部に位置し、上記パッド上に形成されている保護膜とを備える多層プリント配線板であって、上記パッドの表面に、Sn、Ni、Zn、Co、Ti、Pd、Ag、Pt及びAuのうちの少なくとも1種の金属を含む金属層が形成され、上記金属層上に、カップリング剤からなる被膜が形成され、上記保護膜の少なくとも一部は、上記開口部によって露出される上記パッドの露出面に直接形成されており、上記ソルダーレジスト層は、エポキシ樹脂からなることを特徴とする多層プリント配線板。

(もっと読む)

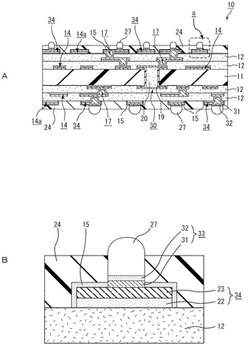

電子部品内蔵配線板

【課題】熱変化や外力等に起因した応力による性能劣化を抑制する。

【解決手段】配線板10が、基板を貫通する開口部R100に配置され、複数の第1パッド200aを有する電子部品200と、基板上及び電子部品200上に形成される積層部と、積層部上に形成される複数の第1外部接続端子321b及び複数の第2外部接続端子322bと、を有する。第1外部接続端子321bは、第1パッド200aの直上を避けつつ電子部品200の直上に形成され、且つ、第2外部接続端子322bは、基板の直上に形成され、1つの主面に投影した場合において、第1外部接続端子321bは、第1パッド200aに囲まれるように配置され、第1パッド200a及び第1外部接続端子321bは、第2外部接続端子322bに囲まれるように配置され、積層部における基板に最も近い絶縁層を構成する材料が、開口部R100における基板と電子部品200との隙間に充填される。

(もっと読む)

配線基板、半導体装置及び配線基板の製造方法

【課題】配線密度を向上させることのできる配線基板、半導体装置及び配線基板の製造方法を提供する。

【解決手段】配線基板は、第1配線層33と、第1配線層33の上に形成された第1絶縁層36と、第1絶縁層36の上に形成された第2配線層38と、第2配線層38の上に形成された第2絶縁層39と、絶縁層36,39の厚み方向に貫通して充填され、第1配線層33のランドL1に接続されるビア40とを有している。第2配線層38は、ビア40の径よりも小さい径の接続部38Aによってビア40と接続されている。また、ビア40は、その上面がパッド5として第2絶縁層39から露出されている。

(もっと読む)

回路形成用支持基板、及び半導体素子搭載用パッケージ基板の製造方法

【課題】パッケージ基板とその製造方法の改良を図る。

【解決手段】コア基板1は、銅張積層板2の両側に銅張積層板2よりサイズの小さい銅箔3を配置し、第1の回路基板10とする。次いで絶縁樹脂層4及び外層となる銅箔5を接着した構成へ積層する。この基板を第2の回路基板20とし、銅箔5上にコンフォーマルマスクを形成して第3の回路基板30とし、非貫通孔を形成して第4の回路基板40とする。非貫通孔を銅めっきして導通し第5の回路基板50とする。銅箔3よりも小さなサイズで裁断することにより支持体である銅張積層板2を除去し第6の回路基板60とし、配線をエッチングして第7の回路基板70を得る。ソルダーレジスト形成及び金めっき仕上げを施し、第8の回路基板80を得る。

(もっと読む)

電子部品検査用配線基板およびその製造方法

【課題】複数の樹脂絶縁層間に形成された配線層の位置が所定の位置に精度良く配設された樹脂絶縁部を含む電子部品検査用配線基板、および該配線基板を確実に製造できる製造方法を提供する。

【解決手段】厚み方向に沿って積層された複数の樹脂絶縁層z1〜z4と、該樹脂絶縁層z1〜z4の間に配置した配線層6〜8とを有する樹脂絶縁部RZを含む電子部品検査用配線基板1であって、樹脂絶縁層z1〜z4は、熱硬化性樹脂からなる第1樹脂層4と、該第1樹脂層4の両面に配設され且つ熱可塑性樹脂からなる一対の第2樹脂層5とから構成され、該樹脂絶縁層z1〜z4には、第1樹脂層4と一対の第2樹脂層5とを貫通し且つ一端部のみが上記配線層6〜8と接続されている非通電ビア導体dv1、あるいは、一端部のみが配線層6,7と接続され且つ該配線層6,7に隣接する一方の第2樹脂層5を貫通し、他端部が第1樹脂層4内で留まっている非通電ビア導体dv2が形成されている、電子部品検査用配線基板1。

(もっと読む)

多層プリント配線板の絶縁層用樹脂組成物

【課題】 多層プリント配線板の絶縁層としての使用に好適なエポキシ樹脂組成物であって、粗化処理後の粗化面の粗度が比較的小さいにもかかわらず、該粗化面がメッキ導体に対して高い密着力を示す絶縁層(層間絶縁層)を達成し得るエポキシ樹脂組成物の提供。

【解決手段】 (A)1分子中に2個以上のエポキシ基を有するエポキシ樹脂、(B)1分子中の平均水酸基含有率P((総水酸基数/総ベンゼン環数)の平均値)が0<P<1であるフェノール系硬化剤、(C)フェノキシ樹脂、及び(D)ゴム粒子を含有することを特徴とする、エポキシ樹脂組成物。

(もっと読む)

プリント配線板

【課題】 コンデンサを内蔵すると共に内蔵コンデンサとの接続を適切に取ることができるプリント配線板を提供する。

【解決手段】 チップコンデンサ20をコア基板30内に収容する。チップコンデンサ20は、銅めっき膜29を被覆した第1、第2電極21,22に銅めっきによりなるバイアホール46で電気的接続を取ってある。銅めっき膜29により第1、第2電極21,22の表面が平滑になり、接続層40に非貫通孔43を穿設した際に樹脂残さが残らず、バイアホール46とチップコンデンサ20との接続信頼性を高めることができる。

(もっと読む)

多層配線基板

【課題】チップ部品を搭載する基板主面側とその反対側の基板裏面側とにおける収縮率の差を緩和して配線基板の反りを抑えることができる多層配線基板を提供すること。

【解決手段】多層配線基板10は、基板主面11及び基板裏面12を有し、複数の樹脂絶縁層21〜27及び複数の導体層31〜38を積層してなる構造を有する。中心層としての樹脂絶縁層24を基準として、基板裏面12側に設けられる複数の導体層35〜38は、面積割合の平均が基板主面11側に設けられる複数の導体層31〜34の面積割合の平均よりも高くなるように形成されている。基板裏面12側に設けられる複数の樹脂絶縁層25〜27は、厚さ平均が基板主面11側に設けられる複数の樹脂絶縁層21〜23の厚さ平均よりも厚くなるように形成されている。

(もっと読む)

配線基板

【課題】ペア伝送路を伝播する信号が例えば35GHzを超えるような高周波であったとしても、信号の反射損や挿入損が小さいとともに共振が発生しにくく、信号を正常に伝播させることが可能な配線基板を提供すること。

【解決手段】帯状配線導体のペア80a,80bと外部接続パッドのペア60a,60bとが、ビア導体のペアおよびスルーホール導体のペア41a,41b〜45a,45bを介して接続されているとともにビアホール導体またはスルーホール導体のペア41a,41b〜45a,45bを取り囲む長円形の開口部91a〜96aを有する接地または電源導体層91〜96とを具備して成る配線基板であって、スルーホール導体のペア43a,43bのピッチが外部接続パッドのペア60a,60bのピッチより狭く開口部91a〜96aが絶縁板13の下面より上面側で小さい。

(もっと読む)

光感応性組成物及びこれを含むビルドアップ絶縁フィルム、そして前記ビルドアップ絶縁フィルムを用いた回路基板の製造方法

【課題】印刷回路基板の製造工程の効率を向上させることができる光感応性組成物及びこれを含むビルドアップ絶縁フィルム、そして前記ビルドアップ絶縁フィルムを用いた回路基板の製造方法を提供する。

【解決手段】本発明による回路基板の製造方法は、光感応性組成物を製造する段階、前記光感応性組成物をポリエチレンテレフタレート(Poly Ethylene Terephthalate:PET)材質からなったフィルム(film)にキャスティング(casting)処理して、ビルドアップ絶縁フィルムを製造する段階、基板上に前記ビルドアップ絶縁フィルムを積層する段階、フォトリソグラフィ工程を利用して、前記ビルドアップ絶縁フィルムにビアホール(via hole)を形成する段階、及び前記ビアホールに導電性ビアを形成する段階を含む。

(もっと読む)

エポキシ樹脂材料及び多層基板

【課題】粗化処理又はデスミア処理された硬化物の表面の表面粗さを小さくすることができ、該硬化物の表面に微細な配線を形成できるエポキシ樹脂材料を提供する。

【解決手段】本発明に係るエポキシ樹脂材料は、エポキシ当量が300以下であるエポキシ樹脂と硬化剤と無機フィラーとを含む。上記エポキシ樹脂材料中の上記無機フィラーを除く成分を配合した配合物を、80℃の5重量%水酸化ナトリウム水溶液に20分間浸漬したときに、無機フィラーを除く成分を配合した配合物の硬化物の重量減少が0.2重量%以下であり、かつ、上記無機フィラーを80℃の5重量%水酸化ナトリウム水溶液に2分間浸漬したときの無機フィラーの重量減少が1.0重量%以上8.0重量%以下である。

(もっと読む)

多層配線基板の製造方法

【課題】製造工程を簡素化することができる多層配線基板の製造方法を提供すること。

【解決手段】本発明の多層配線基板の製造方法では、準備工程において、厚さが100μm以下であるシート状のコア絶縁材13が準備され、穴あけ工程において、コア絶縁材13に対してレーザ穴加工が施されてコア主面14及びコア裏面15にて開口するスルーホール用穴16が形成される。導体形成工程において、無電解銅めっき後に電解銅めっきを施すことにより、コア絶縁材13のスルーホール用穴16内全体が充填されてなるスルーホール導体17が形成されるとともに、コア絶縁材13のコア主面14及びコア裏面15の上に導体層19が形成される。

(もっと読む)

回路基板、電源構造体、回路基板の製造方法、および電源構造体の製造方法

【課題】デカップリングコンデンサを必要とすることなく、電源層間での電磁エネルギーの共振による電磁放射と電源電圧の変動を防止可能な電源構造体および回路基板を提供する。

【解決手段】2つの電源層11,13と、電源層11−13間に挟持された層間絶縁膜15とを備えた電源構造体1であり、電源層11,13のうちの少なくとも一方が、有機材料に導電性微粒子を分散させた導電性微粒子分散膜aからなることを特徴とている。また回路基板は、このような構成の電源構造体1を備えたものである。

(もっと読む)

基板ユニット、ネットワーク装置および基板ユニットの製造方法

【課題】加工精度の高い基板ユニットを得ること。

【解決手段】基板ユニット1は、複数の層21〜24が積層され、異なる層21、22に配置された配線パターン41、42にそれぞれ接触する凹部21a、22aを有し、凹部21a、22a内に凹部21a、22aより深さが浅く、それぞれ同じ層に達する深さの凹部51a、52aを有するビア51、52が設けられたプリント配線板2と、凹部51a、52aの側部に電気的に接続されたコネクタピン32を有するプレスフィットコネクタ3と、を有する。

(もっと読む)

フレキシブルプリント配線板、電子機器、フレキシブルプリント配線板の製造方法

【課題】製造工程及び製造コストを増大させることなく製造することができる、放熱特性に優れたフレキシブルプリント配線板、該フレキシブルプリント配線板を備える電子機器及び前記フレキシブルプリント配線板の製造方法の提供を課題とする。

【解決手段】発熱性の電子部品20を実装するためのフレキシブルプリント配線板10であって、基材11の表裏両面に導電層12を設けてあるものにおいて、裏面側の導電層12のうち、前記電子部品20の直下を含む電子部品近傍領域Kに、凹凸パターンからなる放熱構造を設けてあると共に、前記基材11の表裏の導電層12を、前記電子部品近傍領域Kに設けたブラインドビアホールBを介して電気接続してある。

(もっと読む)

プリント基板の製造方法

【課題】先行技術は、加工時間の増加によりスループットが低くなることがあり、さらには、ビアおよび配線生成工程を多数利用する必要が出てきて、それら工程が複合的アライメント誤りを生じ得るので、特に目下のアライメント予算内では役に立たないであることがある。

【解決手段】基板に金属パネルをレーザ投影パターニングすることと、金属パネル上に誘電体層をラミネートすることと、基板の複数のビアを形成すべく基板をレーザ照射することと、基板のシードコートをレーザ活性化することと、基板のパターニングされていない部分からシードコートを洗浄することと、基板に、パターニングされたビルドアップ層を形成することと、複数の金属突起を形成すべく金属めっきをエッチングで除去することによりプリント回路を形成する。

(もっと読む)

プリント配線板、その製造方法、多層プリント配線板、及びその製造方法

【課題】層間導通に用いるビアホールの底面における接続信頼性を向上させる。

【解決手段】プリント配線板は、可撓性を有する第1の絶縁層21aと、第1の絶縁層21aの第1の主表面に配置されたシード層22aと、シード層22aの上に配置された第1の導体回路23aと、第1の絶縁層21aを貫通するビアホールの中に埋め込まれ、且つビアホールの底面に表出したシード層22aと第1の導体回路23aとの間に形成された第1の合金層28aに接触する層間導通部24aとを備える。層間導通部24aと第1の合金層28aとの親和性は、層間導通部24aとシード層22aとの親和性よりも高い。第1の合金層28aのうち層間導通部24aに接触する部分には、第1の合金層28aと層間導通部24aとの合金からなる第2の合金層27aが配置されている。

(もっと読む)

電子部品内蔵基板及びその製造方法

【課題】所望の特性を有する電子部品内蔵基板を安定して提供する。

【解決手段】電子部品と、電子部品を覆う部品内蔵絶縁層と、部品内蔵絶縁層の下面側に設けられた第1配線と、部品内蔵絶縁層の上面側に設けられた第2配線と、第2配線および電子部品の端子に電気的に接続する第1接続ビアと、第1配線および前記第2配線に電気的に接続する第2接続ビアを有し、電子部品の端子は保護絶縁膜に覆われ、この保護絶縁膜上に前記部品内蔵絶縁層が設けられ、第1接続ビアは、部品内蔵絶縁層と保護絶縁膜を貫通して電子部品の端子に接している、電子部品内蔵基板。

(もっと読む)

プリント配線板、その製造方法、多層プリント配線板、及びその製造方法

【課題】層間導通に用いるビアホールの底面における接続信頼性を向上させる。

【解決手段】プリント配線板は、可撓性を有する第1の絶縁層21aと、第1の絶縁層21aの第1の主表面に配置されたシード層22aと、シード層22aの上に配置された第1の導体回路23aと、第1の絶縁層21a及びシード層22aを貫通するビアホールの中に埋め込まれ、且つビアホールの底面に表出した第1の導体回路23aに接触する層間導通部24aとを備える。層間導通部24aと第1の導体回路23aとの親和性は、層間導通部24aとシード層22aとの親和性よりも高い。

(もっと読む)

配線板

【課題】内蔵する第1半導体素子と実装する第2半導体素子との距離を近づけ信号線の長さを短くすると共に、第2半導体素子を実装する際に信頼性が低下しない配線板を提供する。

【解決手段】絶縁層32に形成されるビア導体34と、層間樹脂絶縁層68に形成されるビア導体70とが、テーパの方向が逆であるので、該絶縁層32と該層間樹脂絶縁層68とで生じる反りの方向が逆となって、発生する応力を互いに打ち消し合う。このため、CPU90を実装する際のリフロー加熱、ヒートサイクル時の加熱・冷却によるメモリ42上の絶縁層32、層間樹脂絶縁層68の反りによるビア導体34とビア導体70との接続信頼性の低下を防ぐことができる。

(もっと読む)

161 - 180 / 1,540

[ Back to top ]